高扇出有哪些危害?

危害1:驱动能力下降,时序紧张

扇出过高也就是也就意味了负载电容过大,电路原理基础告诉咱们,负载电容越大,充放电速度越慢,电平跳变所需要的时间增加,即驱动能力下降,时序更加紧张。面对高扇出的情况,后端工具通常会通过插入buffer增加驱动能力,然后插入buff又会增加延时,造成时序紧张。

危害2:不利于布局布线,会增加走线延时

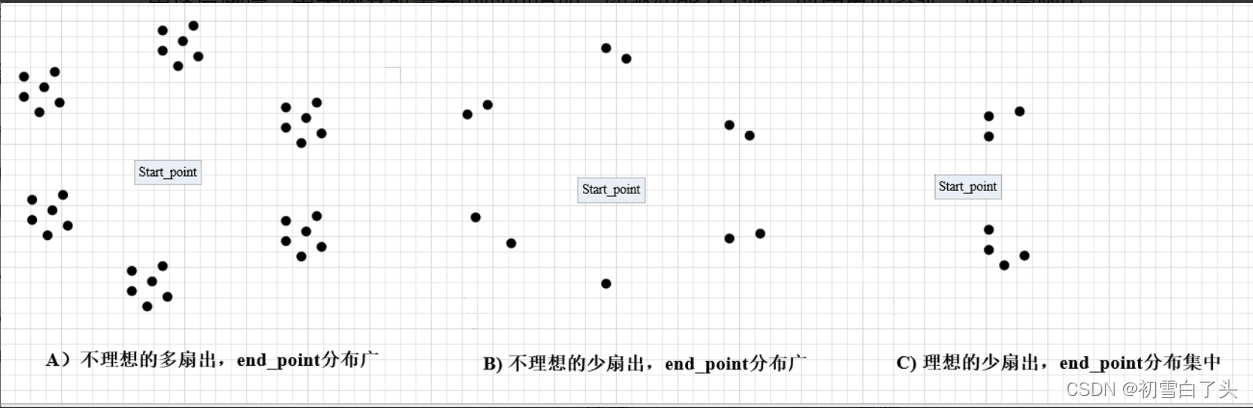

高扇出的情况通常意味着负载end_point分布在block的各个位置。而驱动的start_point需要放置在相对应的中心位置,这就意味到start_point到end_points的走线延时较大,一旦时序紧张,后端工具需要花费很多时间去优化,然而结果还不理想。

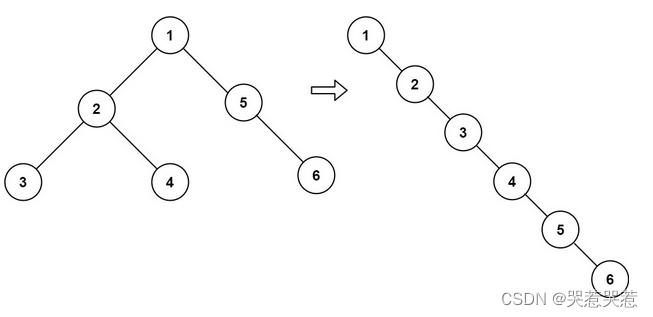

A图所示,扇出高并且end_point很分散,在高扇出情况中很常见,后端工具实现花费时间长,并且很难优化,走线延时比较大,时序比较紧张。

B图所示:扇出不高但是end_point很分散,后端工具实现花费时间教长,优化有难度,走线延时比较大,时序比较紧张。

C图所示, 扇出不高并且end_point集中,是理想情况,后端工具实现简单,走线延时比较小。

优化方法

1. 逻辑展开(Flatten Logic Structures)

逻辑复制是一种通过增加面积来改善时序条件的优化手段,最常使用的场合是调整信号的扇出。如果某个信号需要驱动后级很多单元,此时该信号的扇出非常大,那么为了增加这个信号的驱动能力,一种办法就是插入多级Buffer,虽然这样能增加驱动能力,但是也增加了这个信号的路径延时。为了避免这种情况,此时可以复制生成这个信号的逻辑,用多路同频同相的信号驱动后续电路,使平均到每路的扇出变低,这样不需要插入Buffer就能满足驱动能力增加的要求,从而节约该信号的路径延时。在大部分逻辑设计中,高扇出信号多为同步信号,即寄存器信号,所以进行逻辑复制时是对寄存器进行复制。由于高扇出信号会增加布局布线的难度,减缓布线速度,因此可以通过寄存器复制解决两个问题:减少扇出,缩短布线延时; 复制后每个寄存器可以驱动芯片的不同区域,有利于布局布线。

2. BUFG

通常BUFG是用于全局时钟的资源,可以解决信号因为高扇出产生的问题。但是其一般用于时钟或者复位之类扇出超级大的信号,此类信号涉及的逻辑遍布整个芯片,而BUFG可以从全局的角度优化布线。而且一块FPGA 芯片中BUFG资源也有限,在7k325tffg900上也仅有32个,如果用于普通信号的高扇出优化也不大现实。因此,在时钟上使用BUFG是必须的,但是如果设计中遇到某些复位信号因高扇出产生的时序问题时,可以在此信号上使用BUFG来优化。