TestBench使用

与quartus中testbench的写法有些许。或者说这是平台特有的特性!!

1 平台使用谨记

(1)必须删除:若设计为组合逻辑,需将自动生成的clk删除

若不删除,会提示运行超时错误。

(2)不可删除:平台自动给出的转存文件out.vcd所在的initial块不可删除

若删除,提示代码无法完成编译

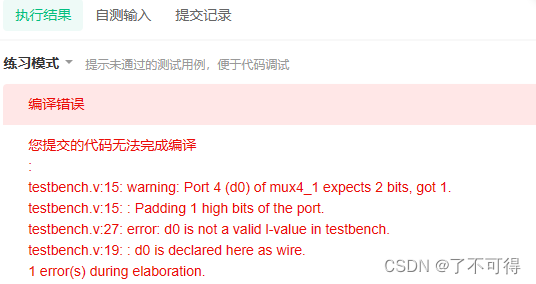

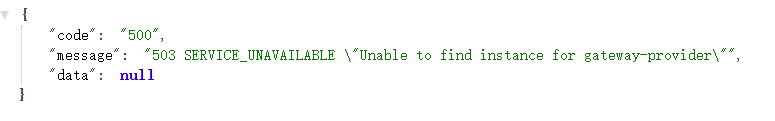

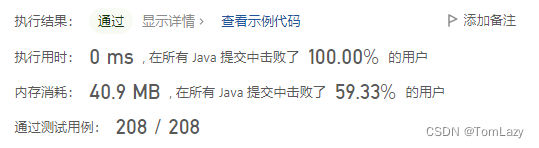

2 平台的[自测运行]可检测出代码的语法错误

如在VL1_四选一多选器中,就给我检测出了如下错误

原因是我代码中的一个变量未声明/或者说是声明错误了。其中d4在代码中是用不到的,代码中需要的是d0,我确没有声明

//input signals

reg [1:0] d1,d2,d3,d4,sel;

//output signals

wire [1:0] mux_out;

//例化

mux4_1 t_mux4_1(

.d1(d1),

.d2(d2),

.d3(d3),

.d0(d0),

.sel(sel),

.mux_out(mux_out)

);

//input signals initialize

initial begin

#10

d0 = 3;

d1 = 0;

d2 = 1;

d3 = 2;

sel = 2'b00;

end

3 仿真时间尽量小

因为网页显示的编译结果显示不太方便。

所以只要能够验证功能的正确性即可。

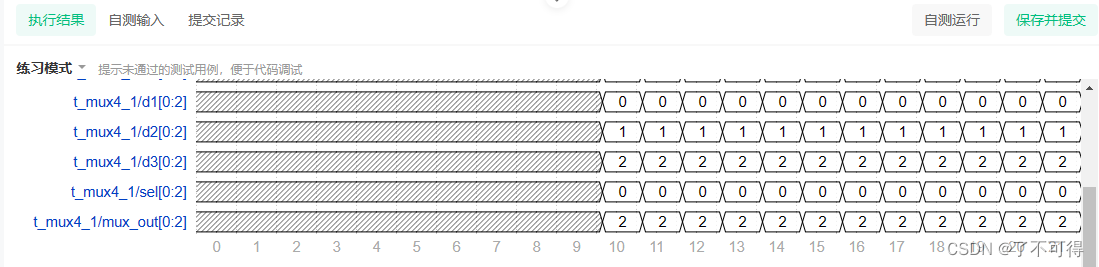

4 得到仿真结果

5 TestBench中模块的另一种例化方式

// mux4_1 t_mux4_1(

// .d1(d1),

// .d2(d2),

// .d3(d3),

// .d0(d0),

// .sel(sel),

// .mux_out(mux_out)

// );

//另一种例化方法

mux4_1 u_mux4_1(d1,d2,d3,d0,sel,mux_out);

6 完整的TestBench文件

`timescale 1ns/1ns

module testbench();

// reg clk=0;

// always #5 clk = ~clk; // Create clock with period=10

// A testbench

//input signals

reg [1:0] d1,d2,d3,d0,sel;

//output signals

wire [1:0] mux_out;

//例化

// mux4_1 t_mux4_1(

// .d1(d1),

// .d2(d2),

// .d3(d3),

// .d0(d0),

// .sel(sel),

// .mux_out(mux_out)

// );

//另一种例化方法

mux4_1 u_mux4_1(d1,d2,d3,d0,sel,mux_out);

//input signals initialize

initial begin

#10

d0 = 3;

d1 = 0;

d2 = 1;

d3 = 2;

sel = 2'b00;

end

initial fork

#20 sel = 0;

#40 sel = 1;

#60 sel = 2;

#80 sel = 3;

join

//end

initial begin

$dumpfile("out.vcd");

// This will dump all signal, which may not be useful

//$dumpvars;

// dumping only this module

//$dumpvars(1, testbench);

// dumping only these variable

// the first number (level) is actually useless

$dumpvars(0, testbench);

end

endmodule

6 吐槽

为什么保存并提交之后,平台不保存我的testbench测试平台文件,生气气!!!

![[曾经沧海难为水]两数求和](https://img-blog.csdnimg.cn/img_convert/694de670f35d2adebf111c7f32fae7c1.png)