周斌老师

课程链接:

目录

- 第一课

- 内容

- 生态环境

- 第一课 CPU体系架构的概述

- 什么是CPU

- 指令

- 存储器架构

- CPU内部的并行性

第一课

预修课程:

Cuda c programming guide

参考内容 1,2,3查找一下。

内容

CPU体系架构概述

并行程序设计概述

CUDA开发环境搭建和工具配置

GPU体系架构概述

GPU编程模型

CUDA编程

CUDA程序分析和调试工具

基本优化

深入优化

最新NVIDIA GPU和CUDA特性

生态环境

nvidia cuda zone

QQ群:

GPU深度开发==》还没有加,记得去加群

多核系统和并行系统,是因为我们的单频系统性能遇到了瓶颈。

第一课 CPU体系架构的概述

什么是CPU

执行指令,处理数据的器件

- 能够完成基本的逻辑和算术指令

指令

算术

访存

控制

这三类指令组成了一个计算机程序。

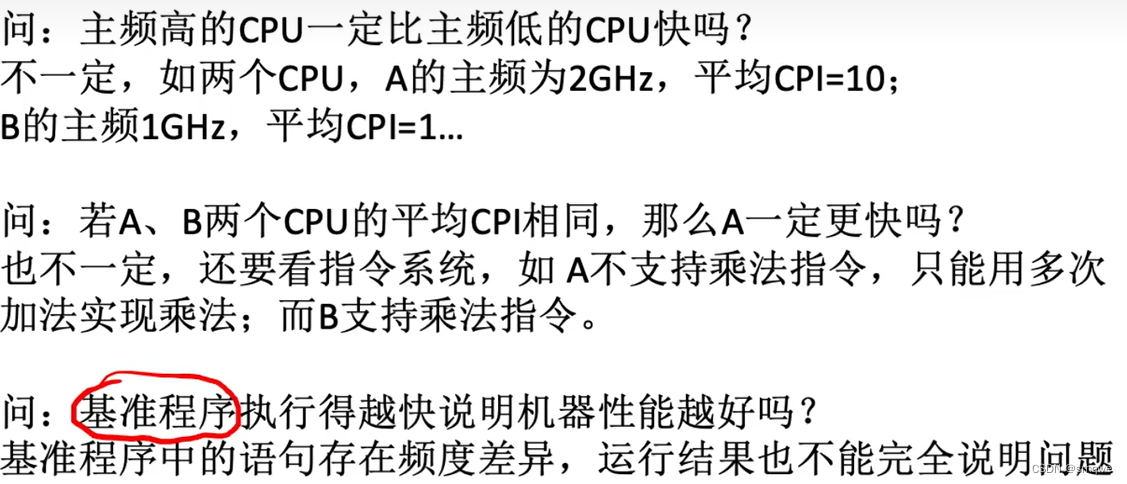

优化的目标:

每天指令需要的时钟周期最少

时钟周期尽量短

程序指令占比:

分支:12.5%

访存:46%

矢量运算:0.2%

CPU结构图:

芯片做计算

内存接口,接内存到CPU上

外部接口:显示系统的接口、多媒体的接口

桥接芯片接口==》硬盘、南桥北桥、

摩尔定律

芯片的集成密度每2年翻一番,成本下降一半。

28nm,芯片加工到了极限。

所以,摩尔定律表现不那么理想了。

百亿的量级的晶体管,这些晶体管都在干什么?

22亿个晶体管,8和芯片

中间最大的部分是三级缓存。

CPU是一个吞吐机,是一个处理机,不断把数据倒来倒去,花费在存储仓库花费在路上的成本最大。

简单的CPU结构图

上面部分数据通道

下面是控制逻辑

流水线

利用指令级并行

- 极大的减小时间周期

增加一些延迟和芯片面积

会带来的问题:

具有依赖关系的指令怎么办?

分支应当处理?

流水线的长度:

- core 2 14级

- pentium 4 > 20级

- Sandy Bridge 14到20级之间

旁路Bypassing

add R1,R7需要用到sub R2,R3指令的结果,可以加一个旁路,这样就不用访问内存,直接获取R7的结果。

停滞Stalls

load [R3]->R7

add R1,R7->r2

add指令需要等待load指令完成

分支 Branches

分支预测Branch Prediction

基于过去的分支记录

分支断定

提升IPC

超标量

峰值N

增加了面积

- N倍资源使用

- 旁路网络N

Sandy Bridge超标量

指令调度Scheduling

寄存器重命名

乱序执行

把指令重新排一下,做一个优化

存储器架构

越大越慢

缓存Caching

将数据放在尽可能接近的位置

利用:

时间的邻近性

空间的邻近性

缓存层次

存储器的另外的设计考虑

分区==》避免多端口

一致性Coherency

控制器Memory controller==>

CPU内部的并行性

向量运算

相同处理的数据同时去做

数据级并行

单指令多数据

X86的向量运算

线程级的并行

多核Multicore

锁、一致性和同一性

CPU遇到了现实的困境,我们称为能量墙,cpu主频提升导致功耗很强度的提升,功耗的提升导致功耗的面积、集成度、成本不能无限增加。

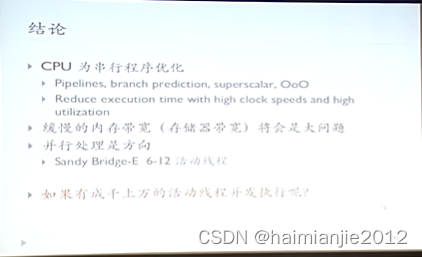

结论

![[busybox] busybox生成一个最精简rootfs(下)](https://img-blog.csdnimg.cn/5332d8e0aa0a4c6995299ee449494438.png)