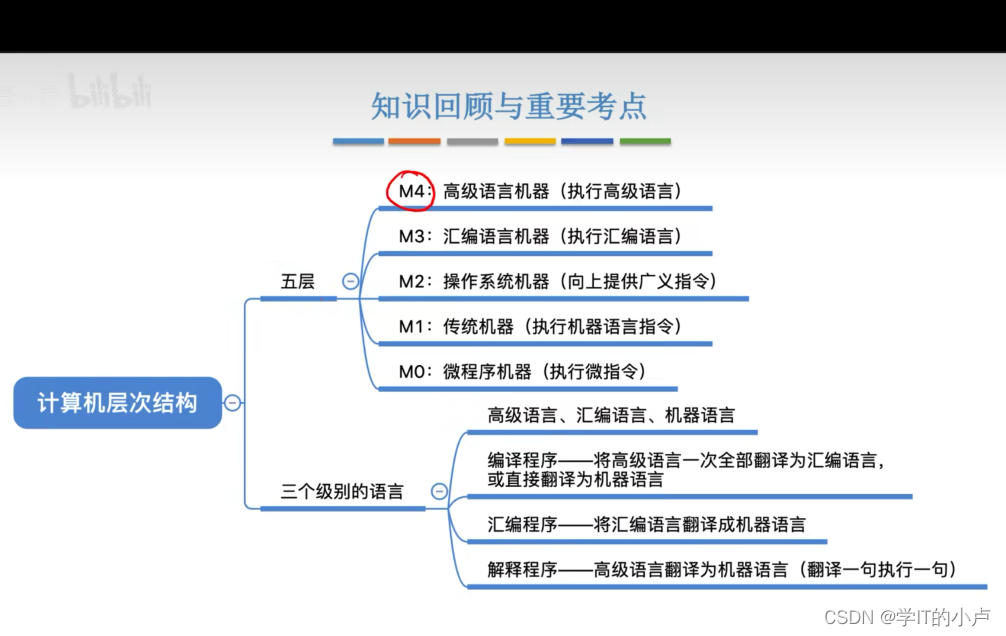

页和段的区别

页式,一个程序的各页是根据你的程序空间连续编址的,程序地址空间只有一维;

而段式,一个程序拆分成各段,独立编址(各段都从零开始编址),程序地址空间有两维。

例如一个50KB的程序,页式分配,不妨设每页4KB,各页地址分别为0~4,4~8 ...... 44~48;

而段式分配,各段地址则可能是0~20,0~20,0~10

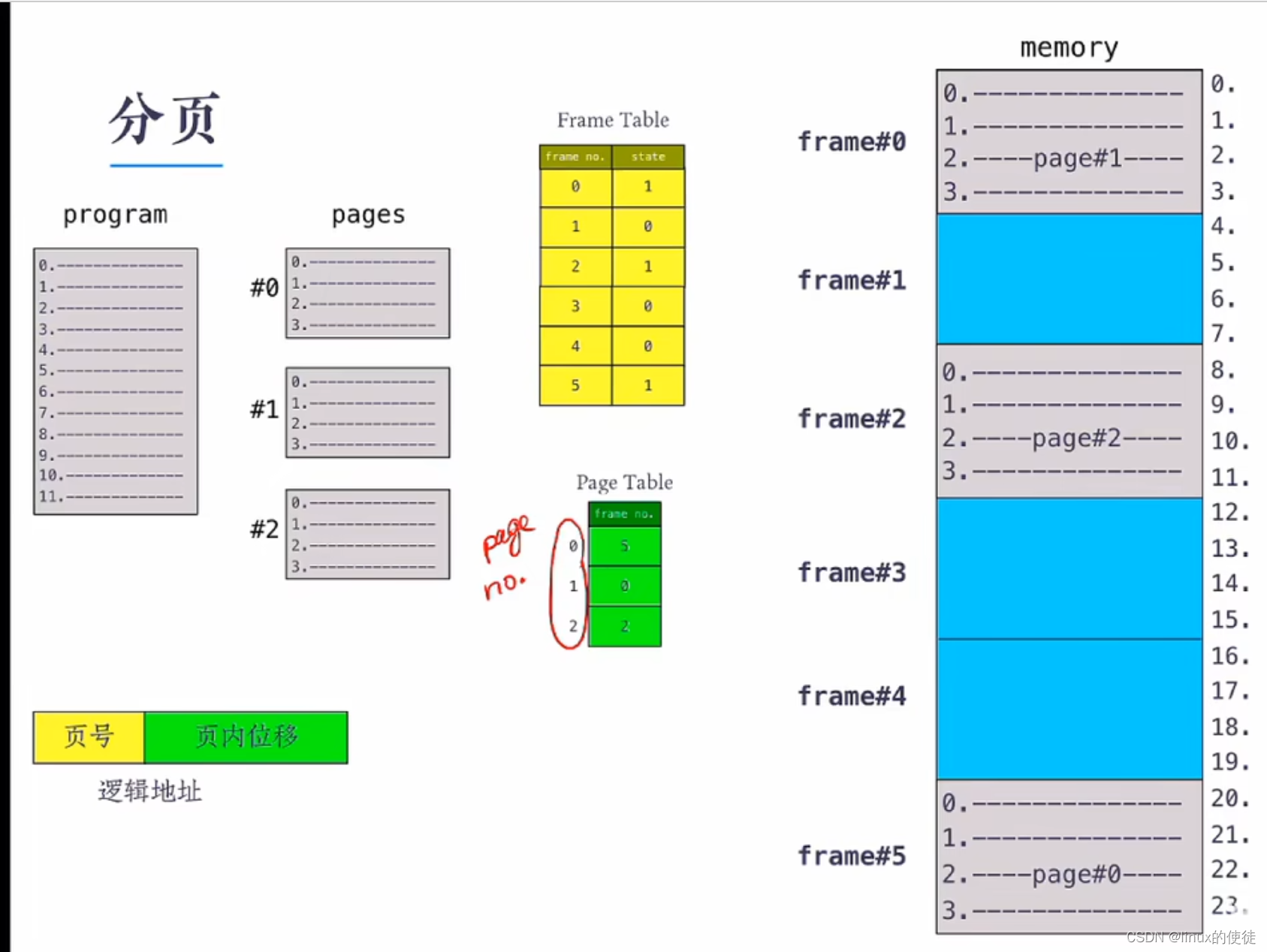

对于page table我们可以优化,用下标代替页号,只保留frame no

我们来算一个我的操作系统的页的m和n

1.可以看到我的操作系统是64位 也就是m为64

2.可以看到我的操作系统默认的page size是4K那么4k等于2^2*2^10=2^12,那么n就等于12

页表的优缺点

块表

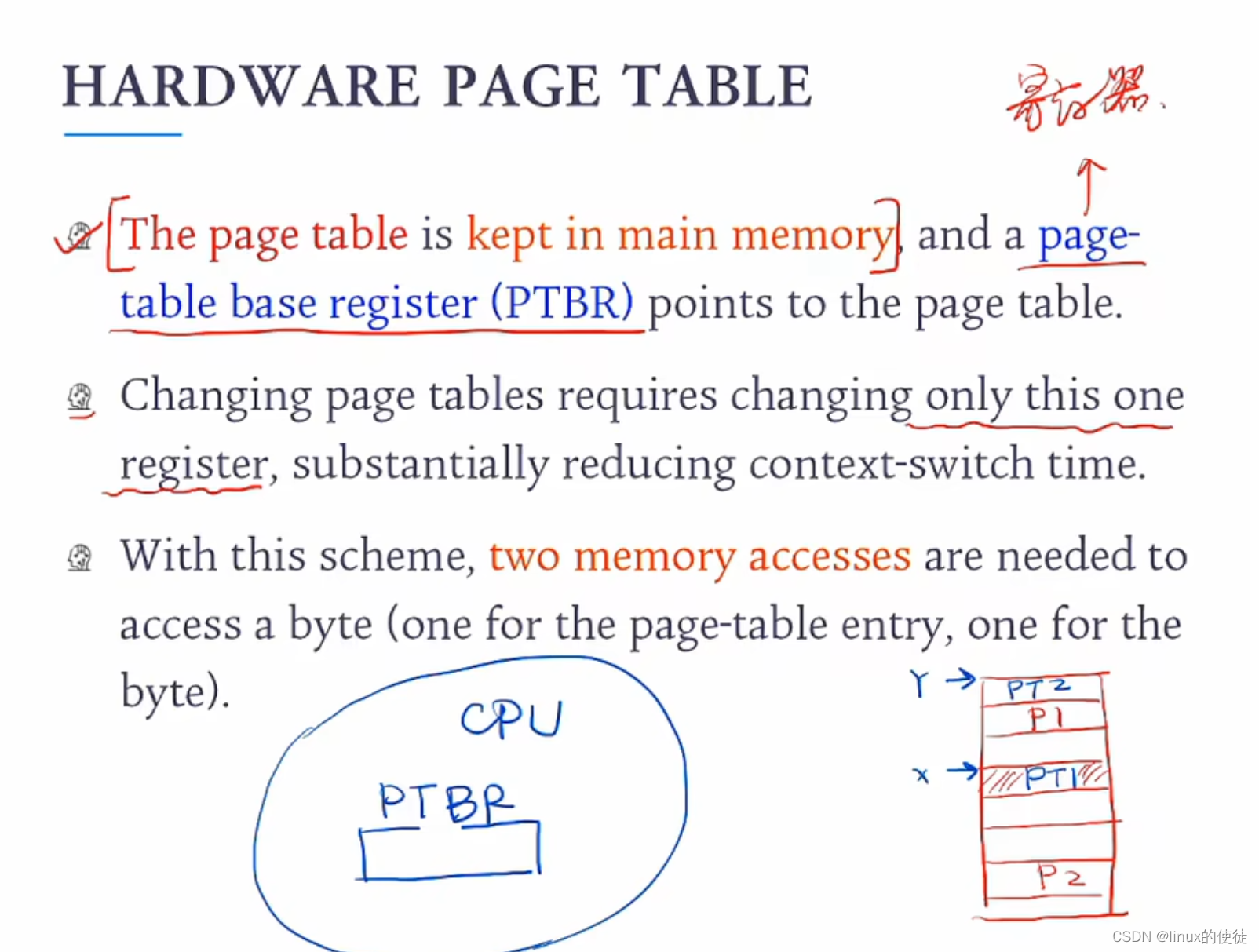

硬件页表

页表也是放在内存中的

我们读取对应的寄存器PTBR的值,page-table base register(PTBR)指向页表

我们每次转化物理地址都需要访问主存访问,第一次访问对应的页表(页表是在内存中的),第二次才根据页表定位到页号。

TLB(Translation look-aside Buffer)这里不翻译,翻译太多了大家理解英文就行

是一种专用的页表缓存,能非常快的查找

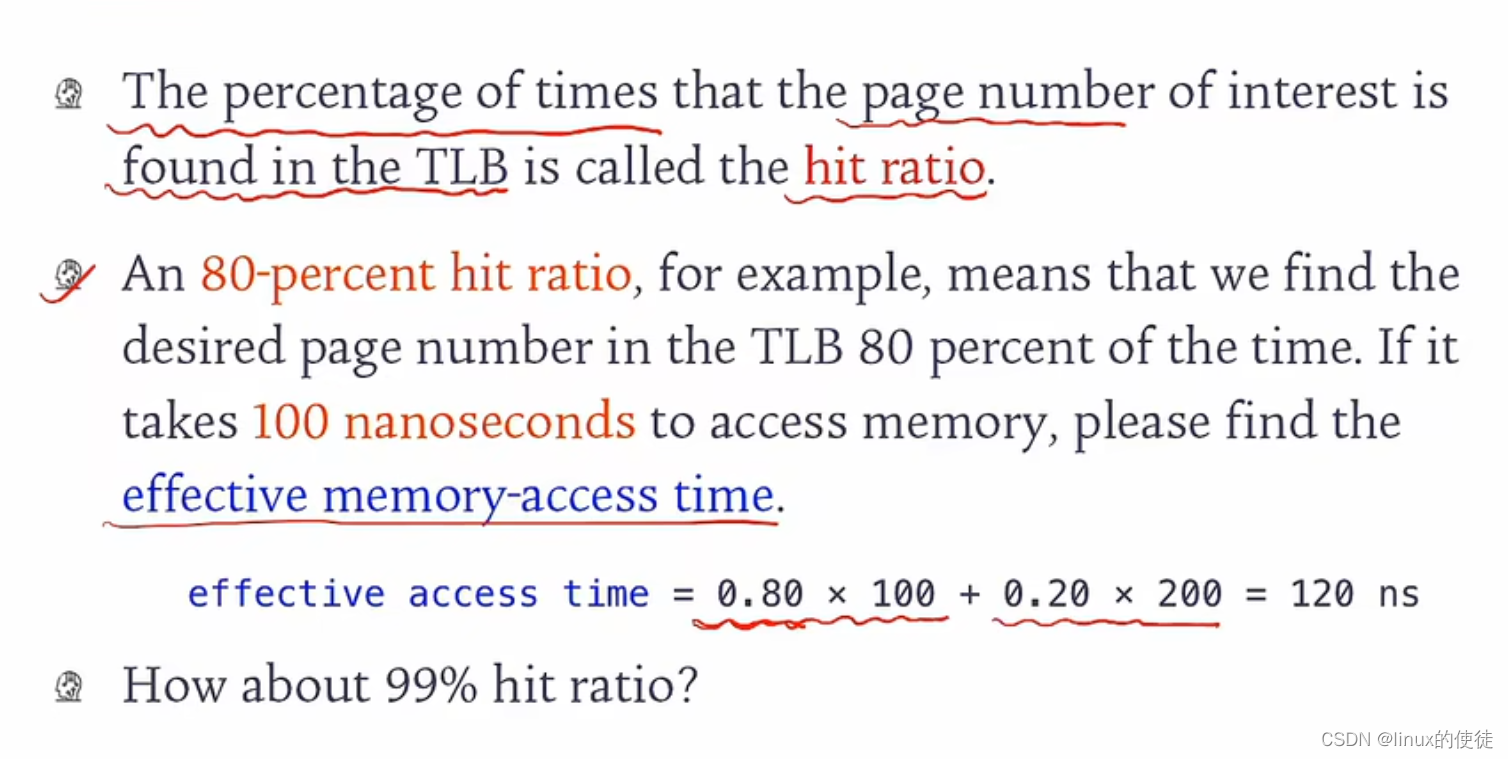

学过计算机组成原理,我们都知道cache的优劣完全由命中率决定

原理都是命中即直接取cache值,未命中就去内存中的page-table中查找,这里如果要提高命中率就需要把程序常用的表录入TLB。

访问流程

命中直接防

命中率分析

百分之八十命中率(命中只需要访问一次内存),未命中就访问两次内存

百分之九十九命中率

0.99 * 100 + 0.01 * 200 = 99 + 2= 101 ns

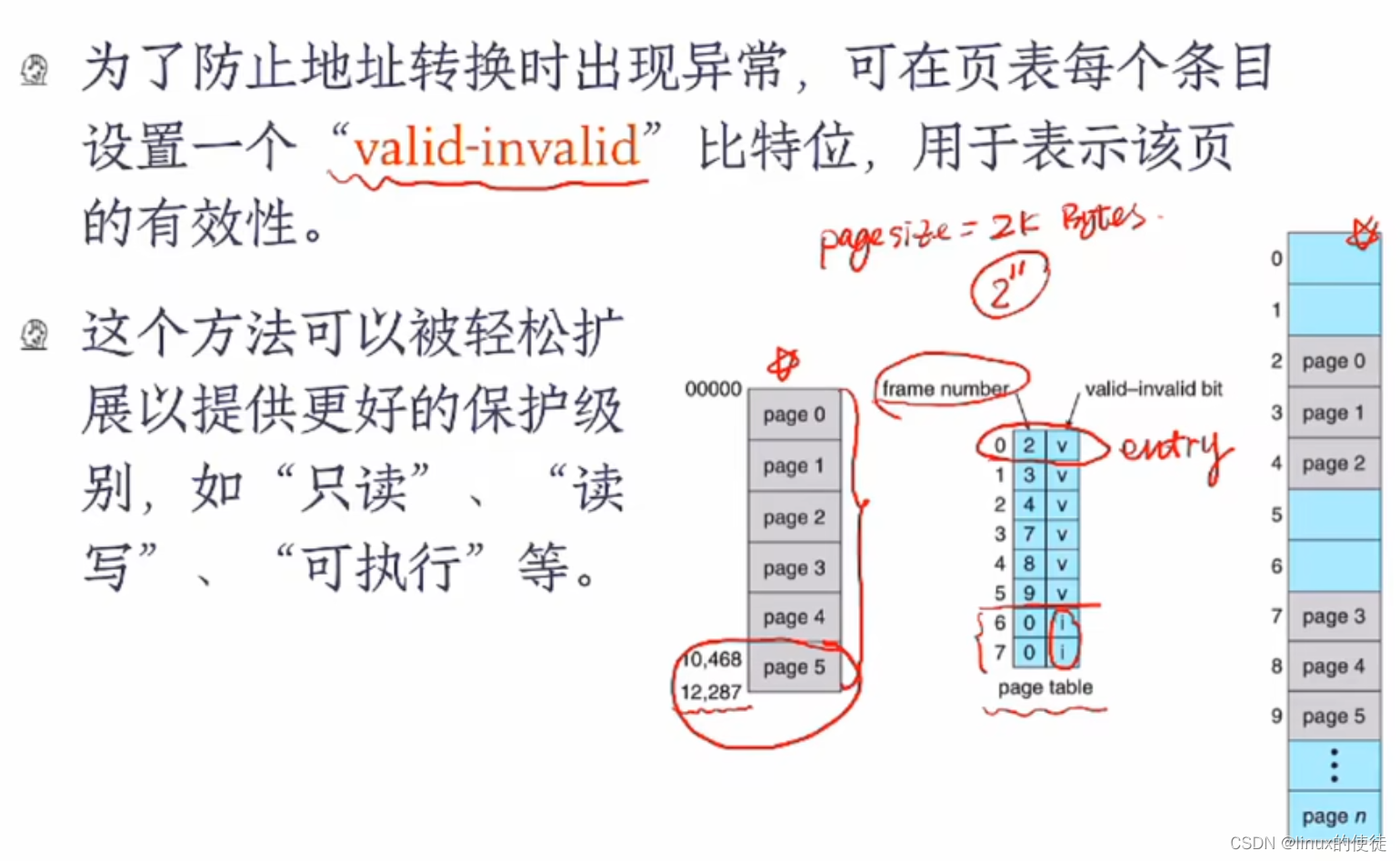

保护机制

操作系统基本单位为2KB

整个虚拟地址大小为12287,分页可以得到12287B/2048B左取值得到5,也就是只能分五页,五页离散放入内存中,page-table页只要0-5的下标里有对应的frame number且valid-invalid bit值有效。而剩下两个下标对应valid-invalid bit值无效,代表frame number无效,如果取到报越界错误。

这个valid-invalid bit可是是bits,因为有些页可能是只读,也能是读写,所以可以添加更多有效位去代表更多属性,但这个是要消耗资源的,所以需要权衡利弊。

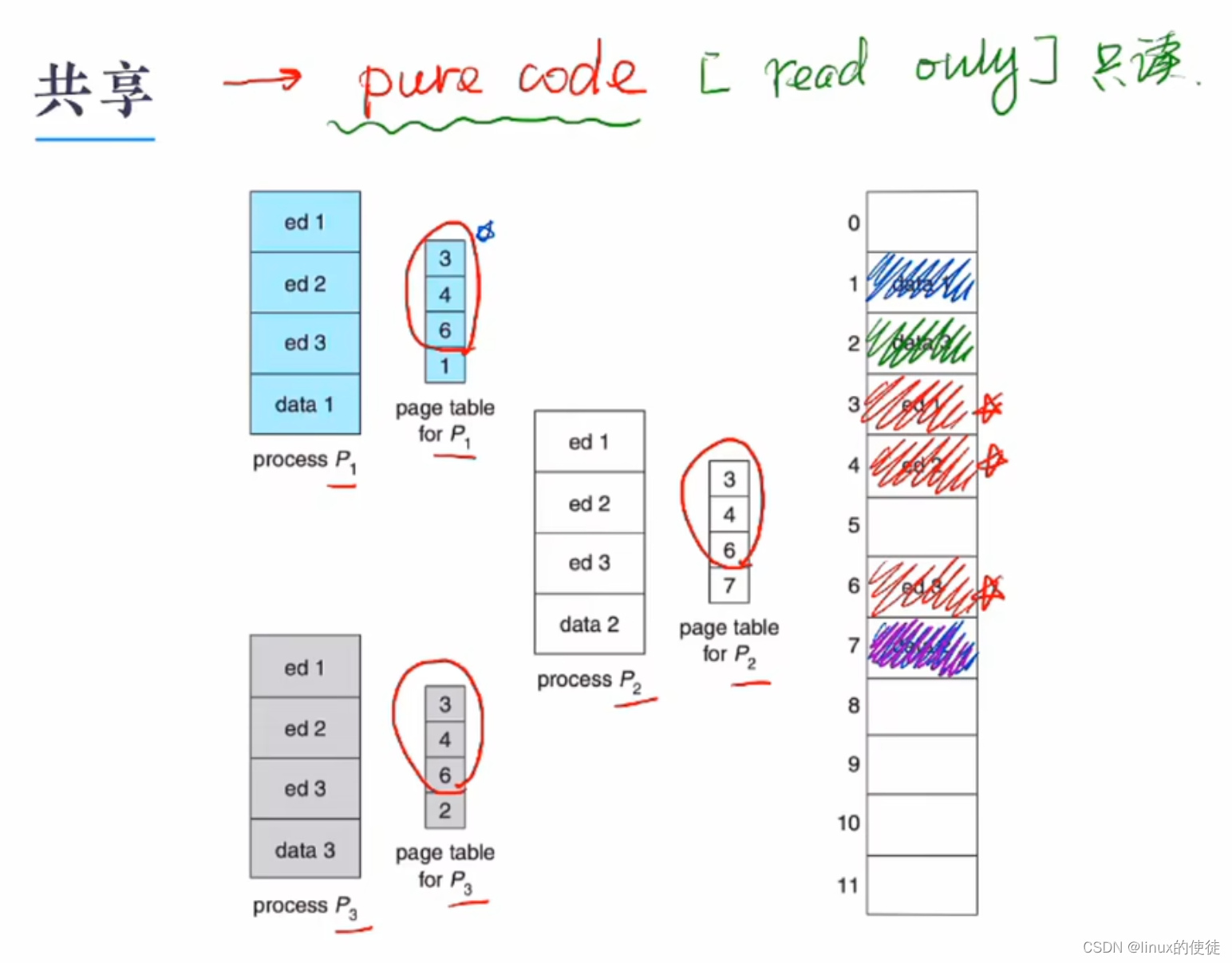

共享

这里有个pure code概念,前面我们说了有些页的内容是只读或读写,这个code可以让很多人读取,但是如果要是多人写入那么会出很多问题,所以一般是只读

但是页表也是存入内存中的,那么如果页表过大,我们如何解决页表连续的问题

我们引入一个问题

每个进程都有页表

这只是一个进程的表可能就要达到4MB,所以我们还是需要将表拆分,离散存储。

我们根据上面的问题发现,如果表离散存储有需要一个记录离散表的东西

页目录(page of page-table)

上面这个叫做两级页表,而我们举例的是32位的,64位就需要更多级

x86-64位架构的机器用的是四级的页表

![③【Java 组】蓝桥杯省赛真题 [黄金连分数][马虎的算式]持续更新中...](https://img-blog.csdnimg.cn/20a7f1b58dfb4660b75d7f021c157d57.png#pic_center)