https://www.eet-china.com/news/magazine220608.html

555时基的迷人历史和先天缺陷!

发布于2022-06-16 03:39:12 LARRY STABILE

流行数十年的555时基,业内不知晓的工程师应该寥寥无几!几乎所有的数字电路教材中,都有该芯片的身影,要说是无所不在一点也不过分。然而,该电路却存在显著的输出级电流浪涌的先天设计缺陷。原设计师曾设法进行改进,来修复缺陷,但最终都未能实现,他的意志已被强大的市场力量所湮灭!

故事从一台电源开始。这是Southwest Technology Products Corporation生产的型号为143D的 2A台式电源。该电源是在很多年前创建工具包时作为一个工具配套的。尽管其外观不太好看,但多年来,在各种项目中使用一直很好。

尽管NE555时基很受欢迎,但我从未使用过。最近为了做一些实验,考虑到有时候可能会需要使用振荡器,我便买了几片,因为对于设计振荡器而言,这似乎是一种最简单的方法。

然而,当试用时,用的还是旧的但完好的143D电源,我惊讶地发现,电源供电失控,过电流甚至将电流表卡住,等等。该电源看来很皮实,并没有被烧掉。我本想搞清楚什么原因,但当时我正在做其他一些电路工作,所以先把元器件放在了一边。

缺陷的发现

最近,我又有了一台型号为Siglent SPD303X的新电源。我决定再次尝试一下NE555,虽然这次没有让电源瘫痪,但我发现了更多事关一个臭名昭著的问题。

事关这个问题有较全的记录。一开始我不知道该怎么做,因为这似乎是555的一个严重设计缺陷:图腾式输出,分别直接连接到正压轨和接地,没有任何类型的限流或特殊的开关定时,允许两个晶体管简单地导通,吸收大电流。我从事过许多设计工作,利用过的元器件包括TTL、各种类型的分立晶体管、运算放大器、各种更复杂的芯片,甚至还有继电器,即使是使用我的旧电源时,也从未遇到过如此严重的浪涌。

实际上,许多人对此进行过跟踪,并清楚描述了这个问题。典型的报告是电流峰值持续100-200纳秒,拉电流约为300毫安。这是芯片正常空载电流的10倍多。在没有去耦电容器的情况下,电源电压会下降一大半。我的情况也不例外;Siglent SPD3303X电源的功能非常好,可以看到这类压降。

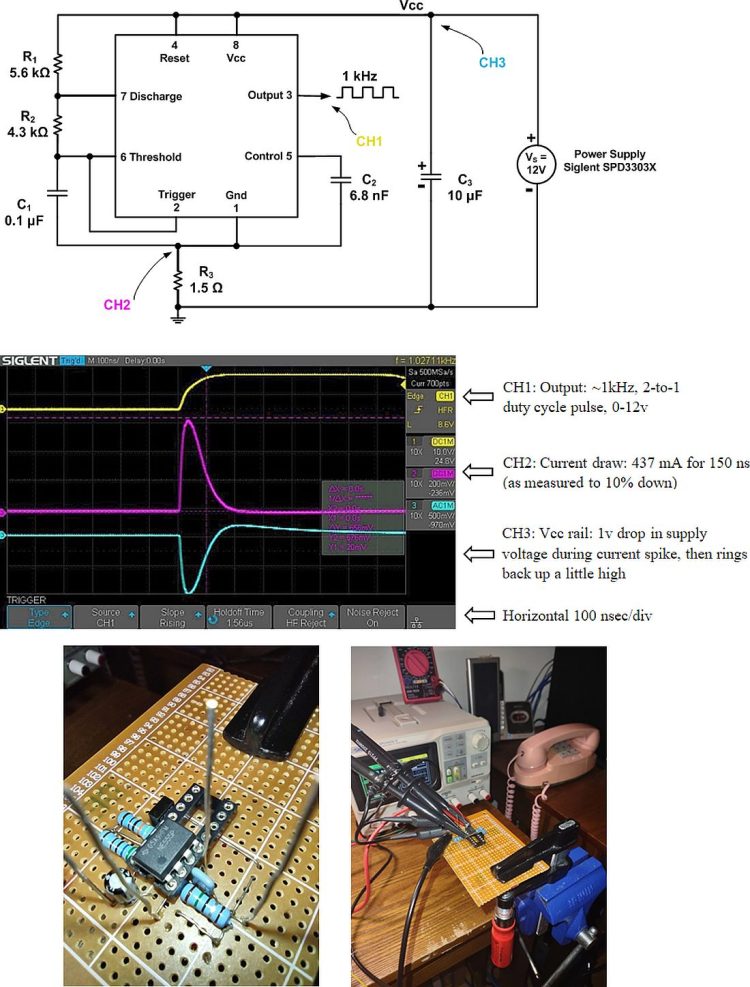

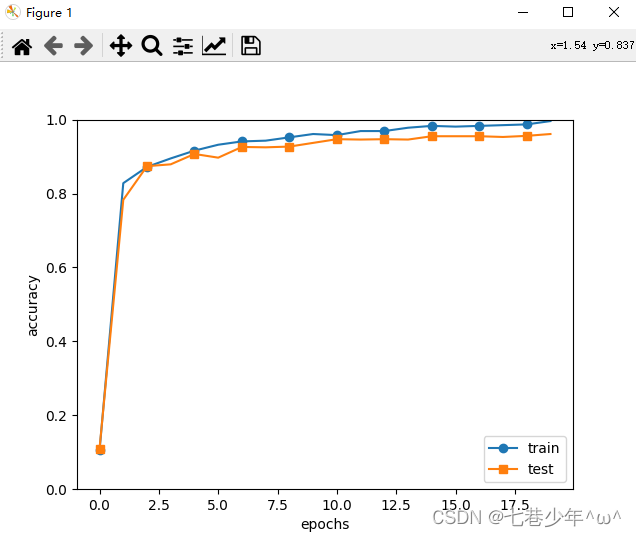

我也做了一些实验,实验如图1所示。紧凑的布局,产生的信号相当纯净。除电源外,示意图中所示的所有组件都位于电路板上。峰值吸收电流相当大,高达437 mA,这与其他报告相符。

图1:NE555测试:原理图、示波器迹线及电路板布局。

我最近的其他一些实验也包括三个频率可能非常接近、独立可调的自由振荡器。为了避免电流浪涌在定时器之间传播寄生同步信号,选用了合适的电阻和电解电容对每个芯片上的电源进行了严格的滤波。虽然这降低了可用电源电压,但也足以驱动下游组件。不过遗憾的是,为了弥补这个问题,需要添加的元器件比功能实际需要的要多。

NE555历史

但更重要的是,随着研究的深入,我发现这款芯片有着迷人的历史。

NE555于1972年由Signetics发布,是Hans Camenzind在之前的两年左右时间里设计的产品。在当年Jack Ward对Camenzind的采访中,他讲述了完成设计的尝试、与雇主的问题(他最终根据合同完成了设计,这在当时非常罕见),以及Signetics的营销经理Art Fury在市场上成功推广该产品方面的勇气和信念。

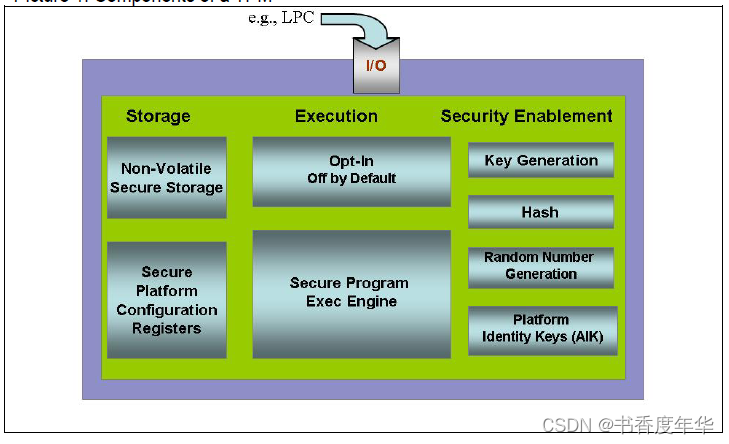

Camenzind在采访中谈到该设计的内部评审。当然,输出级是一个重要的地方。当时类似的集成电路,如TTL门,试图使用限流电阻器、二极管和定时来降低功率峰值。但NE555的目标之一是,它应该能够驱动相当大的负载。因此,让图腾柱输出分别直接连接到Vcc和地的决定可能是有意的。

虽然不清楚电源尖峰问题是什么时候被发现的,但Camenzind很早就意识到最初的设计存在缺陷。他在1997年发表在IEEE Spectrum上的文章《Redesigning the old 555》以及随后在他的《Designing Analog Chips》(2005)一书中对第2版555的描述,都同时列举了缺陷以及改进方案,包括采用更好的偏置电路,以降低对电源变化的敏感性,并扩大电源电压范围;在比较器上添加平衡的有源负载,以提高精度和速度;还有采用一种新型小电流的电流模式触发器,以减小开关时间。改进的主要总体目标是减小工作电流和降低所需的电源电压;这些对输出级也都有重大影响。

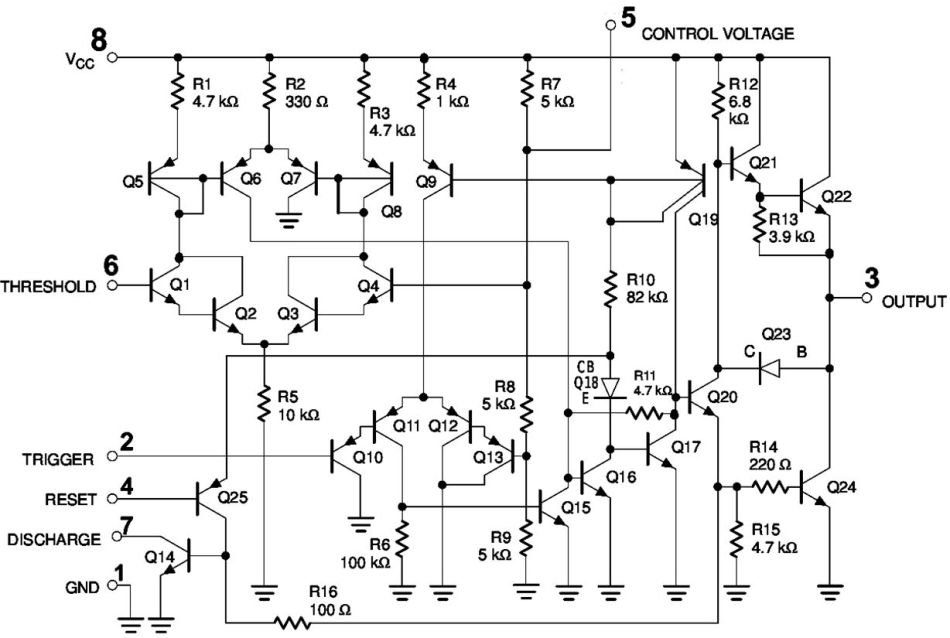

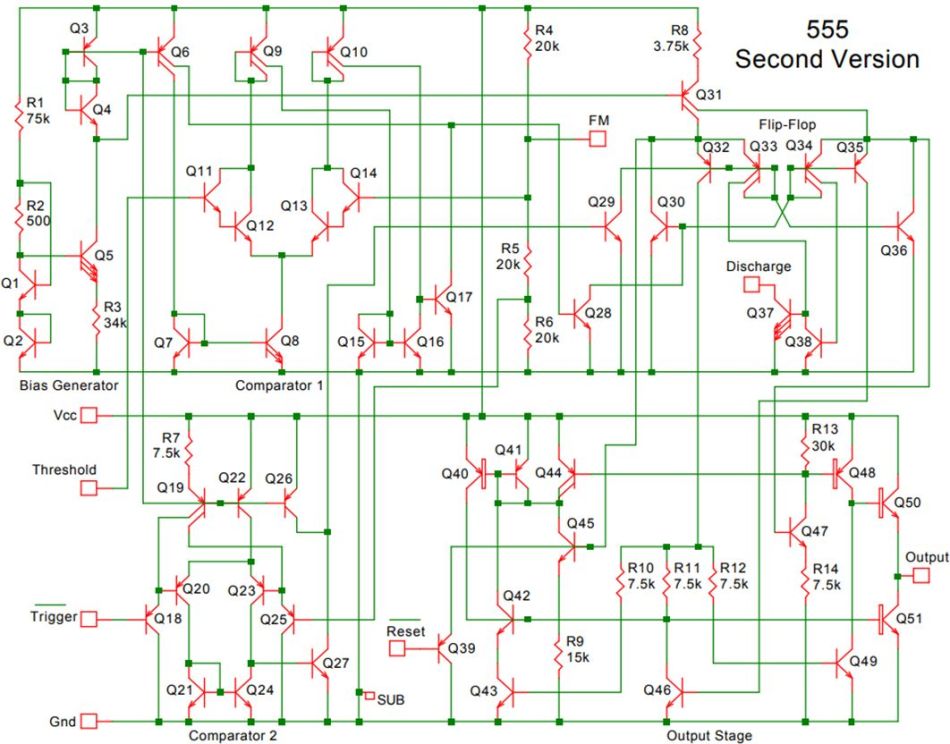

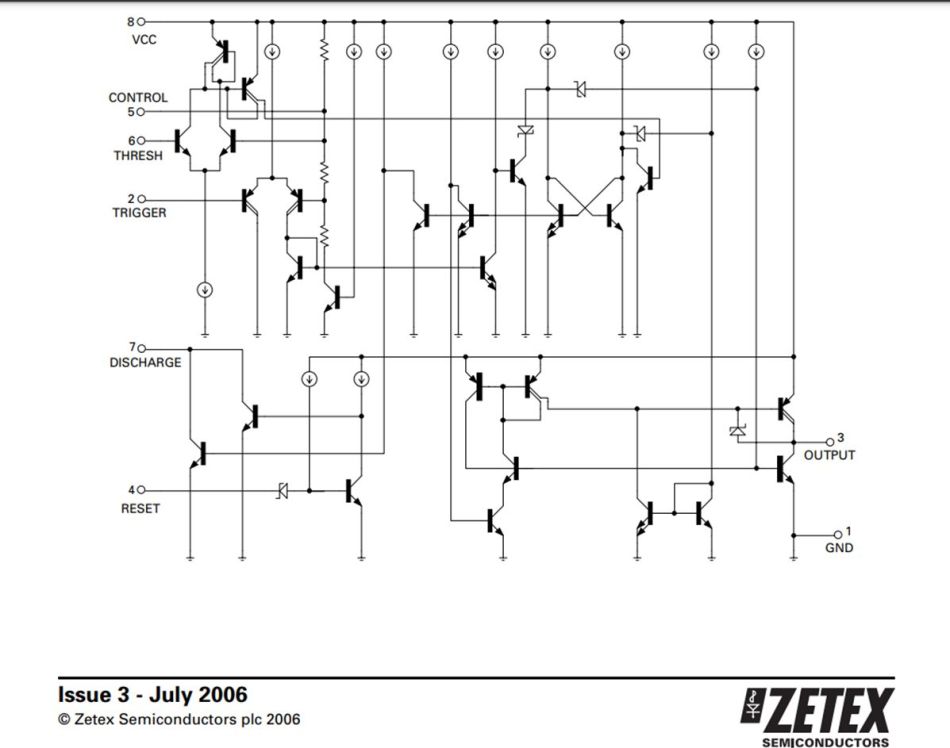

上述所有三个部分的示意图如图2-4所示。请注意,后来的设计利用了当时可实现的更高设计密度。

输出级是上述文章和书中的一个突出主题。Camenzind甚至在书中说,“最重要的变化是输出级”。第一篇文章中还提到Zetex ZSCT1555作为555的重新设计,并遵循了文章中描述的概念。然而,在后来的《Designing Analog Chips》一书中,并不清楚输出电流要求是否已经确定:Camenzind提到了原555的电流源和大灌电流问题,并展示了第2版555的图腾式输出,但没有明确说明新款芯片的输出电流要求。他确实描述了控制电流和定时的各种改善,因此他声称电流浪涌已经消除。

而另一方面,ZSCT1555的设计确实反映了第一篇文章中描述的大部分内容。文章和书中以及第2版的555都使用了“Widlar Latch”正反馈回路。在第2版的555中,该电路由Q40、Q41和Q42组成。ZSCT1555显然面向低功耗和低电压应用。请注意,最低电源电压是降低了,但输出电流指标不对称:其灌电流是NE555的一半,达到100 mA,但反向吐电流只能达到150µA,最高速度也低于NE555。在高压侧使用PNP集电极驱动输出晶体管适用于低电流高压,Camenzind在第一篇文章中明确提到所支持的大电流指的仅是灌电流。然而,由于高压侧吸收电流不大,可见这将会消除电流浪涌。

尽管Camenzind写得很清楚,而且毫不掩饰地公开,但市场上供应的产品还是最初的原555设计。CMOS版本似乎填补了一些低功耗的市场缺口,但生产“更好”的双极555的努力都一直屈服于原始版本的压倒性力量。

图2:最初的555定时器。资料来源:Signetics Analog Applications Manual

图3:Hans Camenzind的第2版555。资料来源:Designing Analog Chips

图4:555的低功率版且引脚兼容的Zetex ZSCT1555。资料来源:Zetex

发明者意志VS市场力量

遗憾的是,直到如今,也就是说在原555发布50年后,也是原设计师Camenzind已经离开我们10年后,第2版的555也未生产,且ZSCT1555亦已经停产,而有设计缺陷的NE555却仍在广泛使用!据报道,它的销量大到无法统计,它是历史上最受欢迎的芯片!

我可以想象得出来,工程师离开办公室后,对修复设计缺陷的那种强烈欲望,这既是工程师的美德,也是魔咒!Camenzind显然是一位优秀的设计师,不仅非常有创意,而且非常有纪律,在设计中投入了大量的前沿思想,但原555的设计缺陷一定让他感到困扰。在采访中,他说对555的改进没有流行起来感到“震惊”。看来,他的创造物已经不再服从他的意志,原创者也无能为力了!

相信我们都能想到类似的例子,尽管程度可能不及Camenzind的案例那么重要。这足以说明:任何设计都必须“三思而后行……”!如果失败了,会沮丧一阵,然后再试一次,两次,三次…… 但如果成功了,欣喜之余必须记住,“把放出去的野马重新弄回马厩可能更困难”!

(参考原文:The NE555 current spike )

本文为《电子工程专辑》2022年6月刊杂志文章,版权所有,禁止转载。点击申请免费杂志订

责编:Jimmy.zhang

![[Css]Grid属性简单陈列(适合开发时有基础的快速过一眼)](https://img-blog.csdnimg.cn/9d338deb4497486c91cdb94f242c0401.png)