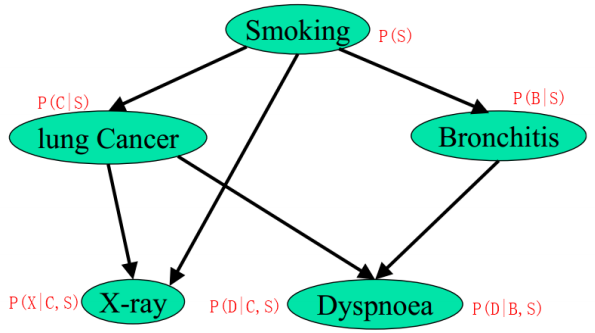

88E6352应用

网关

车载信息娱乐

车身域控制器

PTP

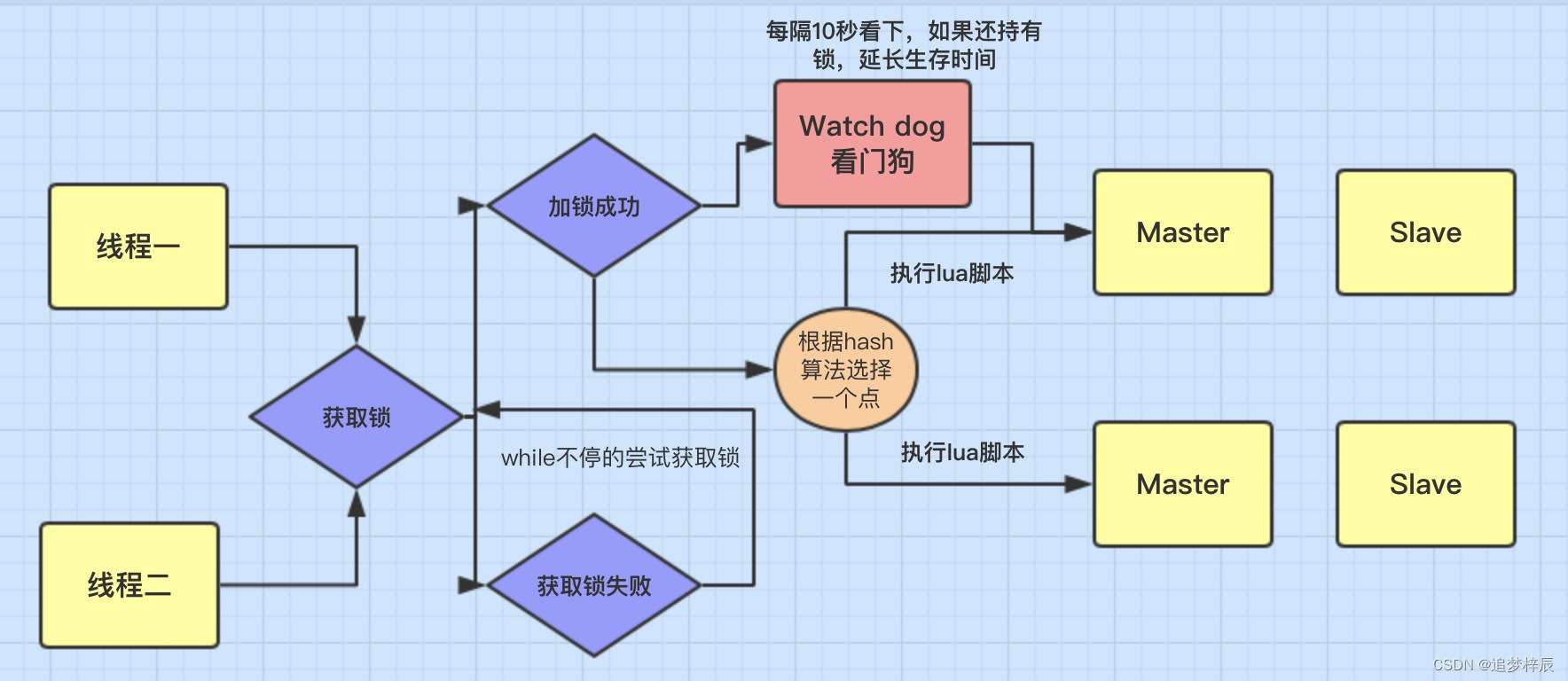

PTP通过周期型地交换控制包实现

- 选择其中网络最佳质量时钟元素,作为PTP网络中Grand Master.没有Grand Master 节点变成PTP slave节点。

- PTP节点从Grand Master节点获得他们驱动频率和时间信息。

基本观念是PTP帧的时间戳经可能接近物理线束。

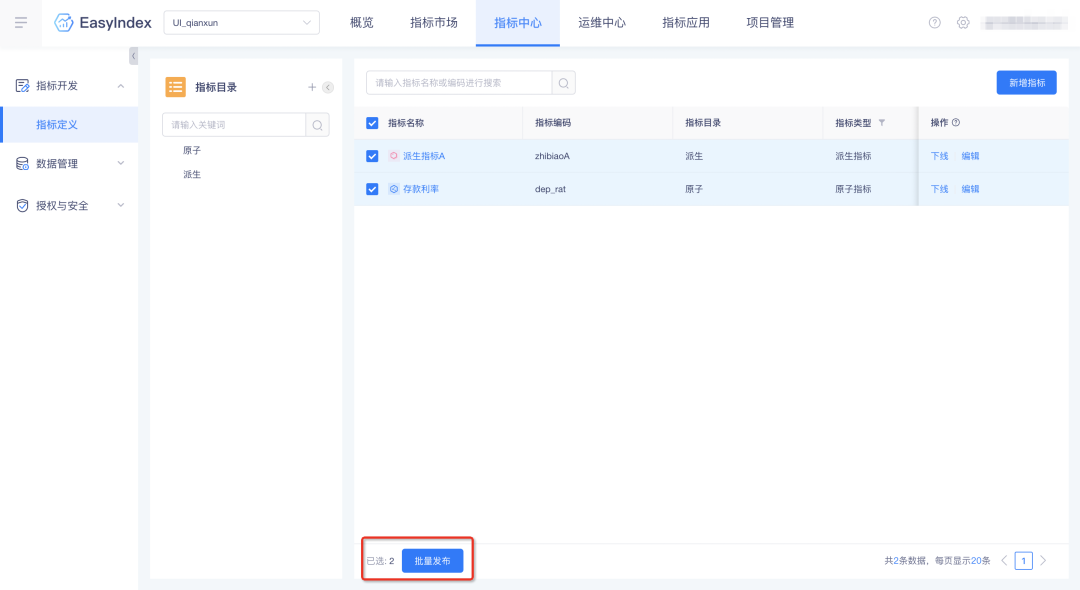

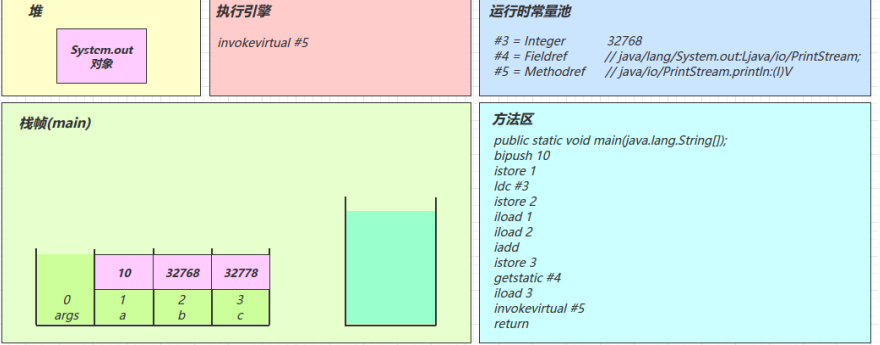

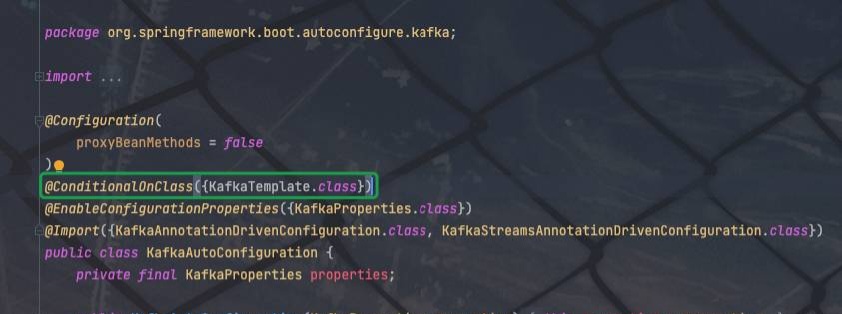

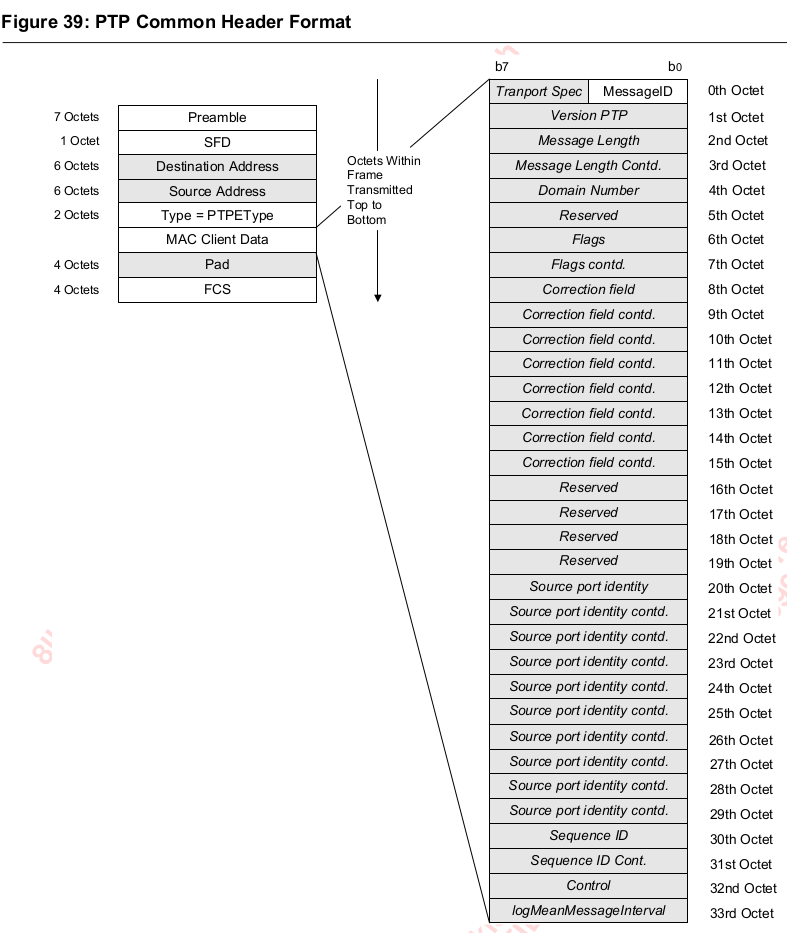

为了支持PTP协议,设备从包和识别到指定转发给CPU的PTP消息中,编码EtherType/Sub-type场。设备的802.1AS控制帧时间戳从离开的节点到被给的节点。设备支持全灵活的配置16种PTP帧类型时间戳在使用MsgldTSEn(PTP全局寄存器偏移0x1)。PTP帧类型通过Msgld场描述,如下。

ptp帧结构

PTP通讯

PTP核基于EtherType和Sub-type场回应帧,确定帧的时间戳信息是否可用。在PTPcore中,注意 帧事件消息帧可以获得时间戳。设备支持两个到达计数和一个离开计数器。确保更多的到达事件在硬件上能够步骤。例如,从Grand Master发出同步帧PDelayReq或者PDelayResponse消息能够同时达到被给Slave节点。

switch交换机数据管道 识别和接收到组播目标地址的使用,会通过PTP帧和转发它到CPU_DEST(Global offset 0x1A)。在接收的PTP帧在修订时,发送CPU_DEST需加一个To_CPU DSA标识。设备支持two-step PTP时钟,其中紧接着的一个消息通过软件节点定时被发出。

当PTPArrIntEn(PTP Global Config register 0x03)设置在0x1,一个通过硬件生成中断,同时PTP事件消息通过硬件打上时间戳。

PTPArr0IntStatus(PTP Port Status Register offset 0x0)和PTPArr1IntStatus(PTP Port Status Register offset 0x4)指定是否处理收集错误到达时间戳触发情况。

在时间戳寄存器PTPArr0Time(PTP Port Status Register Offset 0x01 & 0x02)或者PTPArr1Time(PTP Port Status Register Offset 0x05 & ox06 )成功捕捉时间戳后,相对应的无效位PTPArr0TimeVaild(PTP Port Status Register Offset 0x0) 或者 PTPArr1TimeVaild(PTP Port Status Register Offset 0x04)位被设置。

类似的PTP到达中断寄存器和时间戳寄存器,这里设备支持PTP帧离开中断和时间戳寄存器。设备也能够捕捉到从到达和离开PTP帧公共头ID,确保软件能够在正确PTP帧中解析时间戳信息。

当PTP软件接收到帧,各自的场需要定时更新和帧需要向前到下级PTP从节点。软件的PTP帧到达到硬件被标记为From_CPU DSA 标识帧。

注意每一个端口PTPInt(PTP Global Status Register 0x08)位被设置,当PTP帧时间戳到达时,PTPArrIntEn被设置端口或者当一个外向PTP帧时间戳和PTPDepIntEn设置端口。在软件读取和清除PTPArr0TimeVaild(PTP Port Status register offset 0x0)或者PTPArr1TimeVaild(PTP Port status register offset 0x04)中断位被清除。PTP帧入口要求时间戳相关中断和之后软件清除PTPDepTimeVaild(PTP Port Status register offset 0x08)出口时间戳PTP帧。

参考连接

88e6352资料介绍:https://cn.marvell.com/content/dam/marvell/en/products/assets/automotive/ethernet/documents/marvell-automotive-ethernet-88ea6352-product-brief-2019-03.pdf