目录

触发器:

D触发器:

触发器的VHDL描述:

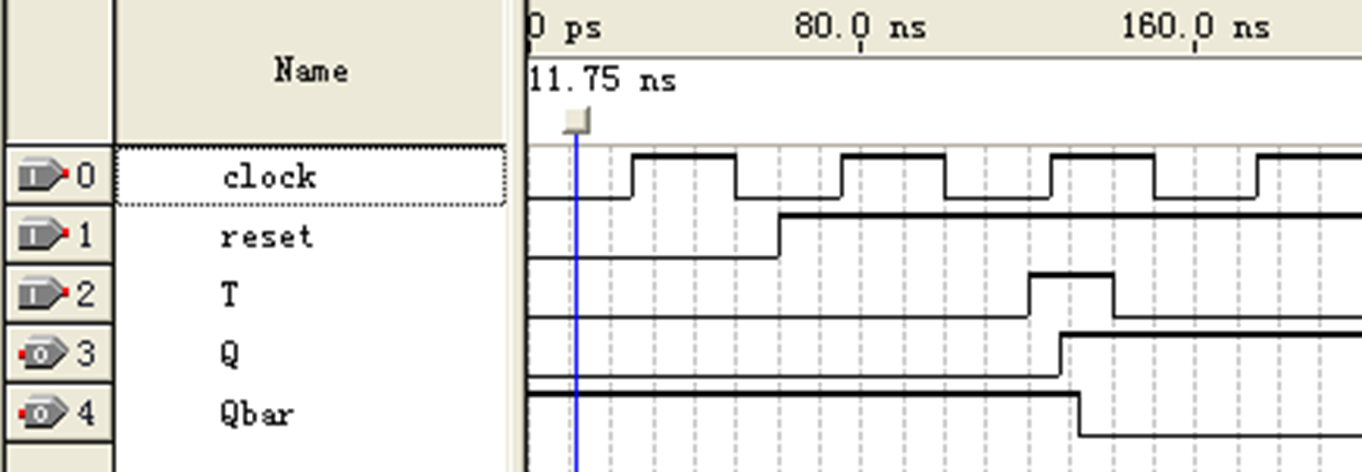

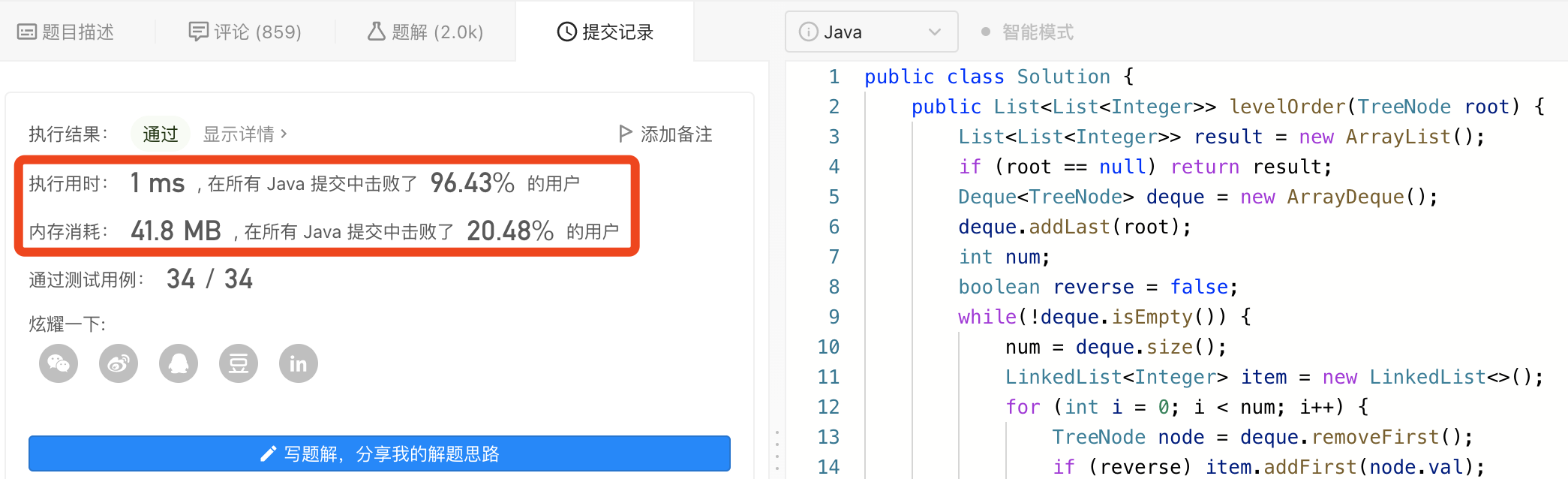

触发器的仿真波形如下:编辑

时钟边沿检测的三种方法:

方法一:

方法二:

方法三:

带有Q非的D触发器:

带有Q非的D触发器的描述:

JK触发器:

JK触发器:

JK触发器的VHDL描述:

T触发器:

真值表:

T触发器:

T触发器的VHDL描述:

触发器:

触发器是指边沿触发的寄存器,常见的有D型,JK型,T型。在描述触发器前要注意时钟上升沿的描述

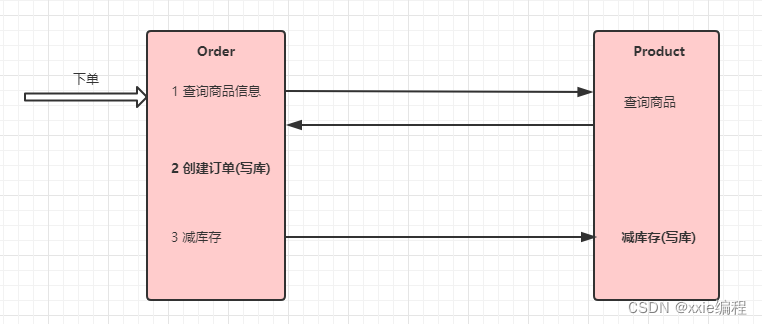

D触发器:

D触发器是最常用的触发器,几乎所有的逻辑电路都可以描述成D触发器与组合逻辑电路

触发器的VHDL描述:

Library ieee;

Use ieee.std_logic_1164.all;

Entity D_FF1 is

port ( D, clk: in std_logic;

Q: out std_logic);

End D_FF1;

Architecture behav of D_FF1 is

Begin

--方法一

process(clk)

begin

if ( clk’s event and clk=‘1’)

then Q<=D;

end if;

end process;

End behav;

--方法二

process

begin

wait until (clk=‘1’) ;

--等同于 wait until clk’event and clk=‘1’;

Q<=D;

end process;

End behav;

方法三

process(clk)

begin

if (clk=‘1’) then

Q<=D;

--利用进程启动特性产生对clk的边沿检测

end if ;

end process;

end behav;

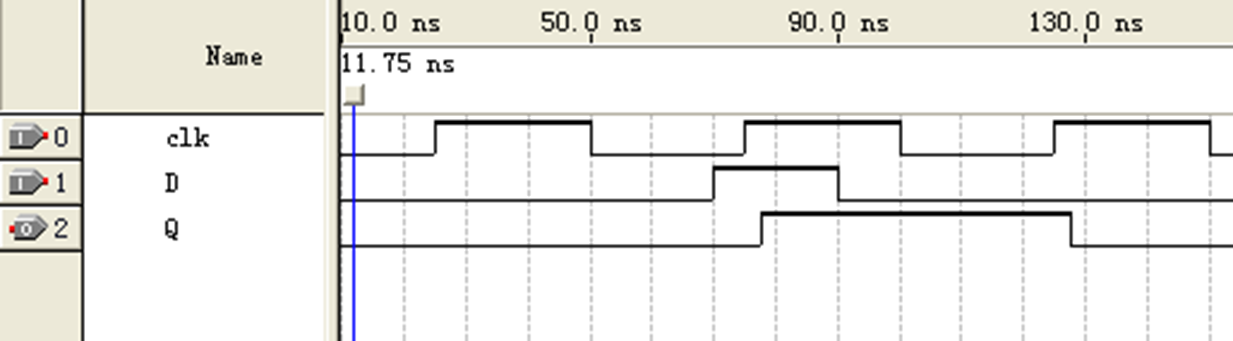

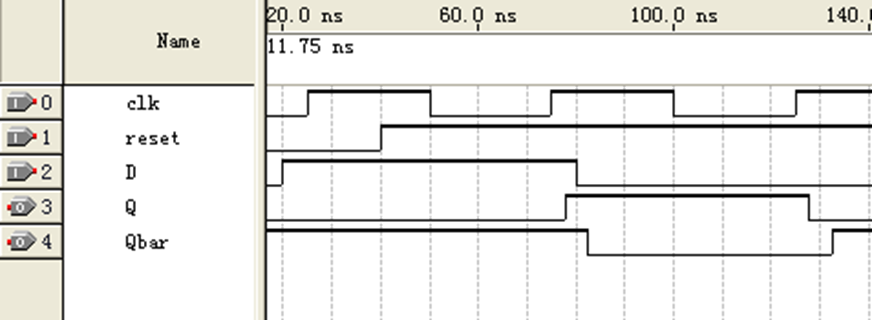

触发器的仿真波形如下:

当时钟上升沿到来时,把D的值赋给Q,之后保持不变。到下一个时钟上升沿到来时,再次把D的值赋给Q。

时钟边沿检测的三种方法:

方法一:

上升沿:clock’ event and clock=‘1’

下降沿:clock’ event and clock=‘0’;

注意:if clock’ event and clock=‘1’语句后面不存在else分支。当clock为std_logic类型时,也可以利用 if rising_edge(clk)或If falling_edge(clk)进行时钟边沿检测。

方法二:

利用WAIT语句启动进程,检测colck的上升沿

方法三:

使用PROCESS语句和IF语句相结合实现。当colck发生跳变的时候启动PROCESS进程,而在执行IF语句时,满足clock=‘1’时才对Q进行赋值更新,所以相当于clock发生跳变且跳变为‘1’时,将D赋给Q,实际上就是D出发器的描述。

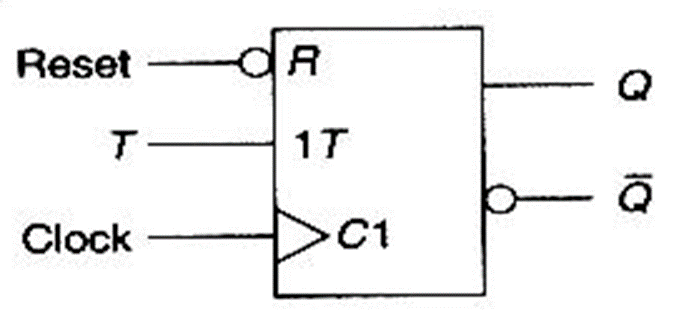

带有Q非的D触发器:

由下图可知,与D触发器相比,该触发器多了Qbar与低电平有效的异步复位信号

带有Q非的D触发器的描述:

Architecture sig of D_FF is

signal state: std_logic ;

Begin

process( clock, reset)

begin

if (reset=‘0’) then state<=‘0’;

else

if rising_edge(clock)

then state<=D;

end if;

end process;

Q<=state;

Qbar<=not state ;

End sig;

Architecture var of D_FF is

Begin

process(clock, reset)

variable state: std_logic ;

begin

if (reset=‘0’) then state:=‘0’;

elsif rising_edge(clock)

then state:=D;

end if;

Q<=state;

Qbar<=not state;

end process;

End var;

当state定义为变量时,其有效范围在process内。因此,Q和Q非的赋值语句只能放在process里面。

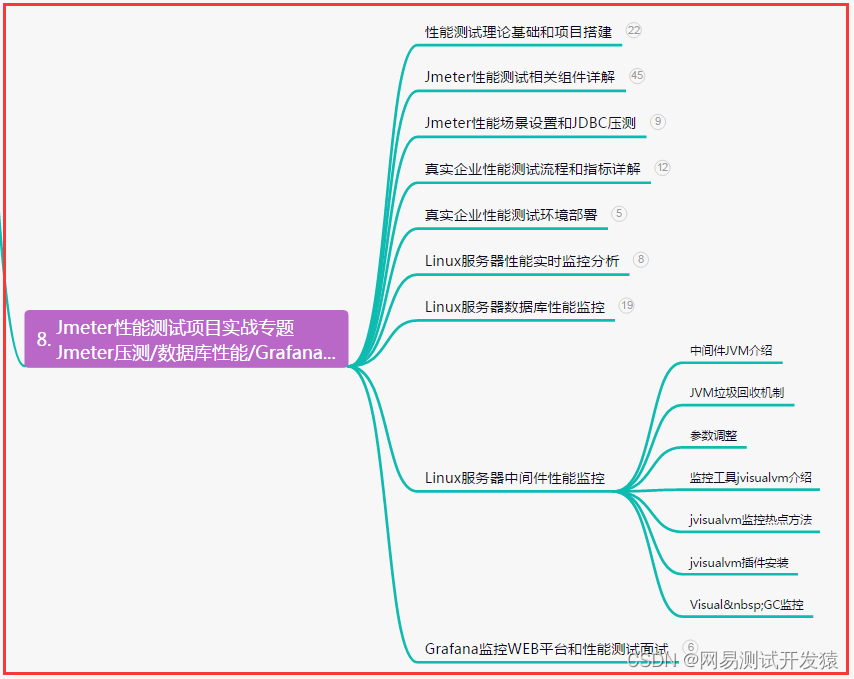

JK触发器:

真值表:

JK触发器:

JK触发器的VHDL描述:

Entity JK_FF is

port ( J, K: in std_logic;

clock,reset:in std_logic;

Q, Qbar : out std_logic );

End JK_FF;

Architecture behav of JK_FF is

signal state : std_logic ;

Begin

process( clock, reset) is

variable jk: std_logic_vector(1 downto 0);

begin

jk:=J&K;

if (reset=‘0’) then state<=‘0’;

elsif rising_edge(clock) then

case jk is

when “11”=> state<=not state;

when “10”=> state<=‘1’;

when “01”=> state<=‘0’;

when others => null;

end case;

end if;

end process;

Q<=state;

Qbar<=not state ;

end behav;

CASE语句要完整,所以在CASE JK的时候要加when others =>null;

T触发器:

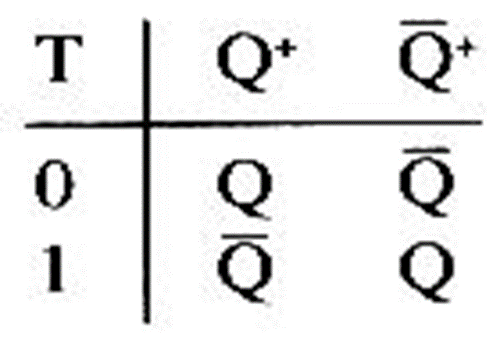

真值表:

T触发器:

T触发器的VHDL描述:

Entity T_FF is

port ( T, clock, reset : in std_logic ;

Q, Qbar : out std_logic );

End T_FF;

Architecture behav of T_FF is

Begin

process(clock, reset)

variable state: std_logic ;

begin

if (reset =‘0’) then state:=‘0’;

elsif rising_edge(clock) then

if T=‘1’then

state := not state;

end if;

end if ;

Q<=state;

Qbar<= not state;

end process;

End behav ;