前言

海思3559a的sdk例子是没有提供BT1120和BT656视频接入的,但实际上硬件是可以支持接入的。不过前提是只支持逐行方式输入,不支持隔行视频,如果想输入PAL制式的隔行视频,请先用芯片转成逐行再接入。不知道是官方手册有意无意的忽略还是太简单约定俗成,例程没有手册相关描述又非常模糊,这里给出SDK2.0.3.1版本的BT656输入调试笔记,输入由adv7280逐行给出

硬件部分:

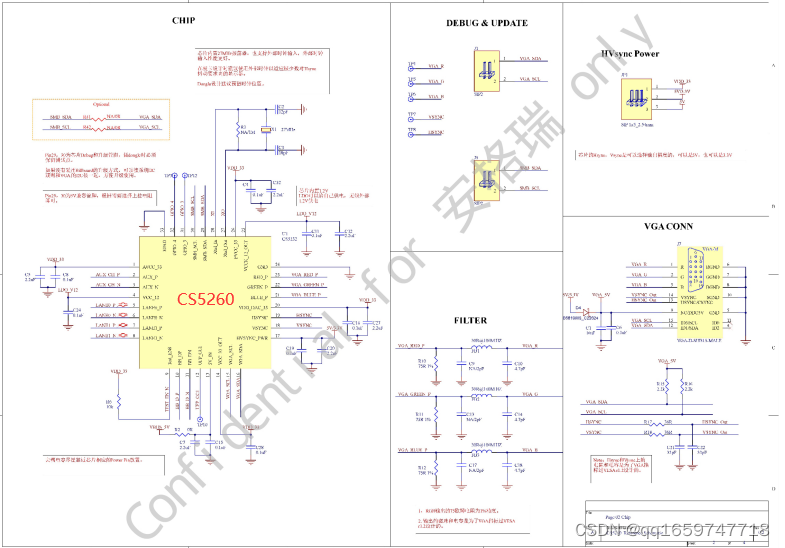

Hi3559AV100 DEV 与 MIPI/SLVS/BT.1120/BT.656/BT601/DC 接口的绑定关系如下

说明不是所有的mipi都可以被当做cmos作采集复用的,相关电路原理图设计如下

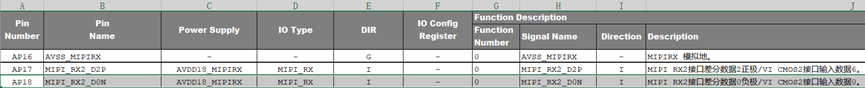

通过《Hi3559AV100_PINOUT_CN》可以查看对应的引脚,发现没有对应的配置寄存器,推测这块不需要我们来配置寄存器的,那就应该是VI CMOS2和MIPI RX Port2/MIPI RX Port3共用引脚通过使能对应接口时钟来选择。

根据《Hi3559A╱C V100 ultra-HD Mobile Camera SoC 用户指南》中MIPI_RX频率配置寄存器(PERI_CRG65),要使能VI CMOS2时钟,应当把PERI_CRG65的bit[11:9]置为111

此处有两种修改方式,阅读加载驱动的脚本load3559av100_multicore,之前传感器类型我们都选择的imx477作为模板加载,直接传入bt656在2.0.3.1版本的SDK里是会报not support的错误,根据报错信息可以找到Hi3559AV100_SDK_V2.0.3.1/drv/interdrv/sysconfig路径下的sysconfig.c

module_init(hi_sysconfig_init);

sensor_config(sensor_list);

static int sensor_config(char *s)

{

int ret;

int index;

int clock;

char* line;

BUS_TYPE bus_type;

char sensor_name[SENSOR_NAME_LEN];

while ((line = strsep(&s, ":")) != NULL)

{

int i;

char* argv[8];

for (i = 0; (argv[i] = strsep(&line, ",")) != NULL;)

{

ret = parse_sensor_name(argv[i], sensor_name);

if(ret >= 0)

{

index = parse_sensor_index(argv[i]);//报错信息出处

if (index >= 0)

{

clock = parse_sensor_clock(sensor_name);

bus_type = parse_sensor_bus_type(sensor_name);

if (is_coms(sensor_name))

{

coms_clock_config(index);

}

else

{

sensor_bus_pin_mux(index, bus_type);

sensor_clock_config(index, clock);

}

}

}

if (++i == ARRAY_SIZE(argv))

{

break;

}

}

}

return 0;

}

is_coms(sensor_name)

static int is_coms(char *name)

{

unsigned int len;

len = SENSOR_NAME_LEN;

if ( (0 == strncmp("bt1120", name, len))

|| (0 == strncmp("bt656", name, len))

|| (0 == strncmp("bt601", name, len)))

{

return 1;

}

else

{

return 0;

}

}

第一种方式

可见,传bt656在这里也仅仅是为了配置这个寄存器,那么我们直接传参后单独修改寄存器也是可以的,直接

devmem 0x12010104 32 0xCEBEDB

个人觉得,归根结底到底层的实现肯定都是通过配置寄存器解决的,只是海思在驱动或者应用层的某些函数上帮我们封装好了,所以这个看似粗暴的办法,在分析清楚实现原理后,也是可以使用的

第二种方式

第二种就是忽略掉parse_sensor_index的报错往下走,将coms_clock_config修改正确,官方的SDK包里这个配置是不正确的!!

修改为

static void coms_clock_config(int index)

{

if(0 == index)

{

reg_write32(0x5 << 15, 0x7 << 15, (unsigned long)reg_crg_base+0x0104);

}

else if(1 == index)

{

reg_write32(0x6 << 21, 0x7 << 21, (unsigned long)reg_crg_base+0x0104);

}

else if(2 == index)

{

reg_write32(0x7 << 9, 0x7 << 9, (unsigned long)reg_crg_base+0x0104);

}

}

重新编译sysconfig.ko即可,这个就不需要单独配置寄存器了

代码部分

sample/comoon路径下的samplecomm.h新增BT656枚举

typedef enum hiSAMPLE_SNS_TYPE_E

{

SONY_IMX477_MIPI_12M_30FPS_12BIT,

SONY_IMX477_MIPI_9M_50FPS_10BIT,

SONY_IMX477_MIPI_8M_60FPS_12BIT,

SONY_IMX477_MIPI_8M_30FPS_12BIT,

SONY_IMX290_MIPI_2M_30FPS_12BIT,

SONY_IMX290_MIPI_2M_30FPS_12BIT_WDR3TO1,

SONY_IMX334_SLAVE_MIPI_8M_30FPS_12BIT,

SONY_IMX334_MIPI_8M_30FPS_12BIT,

SONY_IMX334_MIPI_8M_30FPS_12BIT_WDR2TO1,

SONY_IMX277_SLVS_8M_120FPS_10BIT,

SONY_IMX277_SLVS_8M_30FPS_12BIT,

SONY_IMX277_SLVS_8M_60FPS_12BIT,

SONY_IMX277_SLVS_12M_30FPS_12BIT,

SONY_IMX277_SLVS_2M_240FPS_12BIT,

FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P,

FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P,

BT656_HX_TEST,

SAMPLE_SNS_TYPE_BUTT,

} SAMPLE_SNS_TYPE_E;

sample/common路径下的sample_comm_vi.c

VI MIPI设置

Hi3559AV100 第 0, 1 路 BT.656 与 MIPI 无关, 无需配置, 第 2 路需要配置 MIPI 输入模式为 INPUT_MODE_BT656, 且 devno 为对应的 CMOS 编号。

/* xin.han add BT656 */

combo_dev_attr_t MIPI_BT656_ATTR_HX =

{

.devno = 2,

.input_mode = INPUT_MODE_BT656,

.data_rate = DATA_RATE_X1,

.img_rect = {0, 0, 720, 576},

{

.mipi_attr =

{

DATA_TYPE_RAW_12BIT,

// DATA_TYPE_YUV422_8BIT,

// DATA_TYPE_RAW_8BIT,

// DATA_TYPE_RAW_16BIT,

HI_MIPI_WDR_MODE_NONE,

{0, 1, 2, 3, -1, -1, -1, -1}

}

}//怀疑mipi属性这部分没起作用,毕竟也没用mipi

};

VI DEV 配置

接口模式: VI_MODE_BT656

Mask 设置: 只需设置 au32ComponentMask[0] = 0xFF000000

扫描格式: 只支持逐行 VI_SCAN_PROGRESSIVE

UV 顺序: UV 顺序根据实际输入时序确定,

VI_DATA_SEQ_UYVY/VI_DATA_SEQ_VYUY/VI_DATA_SEQ_YUYV/VI_DATA_

SEQ_YVYU。

数据类型: BT656 进 YUV 数据,因此是 VI_DATA_TYPE_YUV

VI_DEV_ATTR_S DEV_BT656_ATTR_HX =

{

VI_MODE_BT656,

VI_WORK_MODE_1Multiplex,

{0x00FF0000, 0},//此处和官方手册的不一致

VI_SCAN_PROGRESSIVE,

{ -1, -1, -1, -1},

VI_DATA_SEQ_YUYV,

{

VI_VSYNC_PULSE, VI_VSYNC_NEG_LOW, VI_HSYNC_VALID_SINGNAL,VI_HSYNC_NEG_HIGH, VI_VSYNC_VALID_SINGAL, VI_VSYNC_VALID_NEG_HIGH,

{

/*hsync_hfb hsync_act hsync_hhb*/

0, 720, 0,

/*vsync0_vhb vsync0_act vsync0_hhb*/

0, 576, 0,

/*vsync1_vhb vsync1_act vsync1_hhb*/

0, 0, 0

}

},

VI_DATA_TYPE_YUV,

HI_FALSE,

{720 , 576},

{

{

{720 , 576},

},

{

VI_REPHASE_MODE_NONE,

VI_REPHASE_MODE_NONE

}

},

{

WDR_MODE_NONE,

576

},

DATA_RATE_X1

};

掩码问题

VI PIPE 配置

PIPE 的 bIspBypass 设置为 HI_TRUE。

PIPE 的像素格式设置为 PIXEL_FORMAT_YVU_SEMIPLANAR_422。

PIPE 的 bit 位宽 nBitWidth 设置为 DATA_BITWIDTH_8。

VI_PIPE_ATTR_S PIPE_BT656_ATTR_HX =

{

VI_PIPE_BYPASS_NONE,

HI_FALSE,//UV skip enable

HI_TRUE,//ISP Bypass 不需要ISP所以TRUE

720, 576,

PIXEL_FORMAT_YVU_SEMIPLANAR_422,

COMPRESS_MODE_NONE,

DATA_BITWIDTH_8,

HI_FALSE,

{

PIXEL_FORMAT_YVU_SEMIPLANAR_422,

DATA_BITWIDTH_8,

VI_NR_REF_FROM_RFR,

COMPRESS_MODE_NONE

},

HI_FALSE,

{-1, -1}

};

VI CHN设置

VI_CHN_ATTR_S CHN_BT656_ATTR_HX =

{

{720, 576},

PIXEL_FORMAT_YVU_SEMIPLANAR_422,

DYNAMIC_RANGE_SDR8,

VIDEO_FORMAT_LINEAR,

COMPRESS_MODE_NONE,

0, 0,

1,

{ -1, -1}

};

(2)新增sensor类型

static input_mode_t SAMPLE_COMM_VI_GetSnsInputMode(SAMPLE_SNS_TYPE_E enSnsType)

{

input_mode_t enInputMode;

switch (enSnsType)

{

// printf("!!!!!!!!!!!!!!!enSnsTypeis %d!",enSnsType);

case SONY_IMX277_SLVS_8M_120FPS_10BIT: /*imx277 test*/

case SONY_IMX277_SLVS_8M_30FPS_12BIT:

case SONY_IMX277_SLVS_8M_60FPS_12BIT:

case SONY_IMX277_SLVS_12M_30FPS_12BIT:

case SONY_IMX277_SLVS_2M_240FPS_12BIT:

enInputMode = INPUT_MODE_SLVS;

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P:

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P:

enInputMode=INPUT_MODE_LVDS;

break;

case BT656_HX_TEST:

enInputMode=INPUT_MODE_BT656;

break;

default:

enInputMode = INPUT_MODE_MIPI;

break;

}

return enInputMode;

}

(3)memcpy BT656的combo_dev_attr_t结构体

HI_S32 SAMPLE_COMM_VI_GetComboAttrBySns(SAMPLE_SNS_TYPE_E enSnsType, combo_dev_t MipiDev, combo_dev_attr_t* pstComboAttr)

{

switch (enSnsType)

{

// SAMPLE_PRT("!!!!!!!!!!!!!!!enSnsTypeis %d!",enSnsType);

case SONY_IMX477_MIPI_12M_30FPS_12BIT:

if (0 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN0_SENSOR_IMX477_12BIT_12M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (2 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN2_SENSOR_IMX477_12BIT_12M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (4 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN4_SENSOR_IMX477_12BIT_12M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (6 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN6_SENSOR_IMX477_12BIT_12M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else

{

SAMPLE_PRT("unsupported mipi dev :%d for SnsType :%d\n", MipiDev, enSnsType);

}

break;

case SONY_IMX477_MIPI_9M_50FPS_10BIT:

if (0 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN0_SENSOR_IMX477_10BIT_9M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (2 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN2_SENSOR_IMX477_10BIT_9M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (4 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN4_SENSOR_IMX477_10BIT_9M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (6 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN6_SENSOR_IMX477_10BIT_9M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else

{

SAMPLE_PRT("unsupported mipi dev :%d for SnsType :%d\n", MipiDev, enSnsType);

}

break;

case SONY_IMX477_MIPI_8M_60FPS_12BIT:

if (0 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN0_SENSOR_IMX477_10BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (2 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN2_SENSOR_IMX477_10BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (4 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN2_SENSOR_IMX477_10BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (6 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN4_SENSOR_IMX477_10BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else

{

SAMPLE_PRT("unsupported mipi dev :%d for SnsType :%d\n",MipiDev, enSnsType);

}

break;

case SONY_IMX477_MIPI_8M_30FPS_12BIT:

if (0 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN0_SENSOR_IMX477_12BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (2 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN2_SENSOR_IMX477_12BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (4 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN2_SENSOR_IMX477_12BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (6 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN4_SENSOR_IMX477_12BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else

{

SAMPLE_PRT("unsupported mipi dev :%d for SnsType :%d\n",MipiDev, enSnsType);

}

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT:

if (0 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN0_SENSOR_IMX290_12BIT_2M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else if (1 == MipiDev)

{

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN1_SENSOR_IMX290_12BIT_2M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

else

{

SAMPLE_PRT("unsupported mipi dev :%d for SnsType :%d\n",MipiDev, enSnsType);

}

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT_WDR3TO1:

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN0_SENSOR_IMX290_10BIT_2M_WDR3to1_ATTR, sizeof(combo_dev_attr_t));

break;

case SONY_IMX334_SLAVE_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT:

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN0_SENSOR_IMX334_12BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

break;

case SONY_IMX334_MIPI_8M_30FPS_12BIT_WDR2TO1:

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN0_SENSOR_IMX334_12BIT_8M_WDR2to1_ATTR, sizeof(combo_dev_attr_t));

break;

case SONY_IMX277_SLVS_8M_120FPS_10BIT:

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &SLVS_8lane_CHN0_SENSOR_IMX277_10BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

break;

case SONY_IMX277_SLVS_8M_30FPS_12BIT:

case SONY_IMX277_SLVS_8M_60FPS_12BIT:

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &SLVS_6lane_CHN0_SENSOR_IMX277_12BIT_8M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

break;

case SONY_IMX277_SLVS_12M_30FPS_12BIT:

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &SLVS_6lane_CHN0_SENSOR_IMX277_12BIT_12M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

break;

case SONY_IMX277_SLVS_2M_240FPS_12BIT:

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &SLVS_6lane_CHN0_SENSOR_IMX277_12BIT_2M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P:

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &LVDS_4lane_CHN0_FPGA_CYCLONE_16BIT_xM_1080P_NOWDR_ATTR, sizeof(combo_dev_attr_t));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P:

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &LVDS_4lane_CHN1_FPGA_CYCLONE_16BIT_xM_720P_NOWDR_ATTR, sizeof(combo_dev_attr_t));

break;

case BT656_HX_TEST:

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_BT656_ATTR_HX, sizeof(combo_dev_attr_t));

break;

default:

SAMPLE_PRT("not support enSnsType: %d\n", enSnsType);

hi_memcpy(pstComboAttr, sizeof(combo_dev_attr_t), &MIPI_4lane_CHN0_SENSOR_IMX477_12BIT_12M_NOWDR_ATTR, sizeof(combo_dev_attr_t));

}

return HI_SUCCESS;

}

(4)memcpy BT656的VI_DEV_ATTR_S结构体

HI_S32 SAMPLE_COMM_VI_GetDevAttrBySns(SAMPLE_SNS_TYPE_E enSnsType, VI_DEV_ATTR_S* pstViDevAttr)

{

switch (enSnsType)

{

// SAMPLE_PRT("!!!!!!!!!!!!!!!enSnsTypeis %d!",enSnsType);

case SONY_IMX477_MIPI_12M_30FPS_12BIT:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX477_12M_BASE, sizeof(VI_DEV_ATTR_S));

break;

case SONY_IMX477_MIPI_9M_50FPS_10BIT:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX477_9M_BASE, sizeof(VI_DEV_ATTR_S));

break;

case SONY_IMX477_MIPI_8M_60FPS_12BIT:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX477_8M_BASE, sizeof(VI_DEV_ATTR_S));

break;

case SONY_IMX477_MIPI_8M_30FPS_12BIT:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX477_8M_BASE, sizeof(VI_DEV_ATTR_S));

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX290_2M_BASE, sizeof(VI_DEV_ATTR_S));

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT_WDR3TO1:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX290_2M_BASE, sizeof(VI_DEV_ATTR_S));

pstViDevAttr->au32ComponentMask[0] = 0xFFC00000;

break;

case SONY_IMX334_SLAVE_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX334_8M_BASE, sizeof(VI_DEV_ATTR_S));

break;

case SONY_IMX334_MIPI_8M_30FPS_12BIT_WDR2TO1:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX334_8M_WDR2TO1_BASE, sizeof(VI_DEV_ATTR_S));

break;

case SONY_IMX277_SLVS_8M_120FPS_10BIT:

case SONY_IMX277_SLVS_8M_30FPS_12BIT:

case SONY_IMX277_SLVS_8M_60FPS_12BIT:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX277_SLVS_8M_BASE, sizeof(VI_DEV_ATTR_S));

break;

case SONY_IMX277_SLVS_12M_30FPS_12BIT:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX277_SLVS_12M_BASE, sizeof(VI_DEV_ATTR_S));

break;

case SONY_IMX277_SLVS_2M_240FPS_12BIT:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX277_SLVS_2M_BASE, sizeof(VI_DEV_ATTR_S));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_FPGA_CYCLONE_1920x1080_BASE, sizeof(VI_DEV_ATTR_S));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_FPGA_CYCLONE_720x576_BASE, sizeof(VI_DEV_ATTR_S));

break;

case BT656_HX_TEST:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_BT656_ATTR_HX, sizeof(VI_DEV_ATTR_S));

break;

default:

hi_memcpy(pstViDevAttr, sizeof(VI_DEV_ATTR_S), &DEV_ATTR_IMX477_8M_BASE, sizeof(VI_DEV_ATTR_S));

}

return HI_SUCCESS;

}

(5)memcpy BT656的VI_PIPE_ATTR_S结构体

HI_S32 SAMPLE_COMM_VI_GetPipeAttrBySns(SAMPLE_SNS_TYPE_E enSnsType, VI_PIPE_ATTR_S* pstPipeAttr)

{

switch (enSnsType)

{

// printf("warning:!!!!!!!!!!!!!!!enSnsTypeis %d!",enSnsType);

case SONY_IMX477_MIPI_12M_30FPS_12BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_4000x3000_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX477_MIPI_9M_50FPS_10BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_3000x3000_RAW10_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX477_MIPI_8M_60FPS_12BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_3840x2160_RAW10_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX477_MIPI_8M_30FPS_12BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_3840x2160_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_1920x1080_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT_WDR3TO1:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_1920x1080_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

pstPipeAttr->enPixFmt = PIXEL_FORMAT_RGB_BAYER_10BPP;

pstPipeAttr->enBitWidth = DATA_BITWIDTH_10;

break;

case SONY_IMX334_SLAVE_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_3840x2160_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX334_MIPI_8M_30FPS_12BIT_WDR2TO1:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_3840x2160_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX277_SLVS_8M_120FPS_10BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_3840x2160_RAW10_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX277_SLVS_8M_30FPS_12BIT:

case SONY_IMX277_SLVS_8M_60FPS_12BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_3840x2160_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX277_SLVS_12M_30FPS_12BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_4000x3000_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case SONY_IMX277_SLVS_2M_240FPS_12BIT:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_1920x1080_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_FPGA_CYCLONE_ATTR_1920x1080_RAW16_422_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_FPGA_CYCLONE_ATTR_720x576_RAW16_422_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

break;

case BT656_HX_TEST:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_BT656_ATTR_HX, sizeof(VI_PIPE_ATTR_S));

break;

default:

hi_memcpy(pstPipeAttr, sizeof(VI_PIPE_ATTR_S), &PIPE_ATTR_3840x2160_RAW12_420_3DNR_RFR, sizeof(VI_PIPE_ATTR_S));

}

return HI_SUCCESS;

}

(6)memcpy BT656的VI_CHN_ATTR_S结构体

HI_S32 SAMPLE_COMM_VI_GetChnAttrBySns(SAMPLE_SNS_TYPE_E enSnsType, VI_CHN_ATTR_S* pstChnAttr)

{

switch (enSnsType)

{

// SAMPLE_PRT("!!!!!!!!!!!!!!!enSnsTypeis %d!",enSnsType);

case SONY_IMX477_MIPI_12M_30FPS_12BIT:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_4000x3000_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX477_MIPI_9M_50FPS_10BIT:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_3000x3000_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX477_MIPI_8M_60FPS_12BIT:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_3840x2160_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX477_MIPI_8M_30FPS_12BIT:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_3840x2160_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_1920x1080_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT_WDR3TO1:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_1920x1080_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX334_SLAVE_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_3840x2160_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX334_MIPI_8M_30FPS_12BIT_WDR2TO1:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_3840x2160_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX277_SLVS_8M_120FPS_10BIT:

case SONY_IMX277_SLVS_8M_30FPS_12BIT:

case SONY_IMX277_SLVS_8M_60FPS_12BIT:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_3840x2160_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX277_SLVS_12M_30FPS_12BIT:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_4000x3000_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case SONY_IMX277_SLVS_2M_240FPS_12BIT:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_1920x1080_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_FPGA_ATTR_1920x1080_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_FPGA_ATTR_720x576_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

break;

case BT656_HX_TEST:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_BT656_ATTR_HX, sizeof(VI_CHN_ATTR_S));

break;

default:

hi_memcpy(pstChnAttr, sizeof(VI_CHN_ATTR_S), &CHN_ATTR_3840x2160_420_SDR8_LINEAR, sizeof(VI_CHN_ATTR_S));

}

return HI_SUCCESS;

}

(7)根据模式选择不同分辨率

HI_S32 SAMPLE_COMM_VI_GetSizeBySensor(SAMPLE_SNS_TYPE_E enMode, PIC_SIZE_E* penSize)

{

HI_S32 s32Ret = HI_SUCCESS;

if (!penSize)

{

return HI_FAILURE;

}

switch (enMode)

{

SAMPLE_PRT("!!!!!!!!!!!!!!!enMode %d!",enMode);

case SONY_IMX477_MIPI_12M_30FPS_12BIT:

*penSize = PIC_4000x3000;

break;

case SONY_IMX477_MIPI_9M_50FPS_10BIT:

*penSize = PIC_3000x3000;

break;

case SONY_IMX477_MIPI_8M_60FPS_12BIT:

*penSize = PIC_3840x2160;

break;

case SONY_IMX477_MIPI_8M_30FPS_12BIT:

*penSize = PIC_3840x2160;

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT:

case SONY_IMX290_MIPI_2M_30FPS_12BIT_WDR3TO1:

*penSize = PIC_1080P;

break;

case SONY_IMX334_SLAVE_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT_WDR2TO1:

*penSize = PIC_3840x2160;

break;

case SONY_IMX277_SLVS_8M_120FPS_10BIT:

case SONY_IMX277_SLVS_8M_30FPS_12BIT:

case SONY_IMX277_SLVS_8M_60FPS_12BIT:

*penSize = PIC_3840x2160;

break;

case SONY_IMX277_SLVS_12M_30FPS_12BIT:

*penSize = PIC_4000x3000;

break;

case SONY_IMX277_SLVS_2M_240FPS_12BIT:

*penSize = PIC_1080P;

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P:

*penSize=PIC_1080P;

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P:

*penSize=PIC_D1_PAL;

break;

case BT656_HX_TEST:

*penSize=PIC_D1_PAL;

break;

default:

*penSize = PIC_3840x2160;

break;

}

return s32Ret;

}

(8)根据模式选择正确的设备号

combo_dev_t SAMPLE_COMM_VI_GetComboDevBySensor(SAMPLE_SNS_TYPE_E enMode, HI_S32 s32SnsIdx)

{

combo_dev_t dev = 0;

switch (enMode)

{

SAMPLE_PRT("!!!!!!!!!!!!!!!enMode %d!",enMode);

case SONY_IMX477_MIPI_12M_30FPS_12BIT:

case SONY_IMX477_MIPI_9M_50FPS_10BIT:

case SONY_IMX477_MIPI_8M_60FPS_12BIT:

case SONY_IMX477_MIPI_8M_30FPS_12BIT:

case SONY_IMX290_MIPI_2M_30FPS_12BIT:

case SONY_IMX290_MIPI_2M_30FPS_12BIT_WDR3TO1:

case SONY_IMX334_SLAVE_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT_WDR2TO1:

if(0 == s32SnsIdx)

{

dev= 0;

}

else if(1 == s32SnsIdx)

{

dev= 2;

}

else if(2 == s32SnsIdx)

{

dev= 4;

}

else if(3 == s32SnsIdx)

{

dev= 6;

}

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P:

dev= 0;

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P:

dev= 2;

break;

case BT656_HX_TEST:

dev= 2;

break;

case SONY_IMX277_SLVS_8M_120FPS_10BIT:

case SONY_IMX277_SLVS_8M_30FPS_12BIT:

case SONY_IMX277_SLVS_8M_60FPS_12BIT:

case SONY_IMX277_SLVS_12M_30FPS_12BIT:

case SONY_IMX277_SLVS_2M_240FPS_12BIT:

if(0 == s32SnsIdx)

{

dev= 0;

}

else if(1 == s32SnsIdx)

{

dev= 2; //8;

}

break;

default:

dev= 0;

break;

}

return dev;

}

关于返回的dev的值

结合手册之前的描述,推断:结构体combo_dev_attr_t的devno不是VI DEV号,也不是MIPI RX设备号(这里也根本没使用MIPI接口),而是VI CMOS号,本案例使用的是Hi3559A的VI CMOS2,因此devno = 2所以对应这里也返回的是2。

sample/common路径下的sampl_comm_isp.c

(1)新增结构体ISP_PUB_ATTR_S

ISP_PUB_ATTR_S BT656_HX_TEST =

{

{0, 0, 720, 576},

{720, 576},

30,

BAYER_GRBG,

WDR_MODE_NONE,

0,

};

(2)memcpy新增的ISP_PUB_ATTR_S结构体

HI_S32 SAMPLE_COMM_ISP_GetIspAttrBySns(SAMPLE_SNS_TYPE_E enSnsType, ISP_PUB_ATTR_S* pstPubAttr)

{

switch (enSnsType)

{

case SONY_IMX477_MIPI_12M_30FPS_12BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX477_12M_30FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX477_MIPI_9M_50FPS_10BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX477_9M_50FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX477_MIPI_8M_60FPS_12BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX477_8M_60FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX477_MIPI_8M_30FPS_12BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX477_8M_30FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX290_2M_30FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX290_MIPI_2M_30FPS_12BIT_WDR3TO1:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX290_MIPI_2M_30FPS_WDR3TO1_LINE, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX334_SLAVE_MIPI_8M_30FPS_12BIT:

case SONY_IMX334_MIPI_8M_30FPS_12BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX334_4K_30FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX334_MIPI_8M_30FPS_12BIT_WDR2TO1:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX334_4K_30FPS_WDR2TO1_LINE, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX277_SLVS_8M_120FPS_10BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX277_SLVS_8M_120FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX277_SLVS_8M_30FPS_12BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX277_SLVS_8M_30FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX277_SLVS_8M_60FPS_12BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX277_SLVS_8M_60FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX277_SLVS_12M_30FPS_12BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX277_SLVS_12M_30FPS, sizeof(ISP_PUB_ATTR_S));

break;

case SONY_IMX277_SLVS_2M_240FPS_12BIT:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX277_SLVS_2M_240FPS, sizeof(ISP_PUB_ATTR_S));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_1080P:

memcpy(pstPubAttr, &ISP_PUB_ATTR_FPGA_LVDS_xM_xFPS_1080P, sizeof(ISP_PUB_ATTR_S));

break;

case FPGA_CYCLONE_LVDS_XM_XFPS_16BIT_720P:

memcpy(pstPubAttr, &ISP_PUB_ATTR_FPGA_LVDS_xM_xFPS_720P, sizeof(ISP_PUB_ATTR_S));

break;

case BT656_HX_TEST:

memcpy(pstPubAttr, &BT656_HX_TEST, sizeof(ISP_PUB_ATTR_S));

break;

default:

memcpy(pstPubAttr, &ISP_PUB_ATTR_IMX477_8M_30FPS, sizeof(ISP_PUB_ATTR_S));

break;

}

return HI_SUCCESS;

}

修改makefile sample/Makefile.param,修改sensor类型

SENSOR0_TYPE ?= BT656_HX_TEST

SENSOR1_TYPE ?= BT656_HX_TEST

SENSOR2_TYPE ?= BT656_HX_TEST

SENSOR3_TYPE ?= BT656_HX_TEST

加载ko文件时还是正常操作就可以

VI日志

这些改完后就可以看到正确的VI日志而不是一团空白了

作为软件部分可以确定一定以及肯定,已经全部修改完毕了。

再出不来图像就需要联合硬件工程师排查电源,时钟,复位,甚至接线等问题(并口线在高速时要求相对会严格一些),联合逻辑工程师排查图像是否逐行,时钟可以测量到但是性能是否满足要求,物理层是否有数据流通。涉及匹配的电阻

如果硬件确认无误后,结合当前的配置环境,可以在vi的日志上,查看中断的是否增长,图像有无丢失,帧率是否稳定,基本就可以确定vi调试OK了,后续vi绑定vpss,vpss在绑定venc参考venc的sample或者之前的rtsp拉流或者本地保存,就可以直接看到图像来进一步确定最后结果和成像质量了