目录

计数器的设计:

计数器的作用:

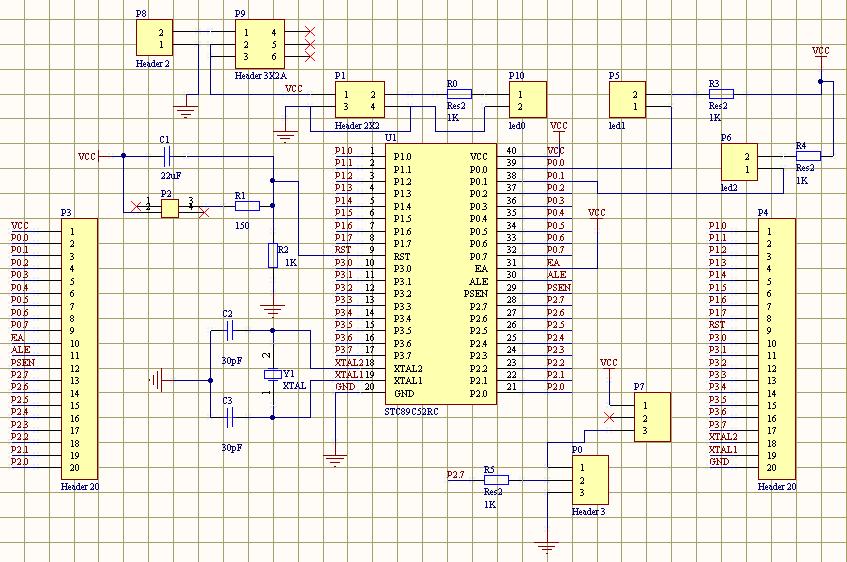

计数器的实现:

1、用“+”函数描述:

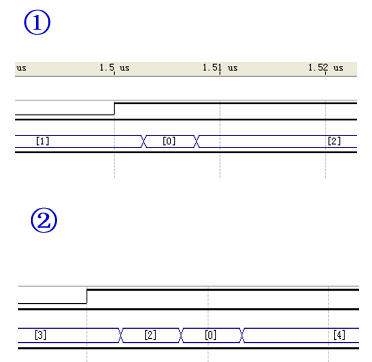

用T触发器级联构成的串行进位的二进制加法计数器的仿真波形:

计数器的仿真:

计数器的设计:

计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路

计数器的作用:

主要是对脉冲的个数进行技术,以实现测量、计数和控制的功能,同时兼有分频功能。比如七位计数器,可对输入时钟进行七分频。

计数器的实现:

1、用“+”函数描述:

Library ieee ;

Use ieee.std_logic_1164.all;

Use ieee.std_logic_unsigned.all;

Entity counter is

generic( n: natural :=4);

port ( clk : in std_logic;

reset : in std_logic ;

count : out std_logic_vector(n-1 downto 0) );

End counter;

architecture ripple of counter is

component T_FF is

port( T : in std_logic ;

clk:in std_logic;

reset:in std_logic;

Q : out std_logic;

Qbar:out std_logic);

end component ; --将前面描述好的T触发器定义为元件;

signal carry: std_logic_vector( n downto 0);

Begin

carry(0)<=clk;

g0: for i in 0 to n-1 generate --循环

T1: T_FF port map ( ‘1’, carry( i ), reset, count( i ), carry( i+1 ) );

end generate g0;

End ripple ;

上例程序中的循环:

g0: for i in 0 to n-1 generate --循环

T1: T_FF port map ( ‘1’, carry( i ), reset, count( i ), carry( i+1 ) );

可以分解成:

T0: T_FF port map ( ‘1’, carry( 0 ), reset, count( 0 ), carry(1 ) );

T1: T_FF port map ( ‘1’, carry( 1 ), reset, count( 1 ), carry( 2 ) );

T2: T_FF port map ( ‘1’, carry( 2 ), reset, count( 2 ), carry( 3 ) );

T3: T_FF port map ( ‘1’, carry( 3 ), reset, count( 3 ), carry( 4 ) );

…………………………

…………………………

Tn-1: T_FF port map ( ‘1’, carry( n-1 ), reset, count( n-1 ), co );

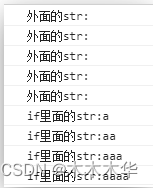

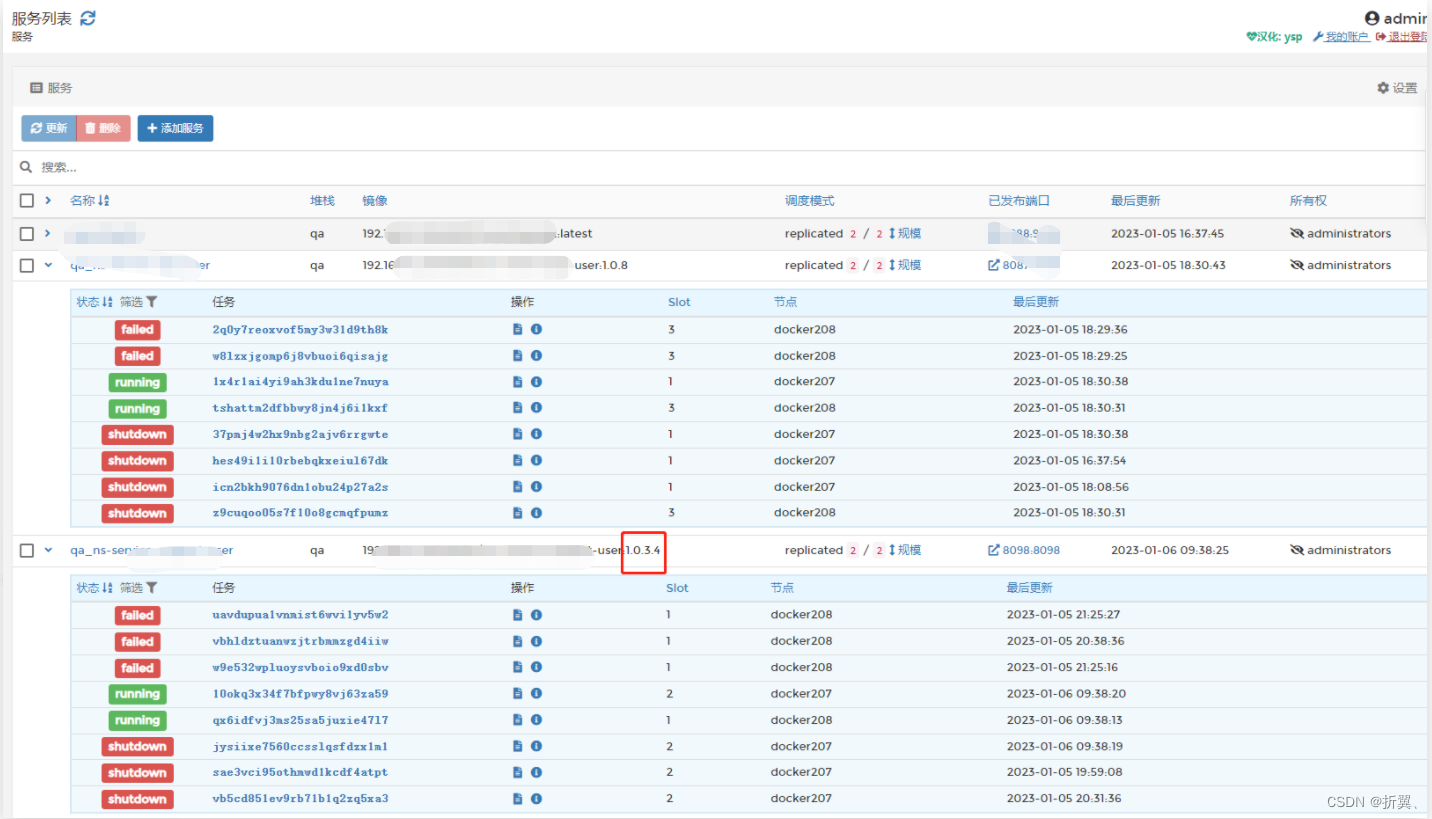

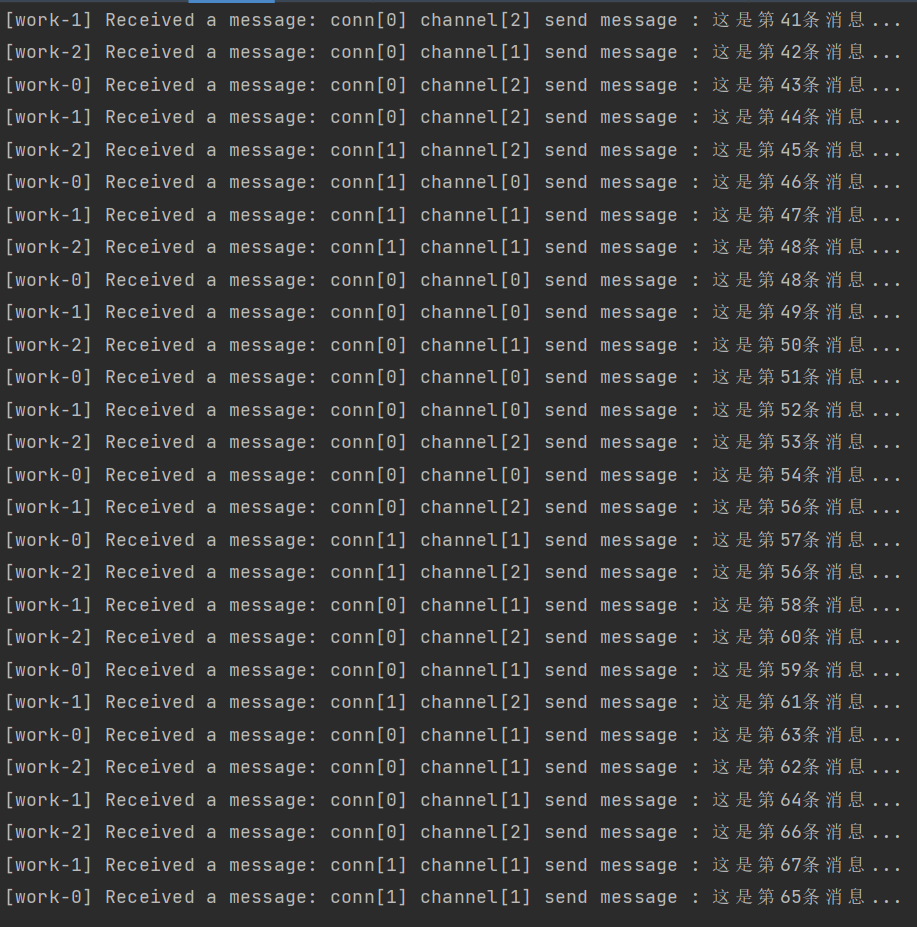

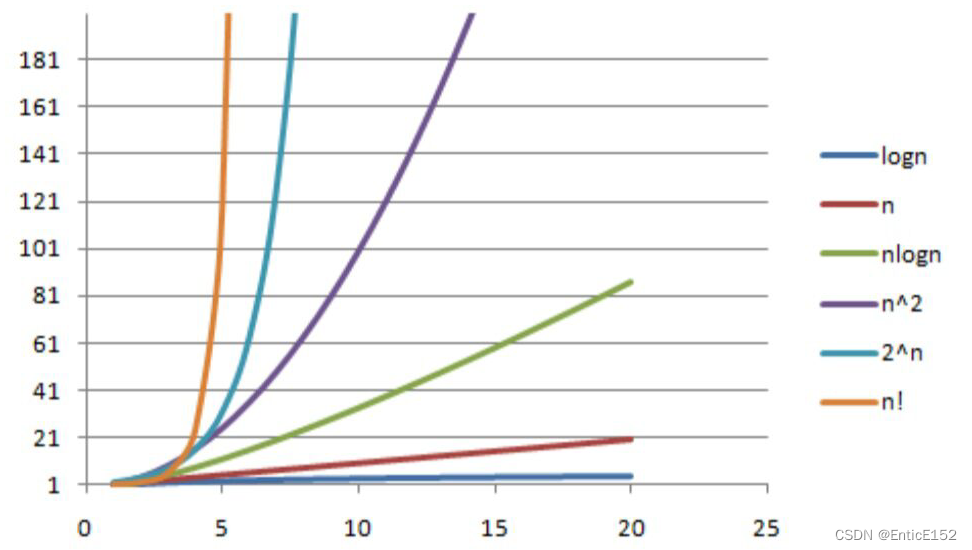

用T触发器级联构成的串行进位的二进制加法计数器的仿真波形:

注意:这里我们可以发现在奇数变为偶数的时候有一个小小的变化。

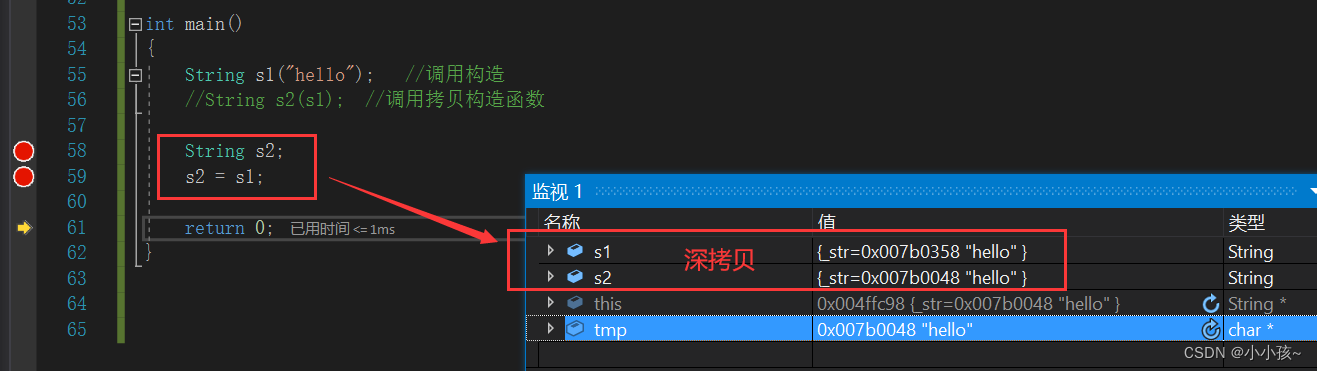

计数器的仿真:

信号赋值的时候有延迟,在计数器由001变为010的时候,先是由

count(0)<=0;carry(1)<=1; -第一步

count(1)<=1;

所以count会先变为000,接着延迟一段时间后才变为010。

同理,对于011变为100的时候,有:

count(0)<=0;carry(1)<=1; -第一步

count(1)<=0;carry(2)<=1; -第二步

count(2)<=1; -第三步

故从011变为010,再变为100。