目录

寄存器的设计:

多位寄存器:

多位寄存器的VHDL描述:

移位寄存器:

串进并出的移位寄存器的VHDL描述:

寄存器的设计:

多位寄存器:

一个D触发器就是一位寄存器,如果需要多位寄存器,就要用多个D触发器构成。

多位寄存器的VHDL描述:

Entity reg is

generic( n: natural :=4 ); --实体类属中的常数

port ( D: in std_logic_vector(n-1 downto 0);

clock, reset : in std_logic;

Q: out std_logic_vector (n-1 downto 0) );

End reg ;

Architecture behav of reg is

Begin

process(clock, reset)

begin

if (reset=‘0’) then Q<=( others=>‘0’); --表示Q赋全‘0’

elsif rising_edge(clock) then

Q<=D;

end if;

end process;

End behav ;

移位寄存器:

我们这里讨论的是串进并出的移位寄存器,即串行输入,在时钟的边沿移位进寄存器,形成并行输出

串进并出的移位寄存器的VHDL描述:

Entity sipo is

generic( n : natural :=8);

port ( a : in std_logic ;

q: out std_logic_vector(n-1 downto 0);

clk : in std_logic );

End sipo;

Architecture behav of sipo is

Begin

process(clk)

variable reg : std_logic_vector(n-1 downto 0);

begin

if rising_edge(clk) then

reg : = reg ( n-2 downto 0) & a ; --左移移位寄存器;

-- reg : = a & reg (n-1 downto 1); 右移移位寄存器

end if ;

q<= reg ;

end process;

End behav;

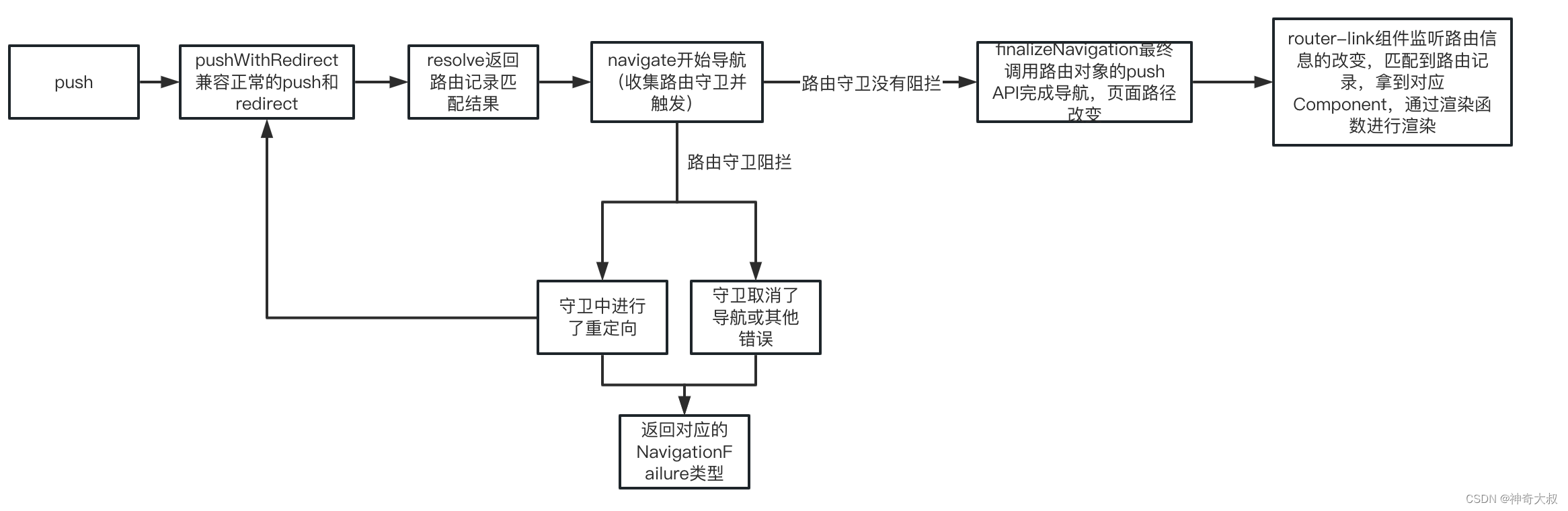

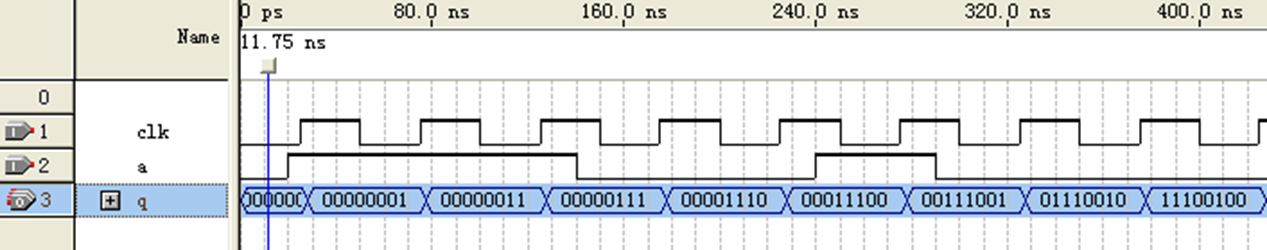

输入8位数据11100100,从仿真波形可以看出,8位数据是从低位左移存储到寄存器中的。

输入8位数据11100100,从仿真波形可以看出,8位数据是从低位左移存储到寄存器中的。