int和unsigned

在 Verilog-2001 中,没有 int 和 unsigned 这样的数据类型。这些关键字是 SystemVerilog 的特性,而不是 Verilog-2001 的一部分。

Verilog-2001 的数据类型

在 Verilog-2001 中,支持的数据类型主要包括以下几种:

1. 基本数据类型

-

reg:- 用于存储组合逻辑或时序逻辑中的值。

- 可以定义为标量(

reg a;)或向量(reg [31:0] data;)。

-

wire:- 用于表示连续赋值信号(如连线)。

- 也可以定义为标量或向量。

-

integer:- 一个 32 位的有符号整数类型,通常用于仿真中的循环计数器等。

- 示例:

integer i;

-

real:- 表示浮点数,主要用于仿真,不能综合。

- 示例:

real r = 3.14;

-

time:- 用于存储时间值,主要用于仿真。

- 示例:

time t;

2. 向量和数组

-

向量声明:

- 支持定义多位的信号,例如

reg [7:0] data;。 - 可以是有符号或无符号的(默认是无符号)。

- 支持定义多位的信号,例如

-

数组声明:

- 数组可以基于

reg或wire定义,但只能是一维的。 - 示例:

reg [7:0] mem [0:255];定义了一个 256 个元素的 8 位寄存器数组。

- 数组可以基于

3. 用户定义的类型

- 在 Verilog-2001 中,不支持像 SystemVerilog 那样的复杂用户定义类型(如

typedef)。

SystemVerilog 的扩展:int 和 unsigned

如果你需要使用 int 和 unsigned 类型,说明你在使用 SystemVerilog,而不是 Verilog-2001。以下是这两个关键字的含义:

-

int:- 一个 32 位的有符号整数类型。

- 示例:

int a = -10;

-

unsigned:- 用于修饰其他整数类型,使其变为无符号。

- 示例:

int unsigned b = 4294967295; // 32 位无符号整数

总结

- Verilog-2001 不支持

int和unsigned数据类型。 - 如果你需要这些特性,必须切换到 SystemVerilog。

- 在 Verilog-2001 中,可以通过

reg、wire、integer等基本类型来实现类似的功能,但需要注意它们的行为与 SystemVerilog 的类型有所不同。

bit,localparam和parameter

在 Verilog-2001 和 SystemVerilog 中,localparam 和 parameter 都是用于定义常量的关键字,但它们的使用场景和作用范围有所不同。至于 bit,它并不是 Verilog-2001 的标准数据类型,而是 SystemVerilog 引入的一个新特性。

1. parameter

定义与用途

parameter用于定义模块中的常量值,这些值可以在模块实例化时被覆盖。- 它们主要用于定义一些可配置的参数,如延时、宽度等。

示例

module example #(parameter WIDTH=8)(input [WIDTH-1:0] in, output [WIDTH-1:0] out);

// 模块实现

endmodule

// 实例化并覆盖参数

example #(.WIDTH(16)) inst (.in(a), .out(b));

2. localparam

定义与用途

localparam是 Verilog-2001 引入的一种特殊类型的参数,其值不能在模块实例化时被修改。- 主要用于定义局部使用的常量,通常是为了提高代码的可读性和维护性。

示例

module example;

localparam DELAY = 5;

reg [31:0] count;

always @(posedge clk) begin

if (count == DELAY)

count <= 0;

else

count <= count + 1;

end

endmodule

3. bit

定义与用途

bit是 SystemVerilog 引入的数据类型,表示一个单比特(1 位)的变量,默认为无符号类型。- 它的主要优势在于简洁性和明确性,特别是在处理布尔逻辑或状态标志时非常有用。

示例

bit flag; // 等价于 reg flag;

bit [7:0] data; // 等价于 reg [7:0] data;

区别与联系

parameter vs localparam

-

可覆盖性:

parameter:可以在模块实例化时被覆盖。localparam:不能在模块实例化时被覆盖,主要用于内部使用。

-

作用范围:

parameter:可以影响模块外部的行为,因为它们可以在实例化时被修改。localparam:仅限于定义模块内部使用的常量,确保这些常量不会被外部修改。

bit 数据类型

bit是 SystemVerilog 特有的,不适用于 Verilog-2001。- 在 Verilog-2001 中,通常使用

reg来代替bit,但reg可以有多种解释(例如既可以表示寄存器也可以表示单比特),而bit更加明确地表示单比特无符号数据。

常量和数据类型

常量本身并不属于数据类型,而是属于值的范畴。它们是通过特定的数据类型来存储和表示的。换句话说,常量是指其值在定义后不能被改变的实体,而数据类型决定了这些常量(以及变量)可以存储什么样的值及如何解释这些值。

数据类型与常量的关系

- 数据类型:定义了变量或常量可以存储的数据种类、范围以及操作方式。例如,在 Verilog 中常见的数据类型包括

reg、wire、integer等。 - 常量:指那些在程序执行期间其值不会发生变化的量。可以通过不同的数据类型来定义常量,比如使用

parameter或localparam在 Verilog 中定义常量,或者使用const关键字在 SystemVerilog 中定义常量。

Verilog 中的常量定义

1. parameter

- 用于定义模块级别的常量,可以在实例化模块时被覆盖。

- 示例:

module example #(parameter WIDTH=8)(input [WIDTH-1:0] in, output [WIDTH-1:0] out); // 模块实现 endmodule

2. localparam

- 类似于

parameter,但是它的值不能在模块实例化时被修改,主要用于模块内部。 - 示例:

module example; localparam DELAY = 5; reg [31:0] count; always @(posedge clk) begin if (count == DELAY) count <= 0; else count <= count + 1; end endmodule

3. integer 和其他基本类型中的常量

- 虽然

integer是一种数据类型,但你可以将它用作常量的载体。 - 示例:

integer const_value = 10; // 这里不是真正的常量定义,仅示例说明

SystemVerilog 中的常量增强

在 SystemVerilog 中,除了支持 Verilog 的 parameter 和 localparam 外,还引入了更直接的方式定义常量:

1. const

- 可以用于定义不可更改的变量。

- 示例:

const int fixed_value = 100;

2. bit 类型的常量

- 使用

bit类型定义单比特或向量形式的常量。 - 示例:

bit flag = 1'b1; // 单比特常量 bit [7:0] byte_const = 8'hAA; // 8位向量常量

总结

- 常量:指的是值不变的实体,并不属于数据类型本身。

- 数据类型:决定常量或变量的存储形式和操作方式。

- 在硬件描述语言(如 Verilog 和 SystemVerilog)中,我们通过特定的数据类型(如

reg、wire、integer、bit等)结合parameter、localparam或const来定义常量,从而确保某些值在设计过程中保持不变,同时明确这些值的存储格式和使用方法。

Reg,wire数据类型赋值的规则

在 Verilog 中,reg 和 wire 是两种最基本的数据类型,它们的使用和赋值规则有显著的区别。以下是详细说明以及示例代码,解释哪些赋值是合法的,哪些是非法的。

1. reg 数据类型的赋值规则

特点

reg类型变量用于存储值,可以是标量(1 位)或向量(多位)。- 它的值只能在过程块(如

always块或initial块)中被赋值。 reg类型不能直接连接到连续赋值语句(assign)。

合法赋值

以下是对 reg 的合法赋值方式:

module reg_example;

reg a; // 标量 reg

reg [3:0] b; // 向量 reg

initial begin

a = 1'b1; // 标量赋值

b = 4'b1010; // 向量赋值

#10; // 延迟 10 时间单位

a = 0; // 再次赋值

b = b + 1; // 对 reg 进行操作并赋值

end

endmodule

非法赋值

以下是对 reg 的非法赋值方式:

module illegal_reg_example;

reg a;

assign a = 1'b1; // 非法:不能对 reg 使用连续赋值

endmodule

错误原因:

reg类型必须在过程块(always或initial)中赋值,不能直接用assign语句进行连续赋值。

2. wire 数据类型的赋值规则

特点

wire类型表示物理连线,用于连接模块之间的信号。- 它的值只能通过连续赋值语句(

assign)或者模块实例化端口连接来赋值。 wire类型不能在过程块(always或initial)中直接赋值。

合法赋值

以下是对 wire 的合法赋值方式:

module wire_example;

wire a; // 标量 wire

wire [3:0] b; // 向量 wire

assign a = 1'b1; // 连续赋值

assign b = 4'b1010; // 连续赋值

// 模块实例化时连接 wire

sub_module inst (.out(b), .in(a));

endmodule

module sub_module(input in, output out);

assign out = in; // 连续赋值

endmodule

非法赋值

以下是对 wire 的非法赋值方式:

module illegal_wire_example;

wire a;

initial begin

a = 1'b1; // 非法:不能在过程块中对 wire 赋值

end

endmodule

错误原因:

wire类型必须通过assign语句或模块端口连接赋值,不能在过程块中直接赋值。

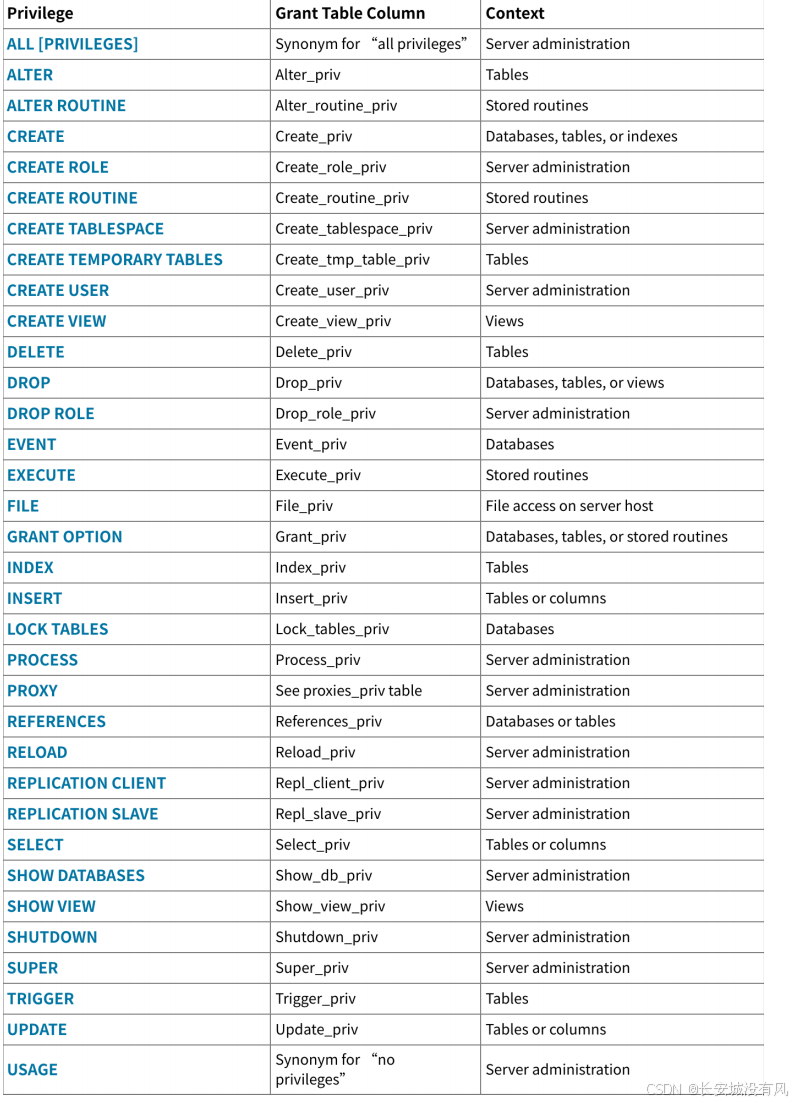

3. reg 和 wire 的区别总结

| 特性 | reg | wire |

|---|---|---|

| 用途 | 存储值 | 表示连线 |

| 赋值方式 | 在过程块(always/initial)中赋值 | 通过 assign 或模块端口连接赋值 |

| 是否需要驱动 | 不需要持续驱动 | 必须有驱动源(如 assign 或模块) |

| 默认值 | 无默认值,未初始化时为不定态 (x) | 无默认值,未驱动时为高阻态 (z) |

4. 综合示例

以下是一个综合示例,展示 reg 和 wire 的正确使用方式:

module example;

reg clk; // 时钟信号

reg reset; // 复位信号

wire [3:0] out; // 输出信号

// 连续赋值 wire

assign out = (reset == 1'b1) ? 4'b0000 : 4'b1111;

// 过程块中赋值 reg

initial begin

clk = 0;

reset = 1; // 初始复位

#10;

reset = 0; // 取消复位

end

always #5 clk = ~clk; // 生成时钟信号

endmodule

解释

reg的使用:clk和reset是reg类型,在initial和always块中赋值。

wire的使用:out是wire类型,通过assign语句根据reset的值动态计算。

- 合法性:

- 所有赋值都符合

reg和wire的规则。

- 所有赋值都符合

5. 总结

reg:- 只能在过程块(

always或initial)中赋值。 - 不能使用

assign语句赋值。

- 只能在过程块(

wire:- 只能通过

assign语句或模块端口连接赋值。 - 不能在过程块中直接赋值。

- 只能通过

理解这些规则对于正确编写 Verilog 代码非常重要,因为违反这些规则会导致编译错误或仿真行为异常。

wire和reg与输入输出端口

在 Verilog 中,模块之间的输入输出端口连接有特定的规则和方式。这些规则不仅影响到如何正确地实例化子模块,还涉及到如何将信号(如 wire 和 reg)与模块的端口进行连接。下面详细解释了这些规则,并提供了示例。

1. 输入端口 (input)

- 输入端口用于接收来自其他模块或顶层模块的信号。

- 输入端口只能连接到

wire类型或者表达式(即可以是常量、连线逻辑等),不能直接连接到reg类型变量。

示例

module top;

wire in_wire;

reg in_reg;

// 正确:使用 wire 连接到 input 端口

sub_module inst (.in(in_wire));

// 错误:尝试使用 reg 直接连接到 input 端口

// sub_module inst (.in(in_reg)); // 不允许

initial begin

in_wire = 1'b0;

#10 in_wire = 1'b1;

end

endmodule

module sub_module(input in);

// 模块实现

endmodule

2. 输出端口 (output)

- 输出端口用于向其他模块传递信号。

- 输出端口可以连接到

wire或者reg,具体取决于是否在过程块中赋值:- 如果在过程块中赋值(如

always块),则需要声明为reg类型。 - 如果通过连续赋值语句 (

assign) 赋值,则应声明为wire类型。

- 如果在过程块中赋值(如

示例

module top;

wire out_wire;

reg out_reg;

// 使用 wire 连接到 output 端口

sub_module inst1 (.out(out_wire));

// 使用 reg 连接到 output 端口

sub_module inst2 (.out(out_reg));

endmodule

module sub_module(output out);

// 如果在 always 块中赋值,则 out 应该是 reg 类型

reg temp_reg;

assign out = temp_reg; // 合法:通过 assign 赋值给 wire 类型的 output

always @(posedge clk) begin

temp_reg <= 1'b1; // 在 always 块中赋值

end

endmodule

3. 双向端口 (inout)

- 双向端口同时具有输入和输出的功能,通常用于总线通信(如三态总线)。

- 双向端口必须连接到

wire类型,因为它们需要支持高阻态 (z) 来表示未驱动状态。

示例

module top;

wire bus;

// 正确:双向端口必须连接到 wire

tristate_buffer buffer_inst (.data(bus), .enable(enable), .data_in(data_in));

endmodule

module tristate_buffer(input enable, data_in, inout data);

assign data = enable ? data_in : 1'bz; // 三态缓冲器实现

endmodule

4. 实际应用中的连接规则

wire 与端口的连接

wire可以连接到任何类型的端口(input,output,inout),这是最常见的做法。- 示例:

module top; wire in_wire; wire out_wire; sub_module inst (.in(in_wire), .out(out_wire)); endmodule module sub_module(input in, output out); // 模块实现 endmodule

reg 与端口的连接

reg只能连接到output端口,且该端口应在过程块中被赋值。- 示例:

module top; wire in_wire; reg out_reg; sub_module inst (.in(in_wire), .out(out_reg)); endmodule module sub_module(input in, output out); always @(posedge clk) begin if (in) out <= 1'b1; else out <= 1'b0; end endmodule

reg 不能直接连接到 input 或 inout 端口

reg类型的变量不能直接连接到input或inout端口,因为它们不是连续赋值模型的一部分。- 示例(错误用法):

module top; reg in_reg; // 错误:试图将 reg 直接连接到 input 端口 // sub_module inst (.in(in_reg)); // 不合法 endmodule

5. 总结

input:只能连接到wire类型或表达式,不能直接连接到reg。output:可以连接到wire或reg,但如果是过程块赋值则应使用reg,如果是连续赋值则应使用wire。inout:必须连接到wire类型,因为它们需要支持高阻态。