tips:资料来自网络,仅供学习使用。@[TOC](TPS63xxx系列DC/DC电源EMI PCB设计方案)

1.概述

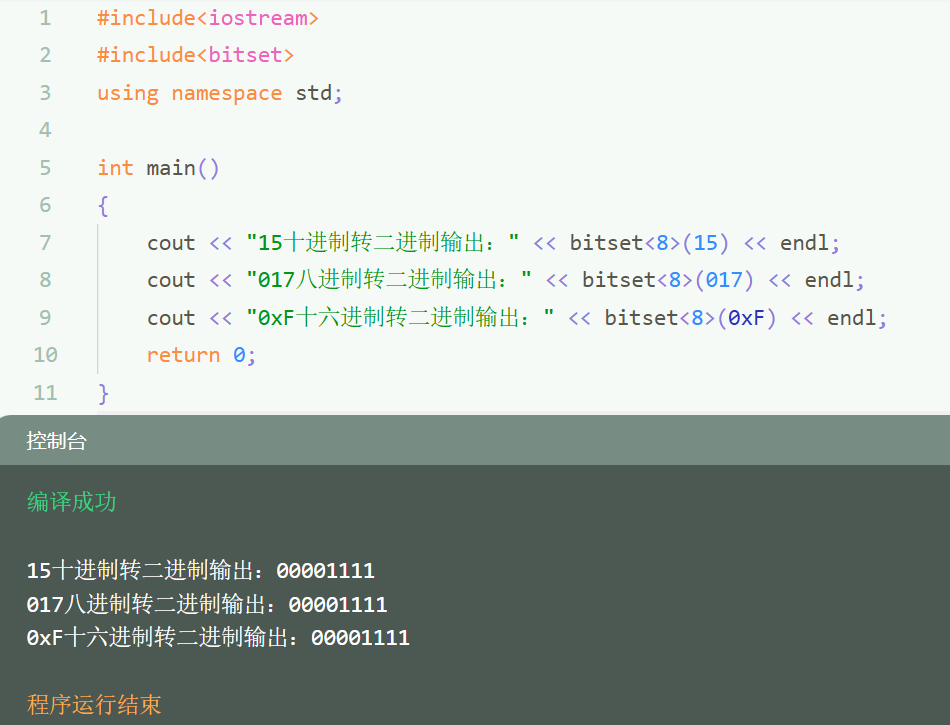

通过TPS63xxx系列DC/DC电源模块来分析降低直流/直流降压/升压转换器辐射 EMI 的来源以及相关PCB设计。

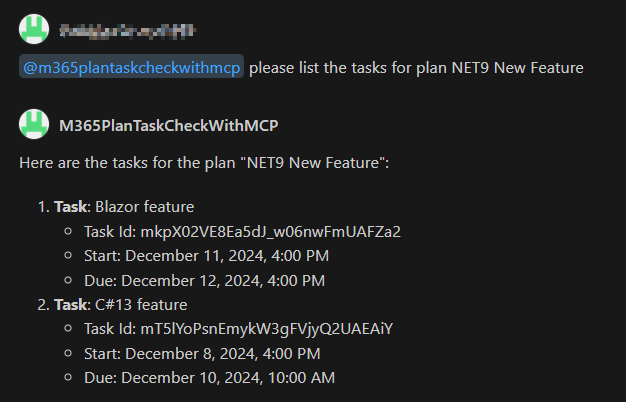

下面都以最常用的TPS63070为例说明:

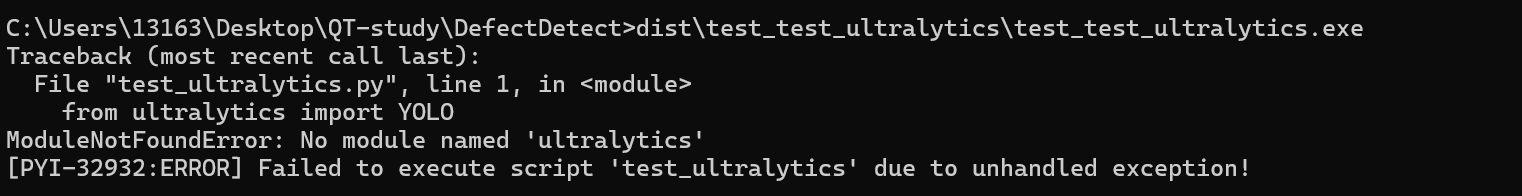

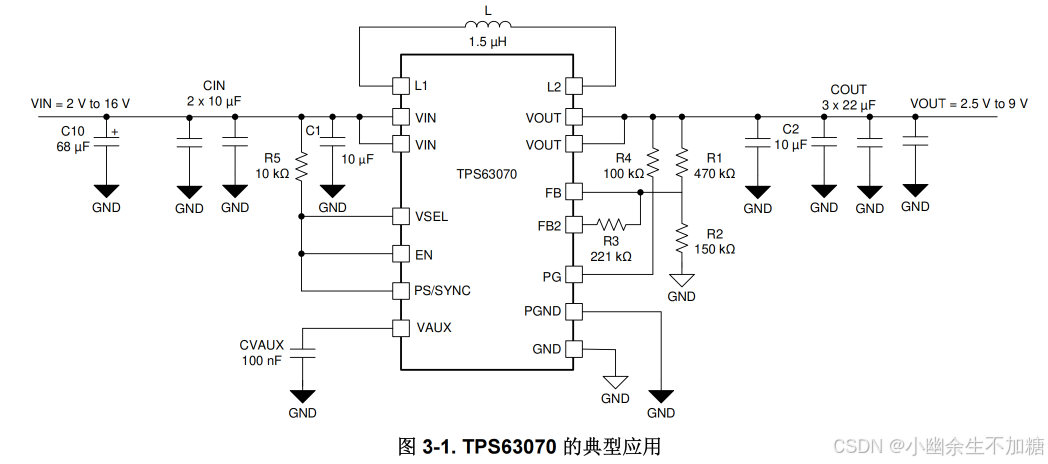

典型应用原理图:

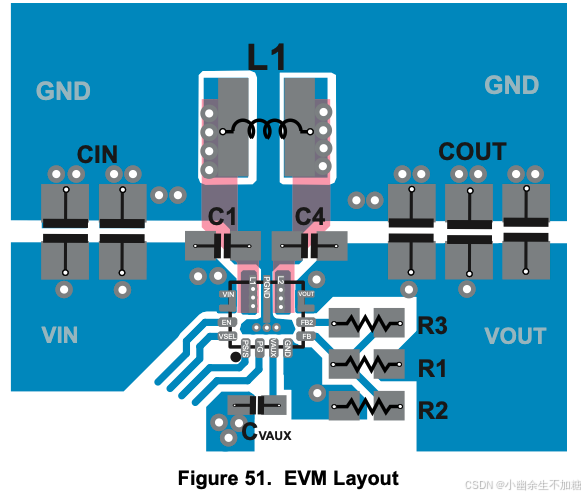

手册参考layout:

2.EMI来源

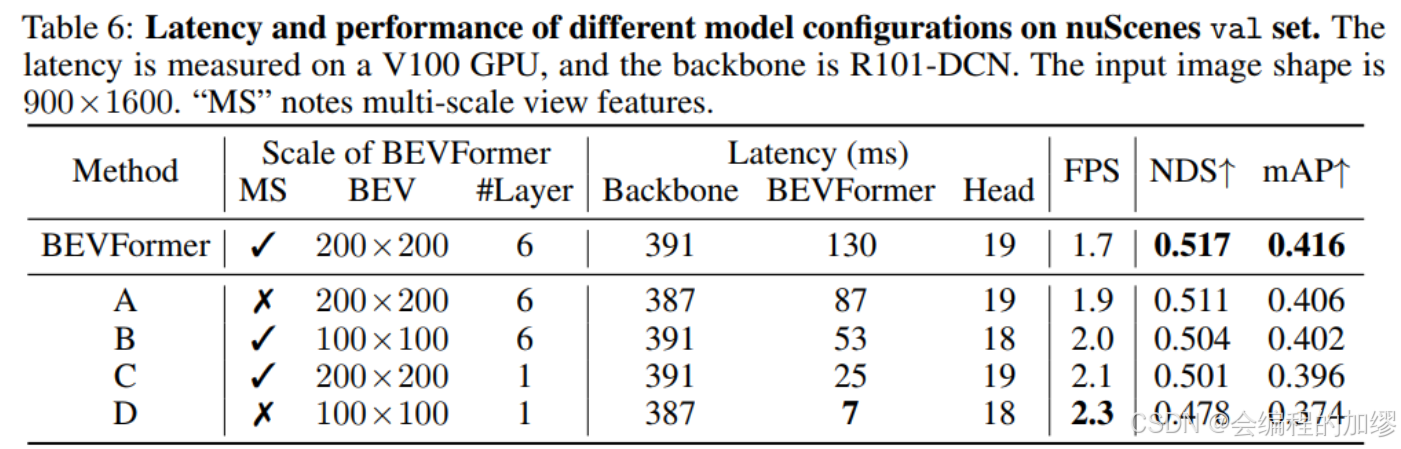

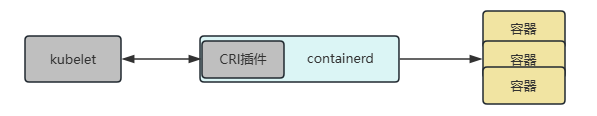

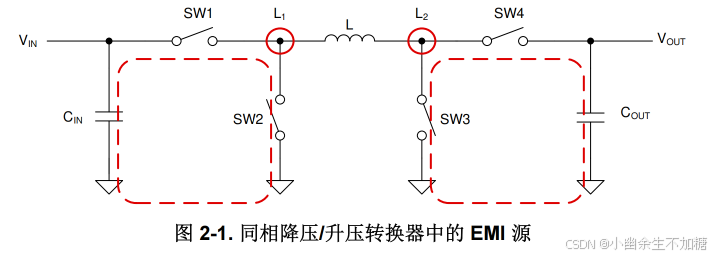

图 2-1 突出显示了同相降压/升压转换器中的主要 EMI 源。

第一个 EMI 源是位于输入电容器 (CIN) 和 SW2 之间的热回路。负责 EMI 的第二个回路是位于输出电容器 (COUT) 和 SW3 之间的回路。回路发生情况取决于转换器工作模式。在图 2-1 中,左侧回路在降压模式运行期间存在,而最右侧回路在升压模式运行期间存在。由于开关逻辑,这些回路的电流随时间的变化率 (di/dt) 会很高。考虑到电容器的等效串联电感 (ESL) 和电感器上的电压方程方程式 1,可以看出这些热回路会产生不需要的电压 (vL)。

开关节点 L1 和 L2 是另一个 EMI 源。根据运行模式(L1 表示降压,L2 表示升压),这些节点的电压随时间的变化率 (dv/dt) 会很高。电压的变化会在电容器中产生不需要的电流,如方程式 2 所示。请记住,电感器绕组之间会产生电容,可能发生寄生电流 (i2C)。

除了电感器的寄生电容,节点和接地层之间还存在另一个电容。该电容由方程式 3 描述,在很大程度上受到节点所在的层与最近的接地层之间的距离 (d) 以及平行板 (A) 区域的影响。ε0 和 εr 是自由空间的介电常数

(ε0=8.85pF/m) 和两个板之间介质的相对介电常数。

以下部分将介绍经测试可减少辐射的解决方案。所提议的解决方案伴随着可证明其有效性的测量。此类测量是根据节 7 中引用的 CISPR 16-2-3 标准和规定进行的。

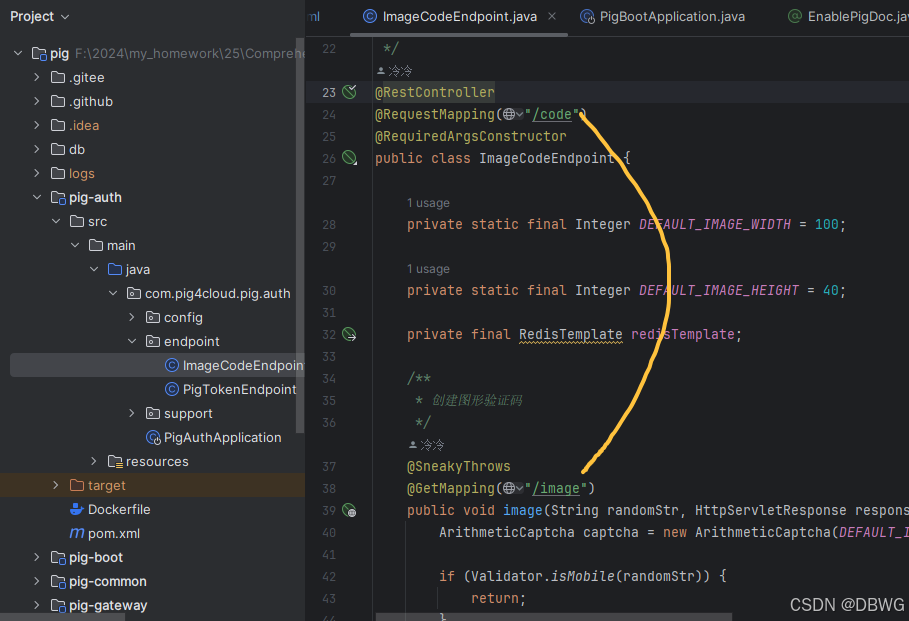

3.PCB布局分析及优化

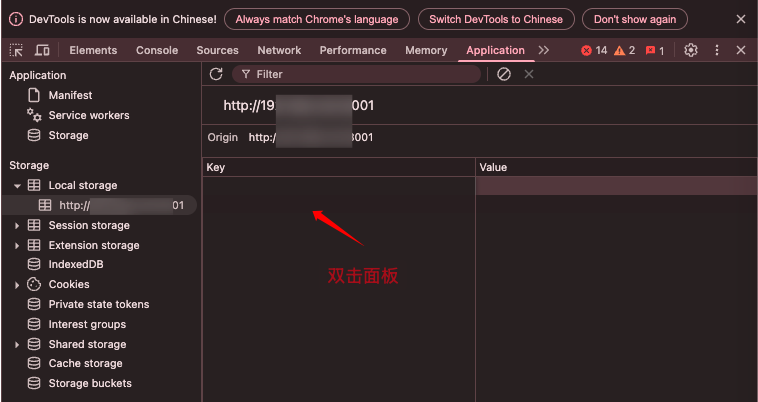

图 3-1 所示为 TPS63070 典型应用的电路。本应用手册中使用了此电路。初始 PCB 布局概念是德州仪器 (TI) 针对已构建 PCB 建议的 Webench 布局。

请注意,Webench 布局并未针对卓越 EMI 性能进行优化,而是针对放置不同尺寸组件的能力进行了优化。

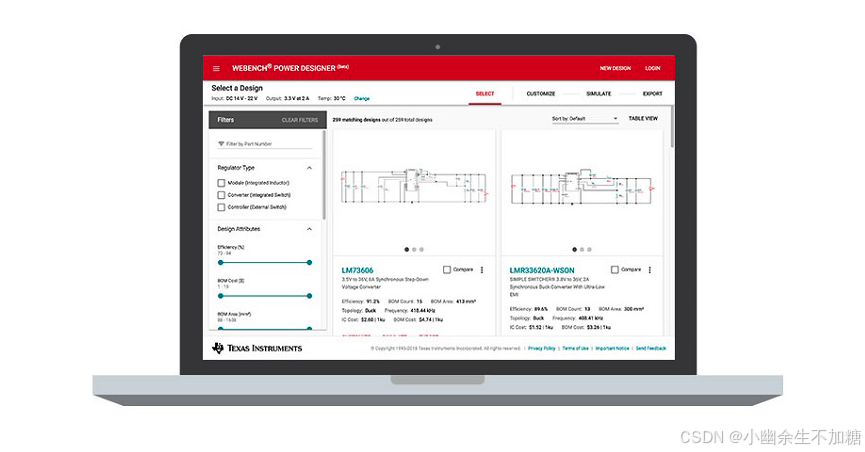

WEBENCH是美国国家半导体推出的一款功能非常强大的在线设计和仿真工具,可以对电源、LED、放大器、滤波器、音频、接口、无线以及信号路径进行设计与仿真。

做一些TI电源的仿真特别好用。

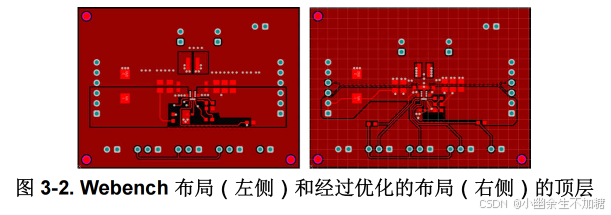

Webench PCB 布局是一种双层方法。除电感器端口之外的所有平面都保留在顶层。底层由电感器端子及输入和输出平面组成。可对 Webench 布局进行优化以提高辐射性能,如下所示:

• 最大限度地减小热平面:对应于输入、输出、电感器和其他组件连接的网络的面积应在设计允许的范围内尽可能小。最大面积应分配给接地层。

• 将布线完全保留在一个层上:尽可能避免在布线中间的层之间交叉。此过程减少了过孔数量并降低了整体平面电感。

图 3-2 所示为 Webench 布局(左侧)和经过优化的布局(右侧)的顶层。它突出显示了极小的平面和缺乏串扰。

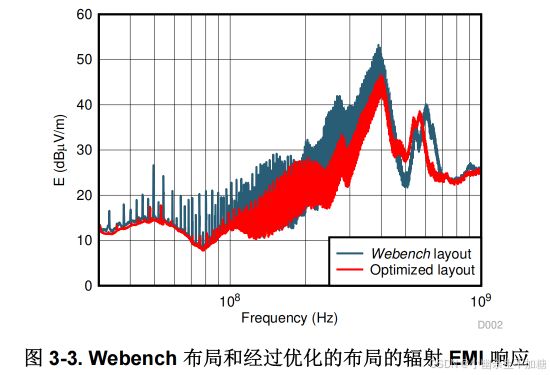

图 3-3 所示为上述改进的优势。这两种测量方法之间的差异非常明显并且很容易看出。从数字角度而言,这种差异在严重受影响的频率下会高达 10dB。

4.办层优化

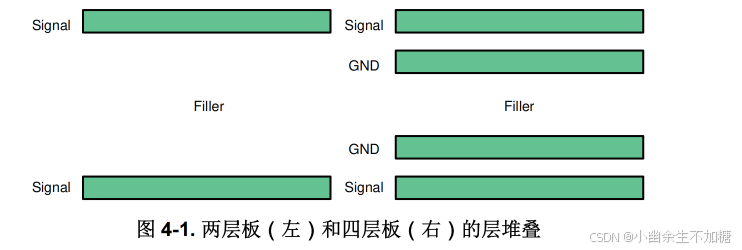

可最大限度地减小辐射的一种常用设计解决方案采用的是四层板。在现有的顶层和底层附近添加两个接地层可显著提高 EMI 性能。新的接地层由填充材料隔开,并尽可能靠近顶层和底层。通过添加接地层,返回电流形成的环路面积显著减少。因此,与两层解决方案相比,减少的环路面积能够更好地抵消磁通。

图 4-1 所示为两层板(左)和四层板(右)的层堆叠。两个额外的接地层可显著降低板之间产生的寄生电容。之所以能减少这种电容,是因为信号层和 GND 层之间的距离被尽可能缩短。如先前在方程式 3 中所述,层间距离与两个板之间出现的电容成反比。

请注意,两个信号层之间的距离在两种情况下都保持不变。

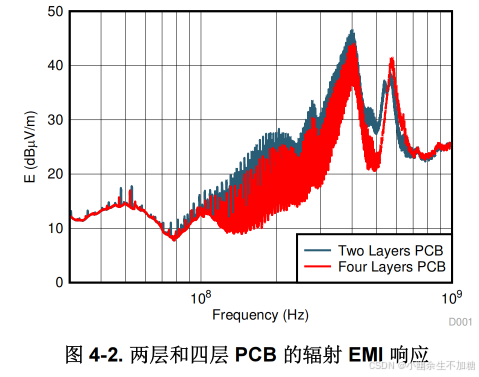

图 4-2 中突出显示了四层板带来的影响。总体而言,变换到四层 PCB 可提高辐射性能。在极端的情况下,辐射场的减少在 4dB 到 10dB 之间变化。

5.机壳地加电容

从天线理论的角度来看,电缆只不过是一个辐射体。转换器所在的机箱或外壳可作为该辐射体的参考平面。电缆和机箱之间的电势差是驱动此天线的电压。由于存在这种现象,外部电缆(如用于连接电源的电缆)会是主要的辐射源。为了更大限度地减少这些辐射,必须控制和减小前面提及的电势差。一个很好的方法是在机箱和连接到潜在辐射体的 PCB 引脚之间提供高频低阻抗连接。

为了将此原理应用于 TPS63070 转换器 PCB,底部平面已被中性机箱接地层所取代。高频电容器已用于将这个新接地层连接到输入端、输出端和地平面。这样,就为高频信号提供了低阻抗路径。

请注意,这些电容器应尽可能靠近 PCB 上的电缆端接放置。这样,我们便可确保机箱接地层和连接平面之间的差处于极低水平。

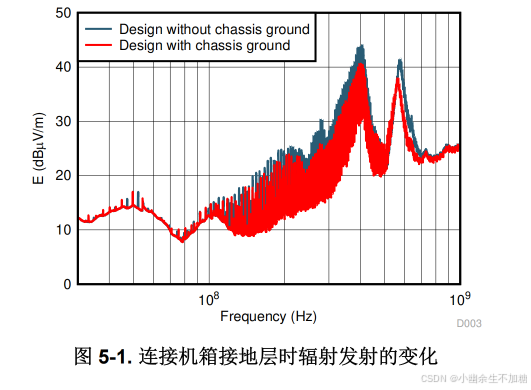

图 5-1 所示为此解决方案对于整体设计的好处。辐射场在所有频率下都已减小,而且没有做出重大取舍。通过实

施该解决方案,可将辐射发射额外降低 5dB。