今天,我们着重理解一些概念。依靠死记硬背去理解知识点,是不长久的,必须深刻理解知识点的精髓,才能长久记忆。

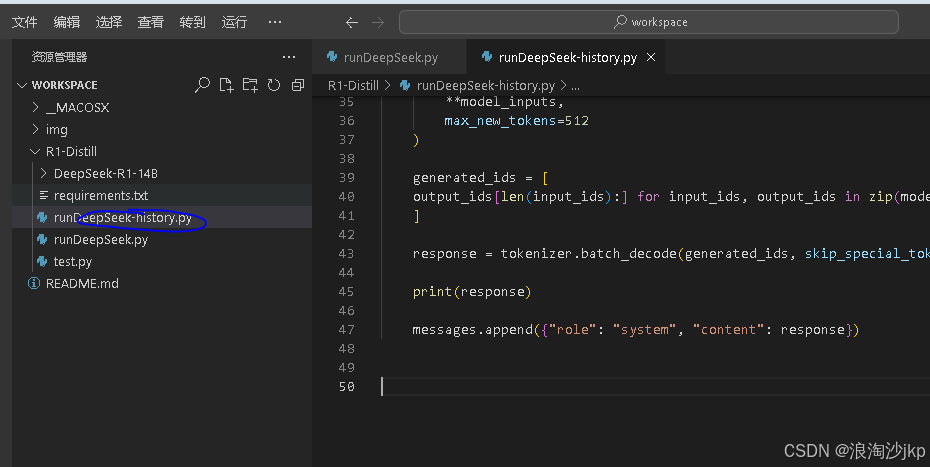

先看如下的代码:

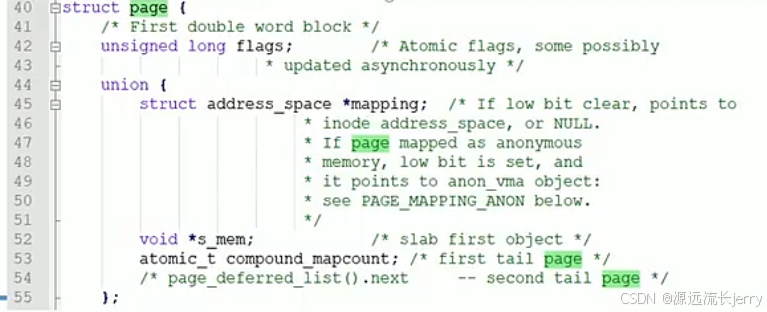

property a2b_p; //描述属性

@(posedge clk) $rose(tagError) |-> ##[2:4] $rose(tErrorBit);

endproperty

a2b_a: assert property(a2b_p); //assert property SVA的关键字表示并发断言

在SystemVerilog断言(SVA)中,两个表达式的区别如下:

-

语法正确性:

-

@(posedge sclk) $rose(a) |-> [2:4] $rose(b);

此表达式存在语法错误。SVA要求时序延迟必须使用##操作符,而[2:4]缺少##,不符合标准语法。工具可能报错或无法正确解析。 -

@(posedge sclk) $rose(a) |-> ##[2:4] $rose(b);

此表达式语法正确。##[2:4]表示在触发后的第2到第4个时钟周期内任意一个周期检查$rose(b)。

-

-

语义含义:

-

第二个表达式明确表示:当 <

-