文章目录

- 1. 概述

-

- 1.1 时钟系统

- 1.2 实验目的

- 2. 代码的配置

-

- 2.1 时钟配置

- 2.2 FTM模块配置

- 2.3 输出引脚配置

- 2.4 API函数调用

1. 概述

1.1 时钟系统

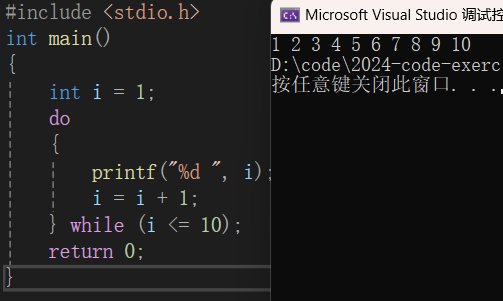

FTM的CPU接口时钟为SYS_CLK,在RUN模式下最高80MHz。模块的时钟结构如下图所示。

从上图中可以看出,FTM模块的功能时钟为SYS_CLK,计数器的时钟源可以来源于三条路:

- SYS_CLK

- 固定时钟

- 外部时钟

此处需要注意,虽然外部时钟源的可选范围较广,但是配置工具提示,其值不可超过SYS_CLK的4分频,在周期中断的文章中已经使用了系统时钟作为时钟源,本次实验使用外部晶振的分频时钟作为时钟源。外部晶振8MHz,分频系数为1,所以FTM的输入时钟为8MHz。

1.2 实验目的

本次实验,通过FTM0在CH0上输出一个频率为1KHz 占空比为50%的PWM波形,并通过API函数调整PWM波形的占空比。

2. 代码的配置

2.1 时钟配置

本次实验仍然运行在RUN模式下,系统时钟80MHz,系统的时钟配置此处不再赘述。

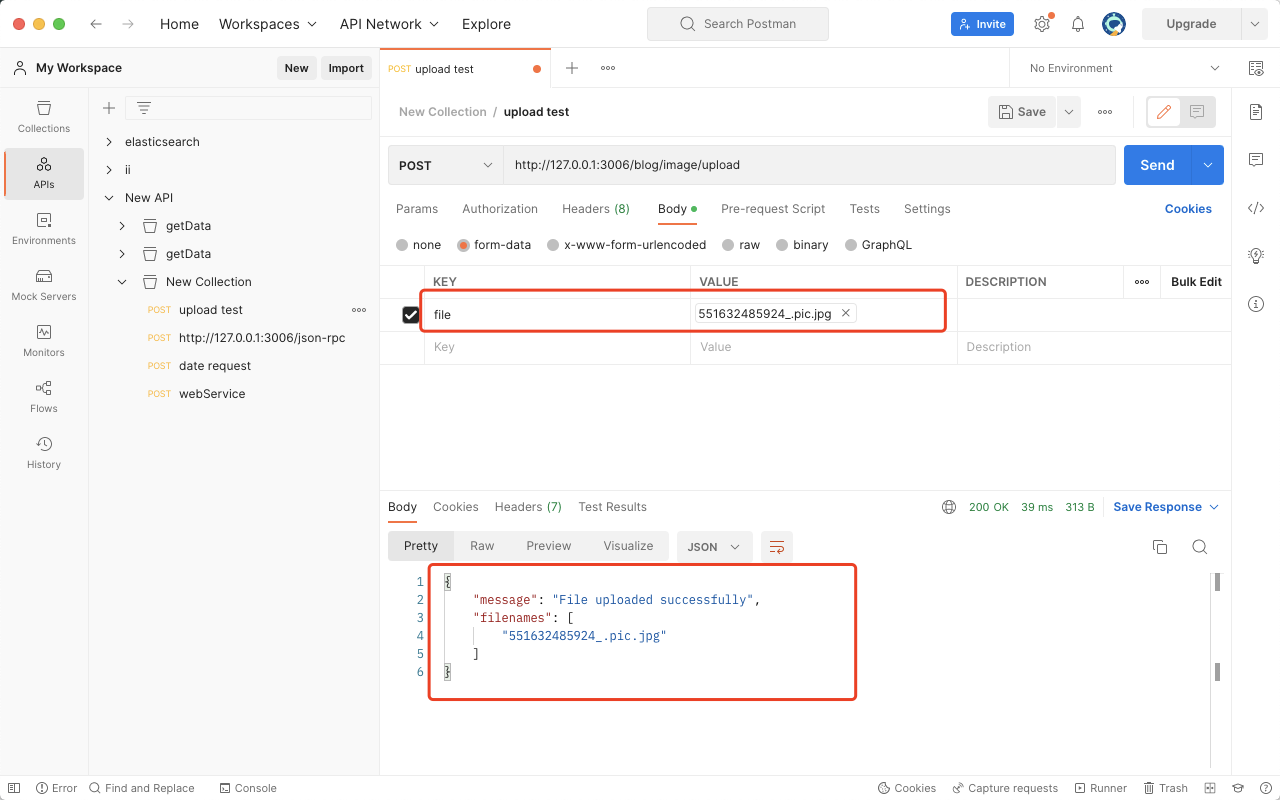

PCC部分的配置如上述需要配置为功能时钟为8MHz的晶振时钟源。如下图所示。

2.2 FTM模块配置

此处配置分为两个部分,第一个部分为模块的初始化,具体配置如下:

第二个部分为输出通道配置,具体配置如下:

此处由配置工具来设置PWM的频率,这里需要注意配置生成的周期计数值是否符合预期,也就是PWM的分辨率问题