目录

一、序言

二、时序约束概览

2.1 约束五大类

2.2 约束功能简述

2.3 跨时钟域约束

三、时序约束规范

3.1 时序约束顺序

3.2 约束的优先级

四、约束示例

4.1 设计代码

4.2 时序结果

4.2.1 create_clock

4.2.2 create_generated_clock

4.2.3 Rename_Auto-Derived_clock

4.2.4 set_clock_latency

4.2.5 set_clock_uncertainty

4.2.6 set_clock_groups

4.2.7 set_clock_sense

4.2.8 set_input_jitter

4.2.9 set_system_jitter

4.2.10 set_external_delay

4.2.11 set_input_delay

4.2.12 set_output_delay

4.2.13 set_data_check

4.2.14 set_bus_skew

4.2.15 set_false_path

4.2.16 set_multicycle_path

4.2.17 set_max_delay

4.2.18 set_min_delay

4.2.19 set_case_analysis

4.2.20 group_path

4.2.21 set_disable_timing

4.2.22 set_disable_timing

一、序言

在之前的文章中,以命令为章节进行了相关的使用说明,命令彼此间是相互独立的。在本章中,将从时序约束整体的角度对这些约束进行一个使用概述,同时结合时序报告,这样有助于深入理解命令的使用。

二、时序约束概览

2.1 约束五大类

时序约束根据约束特性可分为5类:时钟特性约束,端口路径延时,时序例外约束,断言约束,其他类,具体的约束如下图

时钟特性约束:Vivado时序工具是通过时钟特性来计算时序路径要求,通过slack计算来报告设计的时序阈值。因此,必须准确的约束时钟的特性才能准确且全面地覆盖到所有时序路径。理想的时钟通过周期,相位,频率即可完整描述其特性,但实际时钟信号是通过时钟树来传播,时钟边沿可能因为噪声和硬件特性而产生延时,即时钟网络延时(clock network latency)和时钟不确定性(clock uncertainty)。时钟不确定性包括时钟抖动,相位错误,以及其他的附加不确定性,这些时钟特性都需要通过对应的时钟约束来加入。

端口约束:FPGA与外部的信号通信都是通过port来实现的,port也是FPGA的边界。因此,必须通过set_input_delay和set_output_delay来准确建模外部时延情况。

例外约束:默认情况下,时序分析的path requirement选取规则是对发起时钟和捕获时钟在公共周期内,捕获时钟的有效沿时间减去启动时钟的有效沿,setup分析取最小值,hold分析取最大值。对于一些场景则不适用该规则,如传输数据从路径的起点到终点需要设置指定的周期数进行分析,使用set_multicycle_path约束;对于一些逻辑路径不应该被分析时,则使用set_false_path路径;对于一些路径需要限制最大和最小时延,则需设置set_max_delay和set_min_delay约束。

断言约束:断言约束是作用于时序路径间的约束,不影响其他约束的优先级,也不会覆盖或者被clock groups,max delays,false paths,multicycle paths四类时序例外约束所覆盖。对于断言约束也不会影响不会影响最终的结果,可理解为人为对一些信号设置检查条件,然后报告出见检查结果。

其他类:不在上述四大类中的时序约束属于其他类,有set_case_analysis,group_path,set_disable_timing,set_max_time_borrow四类,对应的使用参见之前的时序约束命令章节

2.2 约束功能简述

2.3 跨时钟域约束

跨时钟域CDC约束用于发起时钟和捕获时钟不同的时序路径上,CDC又分为同步CDC和异步CDC,同步CDC和异步CDC取决于发起时钟和捕获时钟的关系和CDC路径上是否有时序例外约束。如果同步时钟间的CDC路径设置了false path约束是不安全的,因此被看作异步CDC路径。异步CDC路径时序可能是安全的也可能不安全,如果异步跨时钟域路径中存在同步电路来避免亚稳态时,路径是安全的。

跨时钟域路径可以通过设置set_false_path和set_clock_groups从而完全忽略,也可以通过设置set_max_delay -datapath only约束来忽略部分路径,多比特跨时钟域路径可通过set_bus_skew约束来避免捕获时钟失准。

三、时序约束规范

3.1 时序约束顺序

在约束文件XDC中设置时序约束时,按照一定的逻辑顺序进行约束可提高约束的可读性以及方便进行修改,建议按照以下顺序设置时序约束。

## 第一部分:时钟申明

# Primary clocks 使用create_clock创建主时钟

# Virtual clocks 使用create_clock创建虚拟时钟

# Generated clocks 使用create_generated_clock创建生成时钟

## 第二部分:时钟断言

# Clock Groups 使用set_clock_groups设置时钟组

# Bus Skew constraints 使用set_bus_skew时钟总线偏斜约束

# Input and output delay constraints 使用set_input_delay/set_output_delay设置输入输出端口时延

## 第三部分:设置时序例外

# False Paths 使用set_false_path设置虚假路径

# Max Delay / Min Delay 使用set_max_delay/set_max_delay设置最大、最小时延约束

# Multicycle Paths 使用set_multicycle_path设置多周期约束

## 第四部分:其他类约束

# Case Analysis 使用set_case_analysis设置案例分析约束

# Disable Timing 使用set_disable_timing设置断开时序

## 第五部分:设置物理约束3.2 约束的优先级

在时序约束中,不同约束之间存在优先级,这个需要特别注意,否则将达不到预期的约束效果

1)相同类型的约束,后者会覆盖前者,以creat_clock约束为例,实际生效的是第二条约束

create_clock -name clk1 -period 10 [get_ports clk_in1]

create_clock -name clk2 -period 11 [get_ports clk_in1]

但如果是后一条添加了-add,则两条都会生效

create_clock -name clk1 -period 10 [get_ports clk_in1]

create_clock -name clk2 -period 11 [get_ports clk_in1] -add

2)时序例外的约束优先级示例

a.下面的set_max_delay中,第一条约束的比第二条更详细,因此第一条约束生效

set_max_delay 12 -from [get_clocks clk1] -to [get_clocks clk2]

set_max_delay 15 -from [get_clocks clk1]

b. 下面的约束中,第一条约束对象为cell,并且约束更紧,第二条约束对象中from为时钟,并且里面的through不会影响优先级。因此,第一条约束覆盖第二条约束。

set_max_delay 12 -from [get_cells inst0] -to [get_cells inst1]

set_max_delay 15 -from [get_clocks clk1] -through [get_pins hier0/p0] -to [get_cells inst1]

四、约束示例

下面以包含上述所有约束的工程示例,对约束生效的方式进行解读,器件为xcku3p-ffvb676-2-i

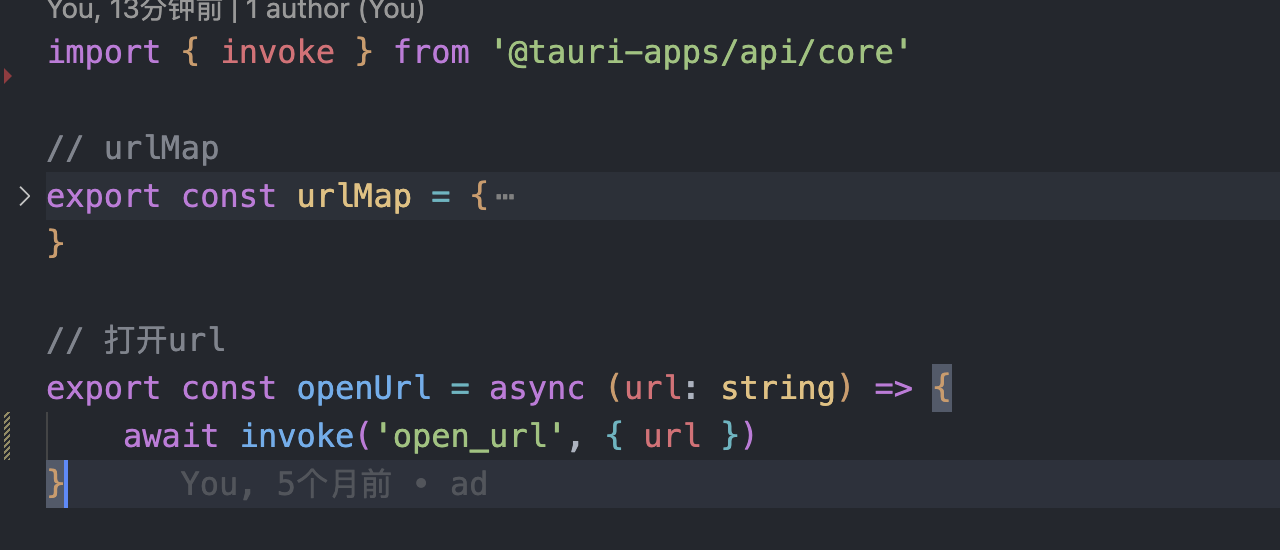

4.1 设计代码

module timing_constraint(CLKIN1,CLKIN2,clk1,clk2,CLKINSEL,CLKFBIN,rst,d,S,in,CLKFBOUT,sel,ff2_sense,

ff_clkout0_a,ff_clkout0_b,ff_clk1_a,ff_clk2,bus_clk2,GE,clr,ff2_timeborrow,ff_case2);

input CLKIN1,CLKIN2,clk1,clk2,CLKINSEL,CLKFBIN,rst,d,S;

input [4:0] in;

output CLKFBOUT;

input sel;

wire mux_n;

reg mux,ff1_sense;

output reg ff2_sense;

output reg ff_clkout0_a,ff_clkout0_b;

reg ff_clkout0;

output reg ff_clk1_a,ff_clk2;

reg ff_clk1;

reg [4:0] bus;

output reg [4:0] bus_clk2;

wire [4:0] bus_c;

input GE,clr;

output reg ff2_timeborrow;

reg ff1_timeborrow;

reg ff_case1;

output reg ff_case2;

PLLE2_ADV #(

.BANDWIDTH("OPTIMIZED"), // OPTIMIZED, HIGH, LOW

.CLKFBOUT_MULT(8), // Multiply value for all CLKOUT, (2-64)

.CLKFBOUT_PHASE(90