简介

介绍

JESD204 PHY IP核实现了JESD204的物理接口,简化在发送和接收核心之间共享串行收发器信息通道。此内核一般不单独使用,只能与JESD204或JESD204C内核结合使用。

特性

根据JESD204B和JESD204C草案设计

支持1至12lane配置

JESD204 IP支持1至12lane,JESD204C支持1至8lane

支持Subclass 0、1、2

提供物理层支持

支持TX和RX IP共享传输通道

可以通过AXI接口控制DRP来操控QPLL和传输路径

AXI接口速率切换

AXI寄存器可以控制选择传输信号

CH1 概述

逻辑IP JESD204物理核心层实现

JESD204B物理接口支持7系列、UltraScale和UltraScale+设备的1至12通道以及单通道线速率在1.0至12.5Gb/s。

JESD204C物理接口支持7系列、UltraScale和UltraScale+设备的1至8通道以及单通道线速率在1.0至32Gb/s。

有关每台设备支持的具体线速率,请查阅相关手册。

JESD204 PHY核心可以配置独立的传输和接收线速率以及JESD204的版本。

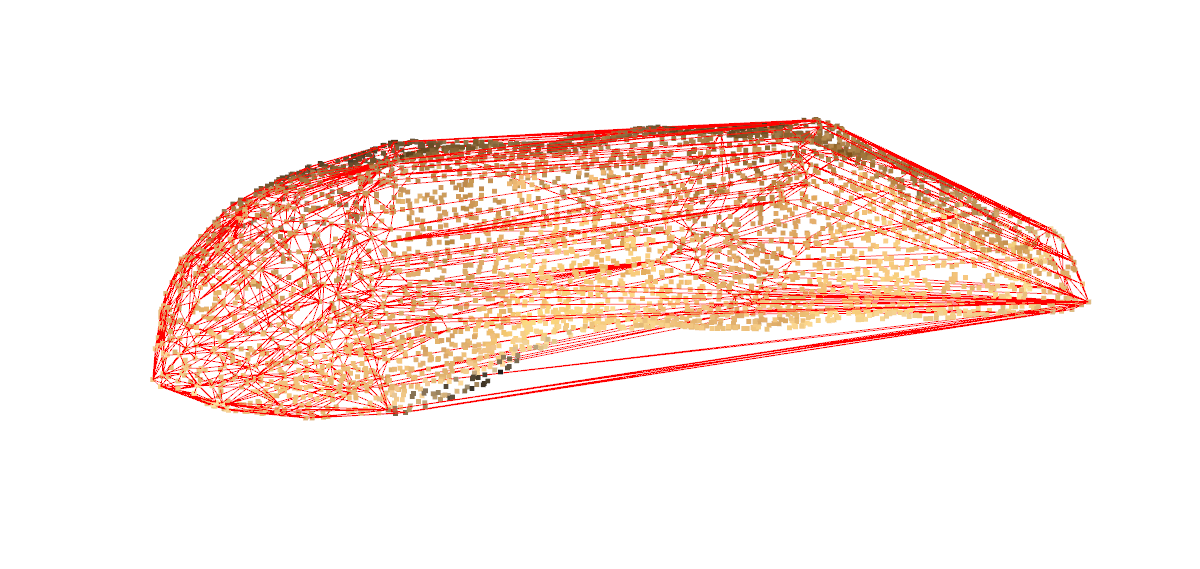

以下是实例设计中具有共享逻辑的JESD204 PHY核心

当与JESD204内核结合使用时,JESD204 PHY是进过充分验证的解决方案,此外,还提供了一个参考设计,请查阅pg066

应用

JESD204 PHY核心是JESD204和JESD204C核心的子核心,有关的应用信息查看JESD204 IP产品指南(PG066)以及JESD204C IP产品指南(PG242),下图显示了JESD204或JESD204C设计中使用JESD204 PHY

JESD204 PHY允许实现复杂收发器和JESD204/JESD204C核心共享,下图取自Vivado IP集成器,显示了三个JESD204 PHY IP和一个JESD204C和之间共享收发器PHY。

CH2 产品说明书

本章详细介绍了JESD204 PHY核心的资源 利用率和端口

性能和资源利用率

性能和资源利用率详情请见性能和资源利用率网页

端口描述

本节包含JESD204 PHY端口的详细信息

下表详细说明了当核心配置为JESD204或JESD204C时可用的端口,以及当核心配置用于核心或示例中的共享逻辑时可用的接口。

时钟和复位端口

JESD204 PHY IP会根据器件以及高速链路和协议的不同,展示不同的端口。

表2-1:共用时钟端口-JESD204B配置(共享逻辑在核内)

| 信号名 | I/O | 描述 |

|---|---|---|

| txoutclk | O | 传输层的输出时钟,时钟源来自TX master通道,可以在JESD PHY IP的GUI中设置 |

| rxoutclk | O | 传输层的输出时钟,时钟源来自RX master通道,可以在JESD PHY IP的GUI中设置 |

| gt_powergood | O | 用来表示传输层的能量就绪,当驱动配置后输出,仅仅用于U和U+系列 |

| tx_core_clk | I | 用于驱动传输物理层的txusrclk2,在U和U+设备中,txoutclk可以被用来驱动此端口 |

| rx_core_clk | I | 用于驱动传输物理层的rxusrclk2,在U和U+设备中,rxoutclk可以被用来驱动此端口 |

| drp_clk | I | DRP的动态配置时钟 |

| cpll_refclk | I | 物理传输层的通道PLL的参考时钟 |

| qpll_refclk | I | 7系列中Quad Common PLL的参考时钟 |

| qpll0/1_refclk | I | U和U+系列中Quad Common PLL的参考时钟 |

| commonM_qpll_clk_out | O | 来自QPLL的时钟输出,仅仅在QPLL使能的时候才显示 |

| commonM_qpll_refclk_out | O | 来自QPLL的参考时钟输入,仅仅在QPLL使能的时候才显示 |

| commonM_qpll_lock_out | O | 来自QPLL的Lock信号输出,仅仅在QPLL使能的时候才显示 |

| commonM_pll0_clk_out | O | 来自PLL的时钟输出,仅在PLL0使能时才显示 |

| commonM_pll0_refclk_out | O | 来自PLL的参考时钟输入,仅在PLL0使能时才显示 |

| commonM_pll0_lock_out | O | 来自PLL的LOCK信号输出,仅在PLL0使能时才显示 |

| commonM_pll1_clk_out | O | 来自PLL的时钟输出,仅在PLL1使能时才显示 |

| commonM_pll1_refclk_out | O | 来自PLL的参考时钟输入,仅在PLL1使能时才显示 |

| commonM_pll1_lock_out | O | 来自PLL的LOCK信号输出,仅在PLL1使能时才显示 |

| commonM_qpll0_clk_out | O | 来自QPLL的时钟输出,仅仅在QPLL0使能的时候才显示 |

| commonM_qpll0_refclk_out | O | 来自QPLL的参考时钟输入,仅仅在QPLL0使能的时候才显示 |

| commonM_qpll0_lock_out | O | 来自QPLL的Lock信号输出,仅仅在QPLL0使能的时候才显示 |

| commonM_qpll1_clk_out | O | 来自QPLL的时钟输出,仅仅在QPLL1使能的时候才显示 |

| commonM_qpll1_refclk_out | O | 来自QPLL的参考时钟输入,仅仅在QPLL1使能的时候才显示 |

| commonM_qpll1_lock_out | O | 来自QPLL的Lock信号输出,仅仅在QPLL1使能的时候才显示 |

| mmcm_locked | O | 输出指示着内部MMCM锁定,信号可以被其他IP共享,仅仅GTP设备才显示 |

表2-2:共享复位信号端口-JESD204B配置(共享逻辑在核内)

| 信号名 | I/O | 描述 |

|---|---|---|

| tx_reset_gt | I | TX信道数据路径的异步复位 |

| rx_reset_gt | I | RX信道数据路径的异步复位 |

| tx_sys_reset | I | TX信道数据路径和PLL的异步复位 |

| rx_sys_reset | I | RX信道数据路径和PLL的异步复位 |

下表列出了JESD204C配置(共享逻辑在核内)的通用时钟和重置端口。

表2-3:共享时钟端口-JESD204C配置(共享逻辑在核内)

| 信号名 | I/O | 描述 |

|---|---|---|

| txoutclk | O | 传输层的输出时钟,时钟源来自TX master通道,可以在JESD PHY IP的GUI中设置 |

| rxoutclk | O | 传输层的输出时钟,时钟源来自RX master通道,可以在JESD PHY IP的GUI中设置 |

| gt_powergood | O | 用来表示传输层的能量就绪,当驱动配置后输出,仅仅用于U和U+系列 |

| tx_core_clk | I | 用于驱动传输物理层的txusrclk2,在U和U+设备中,txoutclk可以被用来驱动此端口 |

| rx_core_clk | I | 用于驱动传输物理层的rxusrclk2,在U和U+设备中,rxoutclk可以被用来驱动此端口 |

| drp_clk | I | DRP的动态配置时钟 |

| cpll_refclk | I | 物理传输层的通道PLL的参考时钟 |

| qpll_refclk | I | 7系列中Quad Common PLL的参考时钟 |

| qpll0/1_refclk | I | U和U+系列中Quad Common PLL的参考时钟 |

| commonM_qpll0_clk_out | O | 来自QPLL的时钟输出,仅仅在QPLL0使能的时候才显示 |

| commonM_qpll0_refclk_out | O | 来自QPLL的参考时钟输入,仅仅在QPLL0使能的时候才显示 |

| commonM_qpll0_lock_out | O | 来自QPLL的Lock信号输出,仅仅在QPLL0使能的时候才显示 |

| commonM_qpll1_clk_out | O | 来自QPLL的时钟输出,仅仅在QPLL1使能的时候才显示 |

| commonM_qpll1_refclk_out | O | 来自QPLL的参考时钟输入,仅仅在QPLL1使能的时候才显示 |

| commonM_qpll1_lock_out | O | 来自QPLL的Lock信号输出,仅仅在QPLL1使能的时候才显示 |

| mmcm_locked | O | 输出指示着内部MMCM锁定,信号可以被其他IP共享,仅仅GTP设备才显示 |

表2-4:共享复位信号端口-JESD204B配置(共享逻辑在核内)

| 信号名 | I/O | 描述 |

|---|---|---|

| tx_reset_gt | I | TX信道数据路径的异步复位 |

| rx_reset_gt | I | RX信道数据路径的异步复位 |

| tx_sys_reset | I | TX信道数据路径和PLL的异步复位 |

| rx_sys_reset | I | RX信道数据路径和PLL的异步复位 |

表2-5:共享时钟端口-JESD204B配置(共享逻辑在例程)

| 信号名 | I/O | 描述 |

|---|---|---|

| tx_core_clk | I | 用于驱动传输物理层的txusrclk2,在U和U+设备中,txoutclk可以被用来驱动此端口 |

| rx_core_clk | I | 用于驱动传输物理层的rxusrclk2,在U和U+设备中,rxoutclk可以被用来驱动此端口 |

| drp_clk | I | DRP的动态配置时钟 |

| tx_usrclk | I | TXUSRCLK输入给传输层,仅仅在GTP才有 |

| rx_usrclk | I | RXUSRCLK输入给传输层,仅仅在GTP才有 |

| qpll0/1_refclk | I | U和U+系列中Quad Common PLL的参考时钟 |

| commonM_qpll_clk_in | I | QPLL的时钟输入,一直显示,仅用于7系列器件 |

| commonM_qpll_refclk_in | I | QPLL的参考时钟输入,一直显示,仅用于7系列器件 |

| commonM_pll0_clk_in | I | 来自PLL0的时钟输入,仅仅在PLL0使能的时候才显示 |

| commonM_pll0_refclk_in | I | 来自PLL0的参考时钟输入,仅仅在PLL0使能的时候才显示 |

| commonM_pll1_clk_in | I | 来自PLL1的时钟输入,仅仅在PLL1使能的时候才显示 |

| commonM_pll1_refclk_in | I | 来自PLL1的参考时钟输入,仅仅在PLL1使能的时候才显示 |

| commonM_qpll0_clk_in | I | 来自QPLL0的时钟输入,仅仅在QPLL0使能的时候才显示 |

| commonM_qpll0_refclk_in | I | 来自QPLL0的参考时钟输入,仅仅在QPLL0使能的时候才显示 |

| commonM_qpll1_clk_in | I | 来自QPLL1的时钟输入,仅仅在QPLL1使能的时候才显示 |

| commonM_qpll1_refclk_in | I | 来自QPLL1的参考时钟输入,仅仅在QPLL1使能的时候才显示 |

表2-6:共享复位端口-JESD204B(共享逻辑在例程)

| 信号名 | I/O | 描述 |

|---|---|---|

| tx_reset_gt | I | TX信道数据路径的异步复位 |

| rx_reset_gt | I | RX信道数据路径的异步复位 |

| tx_sys_reset | I | TX信道数据路径和PLL的异步复位 |

| rx_sys_reset | I | RX信道数据路径和PLL的异步复位 |

| qpll_reset_out | O | 从传输逻辑到common Block,仅仅在QPLL选择时出现 |

| qpll0_reset_out | O | 从传输逻辑到common Block,当QPLL0被选择或者AXI4-lite管理接口被使能并且最少一个通道使用了QPLL0,此端口只被用于U或者U+系列器件 |

| qpll1_reset_out | O | 从传输逻辑到common Block,当QPLL1被选择或者AXI4-lite管理接口被使能并且最少一个通道使用了QPLL1,此端口只被用于U或者U+系列器件 |

| commonM_pll0_reset_out | O | 从传输层逻辑到common Block,仅仅在PLL0被使能的时候出现 |

| commonM_pll1_reset_out | O | 从传输层逻辑到common Block,仅仅在PLL1被使能的时候出现 |

| mmcm_reset | O | 从传输层输出给MMCM的复位,仅仅出现在GTP收发器上 |

| mmcm_lock | I | MMCM输出来指示时钟已经锁定,仅仅出现在GTP收发器上 |

下表列出了JESD204C配置的通用时钟和复位端口

表2-7:共享时钟-JESD204C配置(共享逻辑在例程)

| 信号名 | I/O | 描述 |

|---|---|---|

| drp_clk | I | DRP的动态配置时钟 |

| cpll_refclk | I | 给传输通道PLL的参考时钟 |

| qpll0/1_refclk | I | U和U+系列中Quad Common PLL的参考时钟 |

| tx_core_clk | I | 用于驱动传输物理层的txusrclk2,频率等于线速率/66 |

| rx_core_clk | I | 用于驱动传输物理层的rxusrclk2,频率等于线速率/66 |

| commonM_qpll0_clk_in | I | 来自QPLL0的时钟输入,仅仅在QPLL0使能的时候才显示 |

| commonM_qpll0_refclk_in | I | 来自QPLL0的参考时钟输入,仅仅在QPLL0使能的时候才显示 |

| commonM_qpll1_clk_in | I | 来自QPLL1的时钟输入,仅仅在QPLL1使能的时候才显示 |

| commonM_qpll1_refclk_in | I | 来自QPLL1的参考时钟输入,仅仅在QPLL1使能的时候才显示 |

表2-8:共享复位端口-JESD204C配置(共享逻辑在例程)

| 信号名 | I/O | 描述 |

|---|---|---|

| tx_reset_gt | I | TX信道数据路径的异步复位 |

| rx_reset_gt | I | RX信道数据路径的异步复位 |

| tx_sys_reset | I | TX信道数据路径和PLL的异步复位 |

| rx_sys_reset | I | RX信道数据路径和PLL的异步复位 |

| qpll0_reset_gt | O | 来自传输层给到QPLL0 common block的复位逻辑,当QPLL0被选中或者AXI-lite管理接口被使能并且最少一个通道用了QPLL0或者QPLL1 |

| qpll1_reset_out | O | 来自传输层给到QPLL1 common block的复位逻辑,当QPLL1被选中或者AXI-lite管理接口被使能并且最少一个通道用了QPLL0或者QPLL1 |

发送端口

在传输核的传输接口可用位宽取决于定制IP时数据路径宽度的选择。

表2-9:发送并行数据传输接口-数据深度取决于JESD204B的设置

| 信号名 | I/O | 时钟域 | 描述 |

|---|---|---|---|

| gtN_txdata[31:0] | I | tx_core_clock | 来自TX核的数据。N=0…[Lanes-1] |

| gtN_txcharisk[3:0] | I | tx_core_clock | 来自TX核的K码。N=0…[Lanes-1] |

| gt_prbssel[2:0] | I | tx_core_clock |

表2-10:发送并行数据传输接口-数据深度取决于JESD204C的设置

| 信号名 | I/O | 时钟域 | 描述 |

|---|---|---|---|

| gtN_txdata[63:0] | I | tx_core_clock | 来自TX核的数据。N=0…[Lanes-1] |

| gtN_txheader[3:0] | I | tx_core_clock | 来自TX核的头标志。N=0…[Lanes-1] |

| gtN_txcharisk[3:0] | I | tx_core_clock | 来自TX核的K码。N=0…[Lanes-1] |

表2-11:TX串行传输线

| 信号名 | I/O | 时钟域 | 描述 |

|---|---|---|---|

| txp_out[N:0] | O | tx_core_clock | 串行差分数据的正输出。N=[Lanes-1] |

| txn_out[N:0] | O | tx_core_clock | 串行差分数据的负输出。N=[Lanes-1] |

接收端口

在传输核的传输接口可用位宽取决于定制IP时数据路径宽度的选择。

表2-12:接收并行数据传输接口-数据深度取决于JESD204B的设置

| 信号名 | I/O | 时钟域 | 描述 |

|---|---|---|---|

| gtN_rxdata[31:0] | O | rx_core_clock | 给到RX核的数据。N=0…[Lanes-1] |

| gtN_rxcharisk[3:0] | O | rx_core_clock | 给到RX核的K码。N=0…[Lanes-1] |

| gtN_rxdisperr[3:0] | O | rx_core_clock | 显示错误给RX核。N=0…[Lanes-1] |

| gtN_rxnotintable[3:0] | O | rx_core_clock | 不在RX核心表中?N=0…[Lanes-1] |

| rxencommalign | I | rx_core_clock | 来自RX core的使能对齐码 |

表2-13:接收并行数据传输接口-数据深度取决于JESD204C的设置

| 信号名 | I/O | 时钟域 | 描述 |

|---|---|---|---|

| gtN_rxdata[63:0] | O | rx_core_clock | 来自RX核的数据。N=0…[Lanes-1] |

| gtN_rxheader[1:0] | O | rx_core_clock | 给到RX核的头标志。N=0…[Lanes-1] |

| gtN_rxblock_sync | O | rx_core_clock | 给到RX核的快对齐标志。N=0…[Lanes-1] |

| gtN_rxmisalign] | O | rx_core_clock | 给到RX核的块不匹配标志,块的头无效。N=0…[Lanes-1] |

| gtN_rxcharisk[3:0] | O | rx_core_clock | 给到RX核的K码。N=0…[Lanes-1] |

| gtN_rxdisperr[3:0] | O | rx_core_clock | 显示错误给RX核。N=0…[Lanes-1] |

| gtN_rxnotintable[3:0] | O | rx_core_clock | 不在RX核心表中?N=0…[Lanes-1] |

表2-14:接收串行数据线端口

| 信号名 | I/O | 时钟域 | 描述 |

|---|---|---|---|

| rxp_out[N:0] | O | rx_core_clock | 串行差分数据的正输入。N=[Lanes-1] |

| rxn_out[N:0] | O | rx_core_clock | 串行差分数据的负输入。N=[Lanes-1] |

发送的DEBUG接口

注意:收发器控制和状态接口中的端口必须按照相应的GT用户指南进行驱动,使用表2-15和表2-16中列出的信号可能会导致IP核的行为不可预测

收发器调试端口(提供对收发器控制和状态引脚的访问,用于调试目的,这些引脚的说明应该参考相应的收发器用户指南)

UltraScale Architecture GTH Transceivers User Guide (UG576)

7 Series FPGAs GTX/GTH Transceivers User Guide (UG476)

7 Series FPGAs GTP Transceivers User Guide (UG482)

UltraScale Architecture GTY Transceivers (UG578)

表2-15:可选的收发器调试端口(7系列器件)

表2-14:接收串行数据线端口

| 信号名 | I/O | 时钟域 | 描述 |

|---|---|---|---|

| gtN_drpaddr[8:0] | I | drp_clk | drp地址总线 |

| gtN_drpdi[15:0] | I | drp_clk | drp从FPGA逻辑端到传输端的写数据配置总线 |

不想写了 好累 还是自己慢慢看吧

![[c++进阶(八)]STL容器适配器之queue](https://i-blog.csdnimg.cn/direct/b763d72ac06f416c81bc95a6c936a188.png)