Flash 简介

Flash全名叫做Flash Memory,属于非易失性存储设备(Non-volatile Memory Device),与此相对应的是易失性存储设备(Volatile Memory Device)。关于什么是非易失性/易失性,从名字中就可以看出,非易失性就是不容易丢失,数据存储在这类设备中,即使断电了,也不会丢失,这类设备,除了Flash,还有其他比较常见的如硬盘,ROM等,与此相对的,易失性就是断电了,数据就丢失了,比如大家常用的内存,不论是以前的SDRAM,DDR SDRAM,还是现在的DDR2,DDR3等,都是断电后,数据就没了。

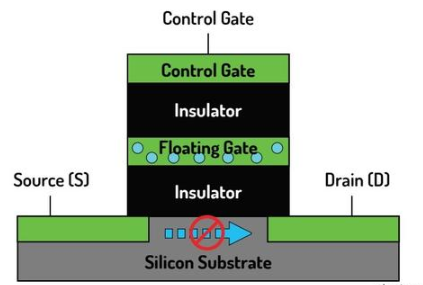

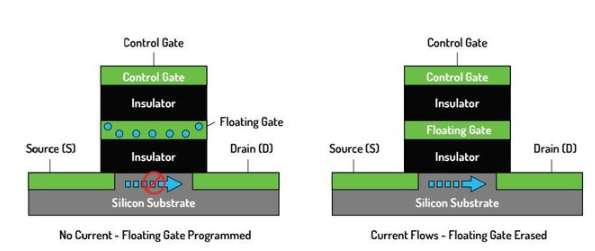

Flash的内部存储是金属-氧化层-半导体-场效晶体管(MOSFET),里面有个浮栅门(Floating Gate),是真正存储数据的单元。

数据在Flash内存单元中是以电荷(electrical charge) 形式存储的。存储电荷的多少,取决于图中的控制门(Control gate)所被施加的电压,其控制了是向存储单元中冲入电荷还是使其释放电荷。而数据的表示,以所存储的电荷的电压是否超过一个特定的阈值Vth 来表示。

FLASH的分类:功能特性分为两种:一种是NOR型闪存,以编码应用为主,其功能多与运算相关;另一种为NAND型闪存,主要功能是存储资料,如数码相机中所用的记忆卡。

关于NAND Flash 和 NOR Flash 的差别,可参考我之前的文章。

NOR Flash 和 NAND Flash 闪存详解_存储元的博客-CSDN博客

本文专注于NAND Flash。

FLASH的发展历史

1.在1984年,东芝公司的发明人Fujio Masuoka首先提出了快速闪存存储器(此处简称闪存)的概念。

2.NAND闪存由东芝公司于1989年研制,并被认为是NOR闪存的理想替代者。

3.MLC是英特尔(Intel)在1997年9月最先开发成功的

4. 3D NAND 是 2014 年由Micron 和 英特尔(Intel)联合研发的。

NAND Flash的架构

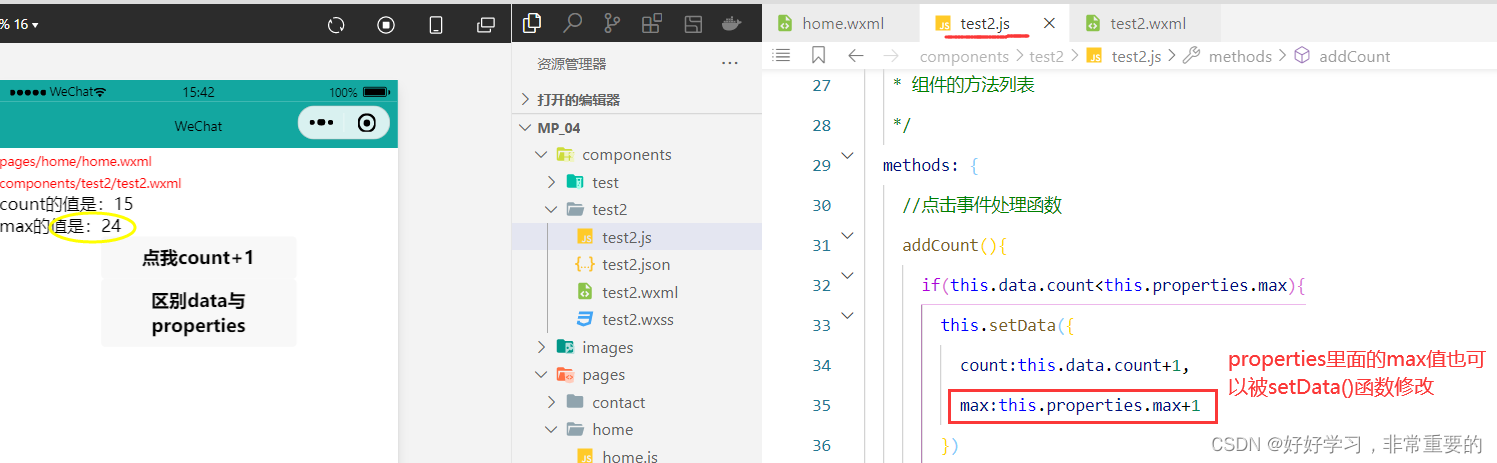

如上图所示,这是一个8Gb 50nm的SLC颗粒内部架构。

每个page有33,792个单元,每个单元代表1bit(SLC),所以每个page就是4096Byte + 128Byte(SA)。

每个Block有64个page组成,所以每个Block容量为262,114Byte + 8192Byte (SA)

page是NAND Flash上最小的读/写单位(一个page上的单元共享一根字符线Word line),块是最小的擦除单位(。不同厂牌不同型号颗粒有不同的page和block大小。

下图是个8Gb 50nm的SLC颗粒。

4KB的页尺寸,256KB的块尺寸。图中4096字节用于存储数据,另外128字节用来做管理和ECC用。

Flash 的物理学原理

经典物理学认为

物体越过势垒,有一阈值能量;粒子能量小于此能量则不能越过,大于此能

量则可以越过。例如骑自行车过小坡,先用力骑,如果坡很低,不蹬自行车也能

靠惯性过去。如果坡很高,不蹬自行车,车到一半就停住,然后退回去。

量子力学则认为

即使粒子能量小于阈值能量,很多粒子冲向势垒,一部分粒子反弹,还会有

一些粒子能过去,好象有一个隧道,称作“量子隧道(quantum tunneling)”。

可见,宏观上的确定性在微观上往往就具有不确定性。虽然在通常的情况下,隧

道效应并不影响经典的宏观效应,因为隧穿几率极小,但在某些特定的条件下宏

观的隧道效应也会出现。

1957 年,受雇于索尼公司的江崎玲於奈(Leo Esaki,1940~)在改良高频 晶体管 2T7 的过程中发现,当增加 PN 结两端的电压时电流反而减少,江崎玲於奈将这种反常的负电阻现象解释为隧道效应。此后,江崎利用这一效应制成了隧

道二极管(也称江崎二极管)。1960 年,美裔挪威籍科学家加埃沃(Ivan Giaever,1929~)通过实验证明了在超导体隧道结中存在单电子隧道效应。在此之前的1956 年出现的“库珀对”及 BCS 理论被公认为是对超导现象的完美解释,单电

子隧道效应无疑是对超导理论的一个重要补充。1962 年,年仅 20 岁的英国剑桥

大学实验物理学研究生约瑟夫森(Brian David Josephson,1940~)预言,当两个超导体之间设置一个绝缘薄层构成 SIS(Superconductor-Insulator-Superconductor)时,电子可以穿过绝缘体从一个超导体到达另一个超导体。约瑟夫森的这一预言不久就为 P.W.安德森和 J.M.罗厄耳的实验 观测所证实——电子对通过两块超导金属间的薄绝缘层(厚度约为 10 埃)时发生了隧道效应,于是称之为“约瑟夫森效应”。

宏观量子隧道效应确立了微电子器件进一步微型化的极限,当微电子器件进一步微型化时必须要考虑上述的量子效应。例如,在制造半导体集成电路时,当电路的尺寸接近电子波长时,电子就通过隧道效应而穿透绝缘层,使器件无法正常工作。因此,宏观量子隧道效应已成为微电子学、光电子学中的重要理论。

闪存的存储单元为三端器件,与场效应管有相同的名称:源极、漏极和栅极。栅极与硅衬底之间有二氧化硅绝缘层,用来保护浮置栅极中的电荷不会泄漏。采用这种结构,使得存储单元具有了电荷保持能力,就像是装进瓶子里的水,当你倒入水后,水位就一直保持在那里,直到你再次倒入或倒出,所以闪存具有记忆能力。

与场效应管一样,闪存也是一种电压控制型器件。NAND 型闪存的擦和写均是基于隧道效应,电流穿过浮置栅极与硅基层之间的绝缘层,对浮置栅极进行充电(写数据)或放电(擦除数据)。而 NOR 型闪存擦除数据仍是基于隧道效应(电流从浮置栅极到硅基层),在写入数据时则是采用热电子注入方式(电流从浮置栅极到源极)。

场效应管工作原理

场效应晶体管(Field EffectTransistor 缩写(FET))简称场效应管。一般的晶体管是由两种极性的载流子,即多数载流子和反极性的少数载流子参与导电, 因此称为双极型晶体管,而 FET 仅是由多数载流子参与导电,它与双极型相反,也称为单极型晶体管。它属于电压控制型半导体器件,具有输入电阻高(108~109Ω)、噪声小、功耗低、动态范围大、易于集成、没有二次击穿现象、安全工作

区域宽等优点,现已成为双极型晶体管和功率晶体管的强大竞争者。

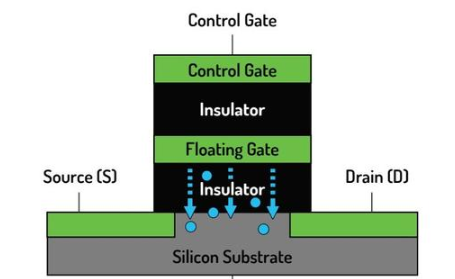

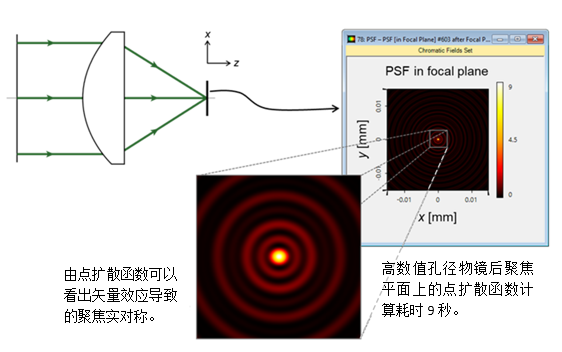

Flash 工作原理

在每个闪存芯片中都有海量的存储单元,有三个场效应管,源极、漏极和栅极。下图是一个闪存存储单元示意图,从上到下分别是控制栅极(Control Gate)、氧化层、浮栅层(Floating Gate)、隧道氧化层和衬底(Substrate)。左侧是源级(Sources)右侧是漏级(Drain),电流只能从源级向漏级单向传导。

闪存记录数据的关键在于浮栅层,当其中被充满电子时是已编程(写入)状态,代表二进制0;当其中没有电子时是已擦除状态,代表二进制1。

上面的这个0和1的逻辑听起来有些颠倒,不过当你了解到闪存的读取原理后就会觉得这样才是对的:源级到漏级之间没有电流(0),说明浮栅中有电子。

当源级到漏级之间有电流(1),说明浮栅里没有电子。

以上就是从闪存中读取数据的原理,往复杂了说它涉及到MOS管等复杂的半导体知识,但是如果朝简单的方向理解,我们也能轻松理解闪存表达数据的原理。

NAND Flash写入原理

对于NAND Flash的写入(编程),就是控制Control Gate去充电(对Control Gate加压),使得悬浮门存储的电荷够多,超过阈值Vth,就表示0。

接下来是向闪存单元中写入数据的方法:在控制栅极和漏级之间施加一个20V高电压,就可以引发量子隧道效应,使电子进入到浮栅层中。由于氧化隧道层的绝缘效果,进入到浮栅层的电子不容易流失掉,所以闪存可以在断电后继续保留数据。

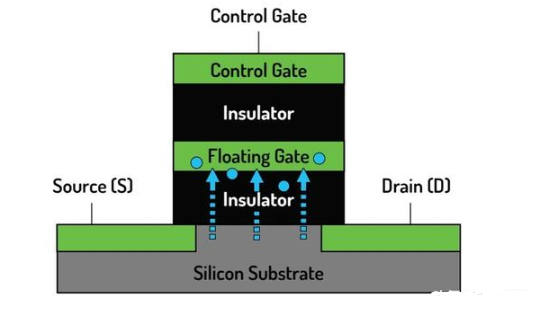

NAND Flash 擦除原理

对于NAND Flash的擦除(Erase),就是对悬浮门放电,低于阀值Vth,就表示1。

反过来也可以使用20V高电压反向将浮栅层中的电子“抽离”出去,这就是闪存的擦除操作。闪存的独特工作原理决定了闪存单元在写入之前必须经过擦除,而不能像磁记录那样直接覆盖写入。

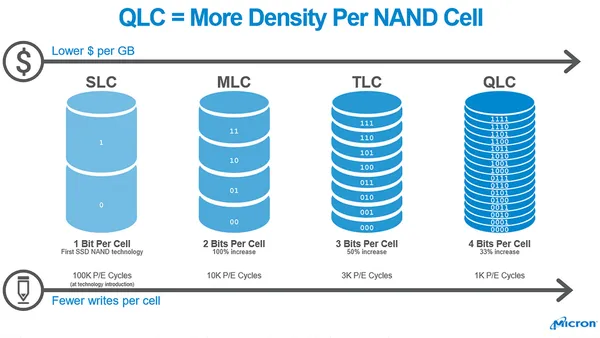

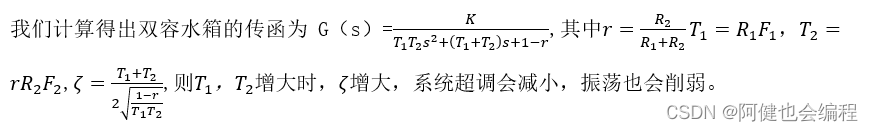

SLC、MLC、TLC、QLC 差异

对于原始的SLC闪存而言,一个存储单元只需保留一比特数据,非0即1,判断起来非常简单。SLC闪存速度快、寿命长,但容量小、每GB容量成本过高,不适合家用电脑的固态硬盘。

MLC闪存可以在每个存储单元中存储2比特数据,即00、01、10、11四种状态,浮栅层中的电荷数等级需要更加精细化。

由上图可以看到,MLC和SLC虽然使用相同的电压值,但是电压之间的阀值被分成了4份

到了TLC闪存(3比特/单元),状态数量达到8种,而QLC闪存(4比特/单元)的状态数量高达16种。

NAND FLASH 从 SLC -> MLC -> TLC -> QLC,每个单元存储的比特数增加,这样晶圆的存储密度会成倍提高,但对应的整卡可写入/擦除次数(P/E Cycle) 也降低(意味着寿命也越短),读写性能会越差。最重要的单位GB的成本会更低,芯片的成本是和面积直接相关的。面积越小,一个晶圆切出的Die(片)数目就更多,单Die的成本就降下来了。

各大原厂孜孜不倦地提高每个单元的比特数,目的就是为了减少成本,成本才是王道!

NAND Flash 使用挑战在哪里

挑战1:需要先擦除才能写入。

当今的NAND Flash可以读/写一个page,但是必须以block大小擦除。

擦除操作就是让块中所有的bit变为1,从一个干净的“已擦除”状态的block重新开始。当里面的页变为0后,只有擦除整个块才能让这个页变为1。为了尽量减少擦除的次数,成熟的块管理技术必不可少。

挑战2:读/写干扰。

NAND Flash的电荷非常不稳定,在读/写中很容易对邻近的单元造成干扰,干扰后会让附近单元的电荷脱离实际的逻辑数值,造成bit出错,因为阀值接近的关系,MLC相对SLC来说更容易受到干扰。

读取干扰

写入干扰

读取干扰指的是在读取某个page时,邻近的bit会受到升高电压的干扰,造成bit出错。写入干扰指的是,某个page在写入时,邻近bit的电压也被升高了,造成bit出错。相对写入干扰来说,读取干扰明显小的多。在读/写干扰中,可能造成某些bit被改变,结果造成数据出错。所以需要在返回数据给主机前,用ECC/EDC算法来纠正这些bit的错误。随着闪存工艺的提升,同样大小的晶片上被封装入更多的单元,造成干扰越来越厉害,所以需要更强大的ECC/EDC来纠正bit。

挑战3:数据保存期限

数据保存期指的是当完全断电后,数据能在NAND Flash里保存多久。NAND单元必须保证一个稳定的电压水平,来保证数据是有效的。典型的SLC一般为10年。电荷从悬浮门里漏出,我们叫做电子迁移,当随着时间的流逝,电荷泄漏到一定程度,改变了NAND单元里悬浮门的电压对应的逻辑值,这样就造成bit出错。

数据保存期会随着擦写次数的增加而明显降低,而且从上面的原理中看出,MLC的数据保存期明显会比SLC少。(更容易被干扰)

挑战4:坏块

NAND Flash里有2种坏块类型:

1,出厂坏块:由于为了保证产量和控制成本,出厂的NAND Flash某些就会有坏块。厂商保证SLC出厂坏块低于2%,MLC出厂坏块低于5%。

2,积累坏块:在多次的写入/擦除循环中,某些NAND单元的电荷电压被永久性的改变了,那就意味着包含这个NAND单元不可用了。

所以固态硬盘需要有坏块管理才能使用,主控制器用坏块表来映射出厂坏块和积累坏块到坏块区内,出厂时,颗粒的第一个块Block 0厂商会保证是可用的(至少ECC后可用)。

挑战5:擦写次数限制

造成NAND Flash有擦写次数限制的主要有2个因素:

1,电荷被困在氧化层,不能进入悬浮门。

2,氧化层结构被破坏。

如图,一旦氧化层损坏到达一定程度,造成电荷越来越难在P-substrate和悬浮门之间交流。电荷被困在氧化层造成悬浮门中的电压到不了阀值,所以说这个NAND单元就要被放入坏块区了。

当前主流SLC的P/E为10万次,50nm MLC为1万次,3xnm的MLC为5000次。到了这个数字并不意味着就不能用了,这个只是代表平均寿命,也就是说到了这个次数后,坏块就会开始大量增加了。

转载

https://blog.csdn.net/qq_41371349/article/details/104927524

NANDFlash原理_gongjiwei的博客-CSDN博客

![[附源码]计算机毕业设计JAVA基于JSP社区生鲜配送系统](https://img-blog.csdnimg.cn/df4b0ed1064a4b5e80f95e2c43fb64da.png)

![[附源码]java毕业设计网上手机商城](https://img-blog.csdnimg.cn/1887a93842e34ac4be1deb7da3bc4b8f.png)

![[附源码]java毕业设计图书管理系统论文](https://img-blog.csdnimg.cn/6ab23af9e5a8464f867317d2f24c870d.png)