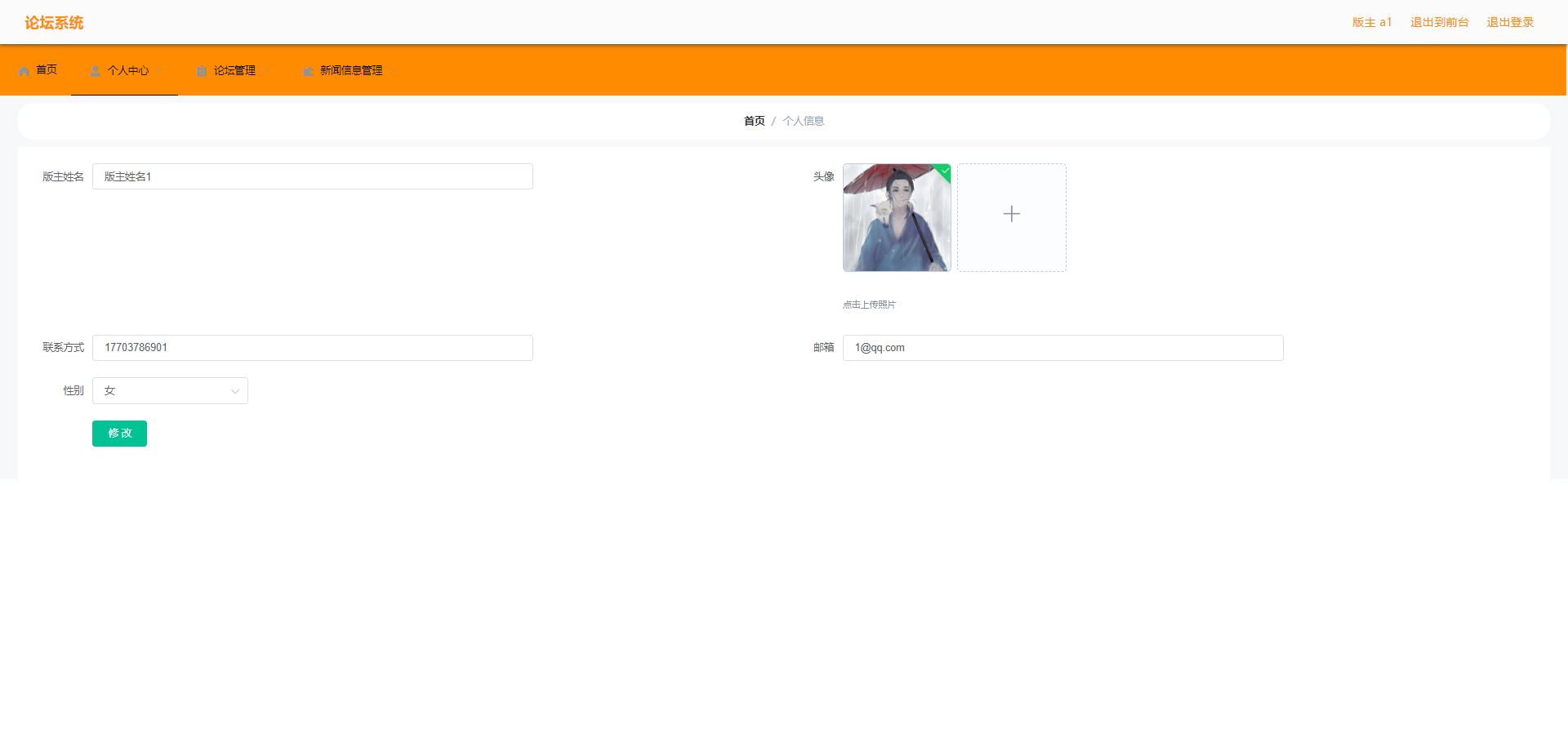

具体流程:

外部晶振(XTIpll)和 外部时钟(EXTCLK)经过OM【3:2】选择进入时钟模块

我们可以看到,在不同的模式下会选择不同的时钟源和状态。

时钟信号进入锁相环(PLL)后,会改变频率,输出时钟频率Mpll相关参考输入时钟频率Fin有如下等式:

通过PLL值选择表,我们就能大致确定我们的 M, P, S 的值:假设输入频率为12, 输出频率为400,那么M = 127, P = 2, S = 1, 这样,我们就能进行配置:

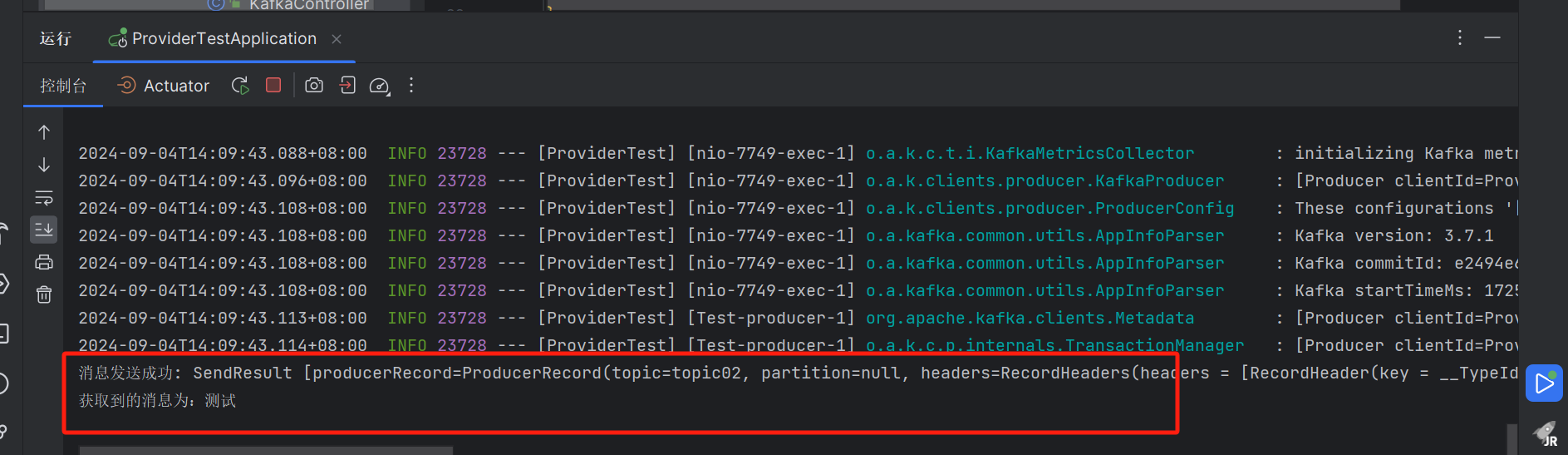

// 配置Fclk为400M

MPLLCON = (127 << 12) | (2 << 4) | (1 << 0);之后,新的时钟信号会被分成三种不同的时钟信号:FCLK,HCLK和PCLK。

FCLK是提供给ARM920T的时钟。

HCLK是提供给用于ARM920T,存储器控制器,中断控制器,LCD控制器,DMA和USB主机模块的AHB 总线的时钟。

PCLK是提供给用于外设如WDT,IIS,I2C,PWM定时器,MMC/SD接口,ADC,UART,GPIO,RTC和 SPI的APB总线的时钟。

假设:我们需要的时钟信号值:F(400M) , H(100M) , P(50M)

这三个信号的分频比例:1:4:8

通过上面两个表我们就能确定我们需要的 HDIVN 与 PDIVN 对应的值,然后写入时钟分频控制寄存器对应位置,然后就可以配置:

// 配置 F :H :P = 1 : 4 : 8

CLKDIVN = (2 << 1) | (1 << 0);到此,我们的时钟分频控制器流程就完成了。

有一点我们需要注意,我们编码流程应该是从后往前,这样的目的是为了防止高频信号烧坏我们的芯片。