1.7 功耗墙

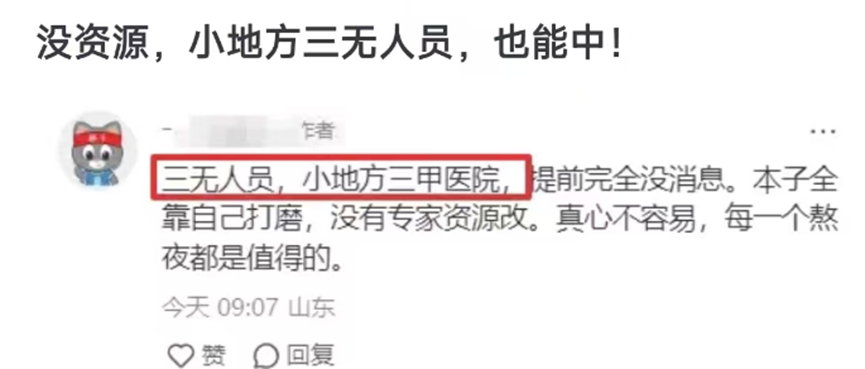

25 年间 1ntel x86 八代微处理器的时钟频率和功耗 。 奔腾 4 处理器时钟频率和功耗提高很大 ,但是性能提升不大 。 Prescott 发热问题导致奔腾 4 处理器的生产线被放弃 。 Core 2 生产线恢复使用低时钟频率的简单流水线和片上多处理器 。 Core i5 采用同样的流水线

功耗提供了能够冷却的极限,在后PC时代,能量是真正关键的资源,对于个人移动设备来说,电池寿命比性能更关键。设计者要尽量降低功耗。

评价功耗时,使用能耗,比使用功耗,更加科学。

能耗的单位是 焦耳/秒 。

占统治地位的集成电路技术是 CMOS (互补型金属氧化半导体),其主要的能耗来源是动态能耗,即在晶体管开关过程中产生的能耗,即晶体管的状态从 0 翻转到 1 或从 1 翻转到 0 消耗的能董 。

动态能耗取决千每个晶体管的负载电容和工作电压:

能耗 ∝ 负载电容 x 电压^2

这个等式表示的是一个0->1->0或者1->0->1的逻辑转换过程中消耗的能量 。一个晶体管消耗的能量为:

能耗 ∝ 1/2 X 负载电容 x 电压^2

每个晶体管需要的功耗是一个翻转需要的能耗和开关频率的乘积:

功耗 ∝1/2 X 负载电容 x 电压^2 X 开关频率

开关频率是时钟频率的函数,负载电容是连接到输出上的晶体管数量 (称为扇出)和 工艺的函数,该函数决定了导线和晶体管的电容 。

为什么时钟频率增长为 1 000 倍,而功耗只增长为 30 倍呢?因为能耗和功耗是电压平方的函数,能够通过降低电压来大幅减少,每次工艺更新换代时都会这样做。一般来说,每代的电压降低大约 15% 。 20 多年来,电压从 5V 降到了1V 。 这就是功耗只增长 30 倍的原因所在 。

一个例题:

假设我们需要开发一种新处理器,其负载电容只有旧处理器的 85% 。 再假设其电压可以调节,与旧处理器相比电压降低了 15%, 进而导致频率也降低了 15%, 问这对新处理器的动态功耗有何影响?

功耗比:

新处理器的功耗大约是旧的处理器的功耗的一半。

如果电压继续下降会使晶体管泄漏电流过大,就像水龙头不能被完全关闭 一样 。 目前 40% 的功耗是由泄漏造成的,如果晶体管的泄漏电流再大,情况将会变得无法收拾 。

为了解决功耗问题,设计者连接大设备以增加冷却,而且将芯片中的一些在给定时钟周期内暂时不用的部分关闭 。 尽管有很多更加昂贵的方式来冷却芯片,但继续提高芯片的功耗(比如到300 瓦)对个人计算机甚至服务器来说成本太高了,对个人移动设备就更不用说了 。

注解:

动态功耗时CMOS能耗的主要来源,但静态能耗也是存在的,晶体管即使在关闭的状态下,也会存在泄漏电流。

增加晶体管的数目,就会增加漏电功耗,即使这些晶体管总是关闭的 。

1.8 单处理器向多处理器的转变

功耗的极限迫使微处理器的设计产生了巨变 。 下图给出了桌面微处理器的程序响应时间的发展 。 从 2002 年起,其每年的增长速率从 1.5 下降到 1. 2 。

在 2006 年,**所有桌面和服务器公司都在单片微处理器中加入了多个处理器,以求更大的吞吐率,**而不再继续追求降低单个程序运行在单个处理器上的响应时间 。 为了减少 processor 和microprocessor (微处理器)这两个词语之间的混淆,一些公司将 processor 作为 “cores” 的代称,这样 microprocessor 就是多核处理器了 。 因此,一个“四核“微处理器是一个包含了 4 个processor 或者 4 个 core 的芯片 。

硬件/软件接口:并行性对计算性能一直十分重要,但它往往是隐蔽的 。 流水线是一种漂亮的技术,通过指令重叠执行使程序运行得更快 。 这是指令级并行性的一个例子 。在抽取了硬件的并行本质之后,程序员或编译程序可认为在硬件中指令是串行执行的 。

迫使程序员意识到硬件的并行性,并显式地按并行方式重写其程序,曾经是计算机体系结构的“第三抱怨",以致很多采用此种方式进行革新的公司都失败了

编写显式并行的程序的困难点:

- 调度

- 负载平衡

- 通信开销

- 同步开销

- 其他开销

1.9 基准

用户日复一日使用的程序是用于评价新型计算机最完美的程序 。 所运行的一组程序集构成了工作负载 (workload) 。 要评价两台计算机系统,只需简单地比较工作负载在两台计算机上的执行时间 。 然而大多数用户并不这样做,他们通过其他方法测量计算机的性能,希望这些方法能够反映计算机执行用户工作负载的情况 。 最常用的测量方法是使用一组专门用于测量性能的基准测试程序 (benchmark) 。 这些测试程序形成负载,用户期望预测实际负载的性能 。 我们在前面提到,要加速大概率事件的执行,必须先准确地知道哪些是大概率事件,因此基准测试程序在计算机系统结构中具有非常重要的作用 。

SPEC (system perlormance evaluation cooperative) 是由许多计算机销售商共同出资赞助并支持的合作组织,目的是为现代计算机系统建立基准测试程序集 。 1989 年, SPEC 建立了重点面已面向处理器性能的基准程序集(现在称为 SPEC89) 。 历经 5 代发展,目前最新的是 SPEC CPU2006, 它包括 12 个整数基准程序集 (CINT 2006) 和 17 个浮点基准程序集 (CFP 2006) 。 CINT2006 包括 C 编译程序、量子计算机仿真、下象棋程序等, CFP 2006 包括有限元模型结构化网格法、分子动力学质点法 、 流体动力学稀疏线性代数法等 。

下图,列举了 SPEC 整数基准程序及其在 Intel Core i7 上的执行时间、指令数、 CPI 和时钟周期时间等组成的 SPEC 分值 。

为了简化测试结果, SPEC 决定使用单一的数字来归纳所有12 种整数基准程序 。 具体方法是将被测计算机的执行时间标准化,即将被测计算机的执行时间除以一个参考处理器的执行时间,结果称为 SPECratio 。 SPEC ratio 值越大,表示性能越快(因为 SPEC ratio 是执行时间的倒数) 。

SPECINTC2006 基准程序在 2. 66GHz 的 Intel Core i7 920 上的运行结果 。 按照经典的 CPU 性能公式的等式,执行时间是本表的 三个因素的乘积:以亿为单位的指令数 、 每条指令的时钟数 (CPI) 以及纳秒级的时钟周期时间 。 SPEC ratio 仅仅是参考时间,由 SPEC 提供,被所测量的执行时间相除 。 SPECINTC2006 所引用的单个数目是 SPEC ratio 的几何平均数。

其中,执行时间比 , 是总共 n 个工作负载中第 L 个程序的执行时间按参照计算机进行标准化的

结果,并且