竞争和冒险

文章目录

- 竞争和冒险

- 总结

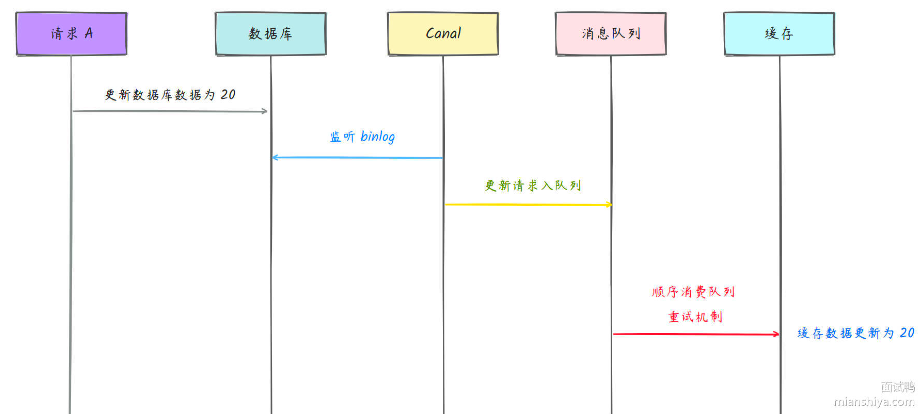

产生原因

数字电路中,信号传输与状态变换时都会有一定的延时。

在组合逻辑电路中,不同路径的输入信号变化传输到同一点门级电路时,在时间上有先有后,这种先后所形成的时间差称为竞争(Competition)。

由于竞争的存在,输出信号需要经过一段时间才能达到期望状态,过渡时间内可能产生瞬间的错误输出,例如尖峰脉冲。这种现象被称为冒险(Hazard)。

竞争不一定有冒险,但冒险一定会有竞争。

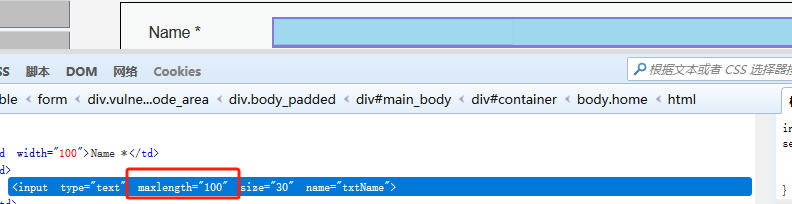

例如,对于给定逻辑 F = A & A’,电路如左下图所示。

由于反相器电路的存在,信号 A’ 传递到与门输入端的时间相对于信号 A 会滞后,这就可能导致与门最后的输出结果 F 会出现干扰脉冲。如右下图所示。

即:门级电路,有两个输入,在同时变化,由于布局布线延迟导致尖峰脉冲。

其实实际硬件电路中,只要门电路各个输入端延时不同,就有可能产生竞争与冒险。

例如一个简单的与门,输入信号源不一定是同一个信号变换所来,由于硬件工艺、其他延迟电路的存在,也可能产生竞争与冒险,如下图所示。

消除方法

对数字电路来说,常见的避免竞争与冒险的方法主要有 4 种。

1)增加滤波电容,滤除窄脉冲

此种方法需要在输出端并联一个小电容,将尖峰脉冲的幅度削弱至门电路阈值以下。

此方法虽然简单,但是会增加输出电压的翻转时间,易破坏波形。

2)修改逻辑,增加冗余项

利用卡诺图,在两个相切的圆之间,增加一个卡诺圈,并加在逻辑表达式之中。

3)使用时钟同步电路,利用触发器进行打拍延迟

同步电路信号的变化都发生在时钟边沿。对于触发器的 D 输入端,只要毛刺不出现在时钟的上升沿并且不满足数据的建立和保持时间,就不会对系统造成危害,因此可认为 D 触发器的 D 输入端对毛刺不敏感。 利用此特性,在时钟边沿驱动下,对一个组合逻辑信号进行延迟打拍,可消除竞争冒险。

延迟一拍时钟时,会一定概率的减少竞争冒险的出现。实验表明,最安全的打拍延迟周期是 3 拍,可有效减少竞争冒险的出现。

当然,最终还是需要根据自己的设计需求,对信号进行合理的打拍延迟。

4)采用格雷码计数器

递加的多 bit 位计数器,计数值有时候会发生多个 bit 位的跳变。

例如计数器变量 counter 从 5 计数到 6 时, 对应二进制数字为 4’b101 到 4’b110 的转换。因为各 bit 数据位的延时,counter 的变换过程可能是: 4’b101 -> 4’b111 -> 4’b110。如果有以下逻辑描述,则信号 cout 可能出现短暂的尖峰脉冲,这显然是与设计相悖的。

小结

一般来说,为消除竞争冒险,增加滤波电容和逻辑冗余,都不是 Verilog 设计所考虑的。

计数采用格雷码计数器,大多数也是应用在高速时钟下减少信号翻转率来降低功耗的场合。

利用触发器在时钟同步电路下对异步信号进行打拍延时,是 Verilog 设计中经常用到的方法。

总结

核心思想就是记住 **F = A & A’*对应的硬件和时序图,就能理解了。消除方法,一般就是打拍延迟。

![[C++] map、set 的 封装 (二):map、set和红黑树的双向奔赴](https://i-blog.csdnimg.cn/direct/f61e059161ab4b0f87f842e0f6567be0.png)