Xilinx 家的 FPGA 支持多重启动功能(Multiboot),即可以从多个 bin 文件中进行选择性加载,从而实现对系统的动态更新,或系统功能的动态调整。

这一过程可以通过嵌入在 bit 文件里的 IPROG 命令实现上电后的自动加载。而同时 Xilinx 也提供了 ICAP 原语,给用户提供了访问配置功能的权限(对于 7 series 的芯片,需要使用 ICAPE2 原语),从而获得更加灵活的多重启动方式。

本文即介绍 Multiboot 以及这两种启动方式,并对两种 Multiboot 进行实现。

文章目录

- 多重启动(Multiboot)

- Golden Image Initial System Setup

- Initial MultiBoot Image System Setup

- IPROG 说明

- WBSTAR 寄存器

- Watchdog 计数器

- 从 ICAPE2 原语启动 Multiboot 介绍

- ICAPE2 原语

- 嵌入 IPROG 命令启动 Multiboot 介绍

- 嵌入 IPROG 的操作流程

- ICAPE2 启动 Multiboot 代码示例

- Multiboot_ctrl.v

- 测试

- 参考文献

多重启动(Multiboot)

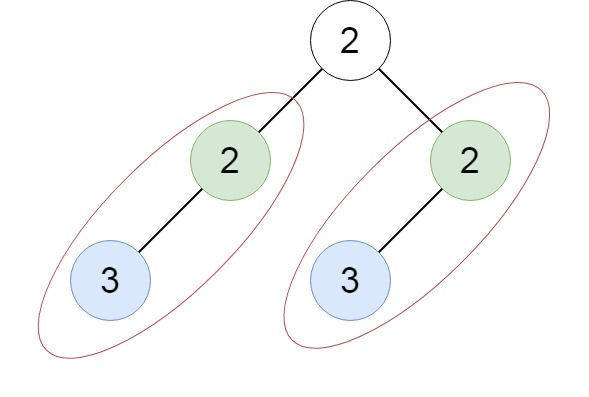

首先对 Multiboot 的流程进行一下介绍,

如图所示,在实现多重启动时,FLASH 中会保存多个 bin 文件,其中保存在 0 地址的称为 Golden 镜像,而其他的被称为 Multiboot 镜像(也称为 Update 镜像),这里就以 2 个 Image 为例进行说明。

一般地,对于单个 bin 的情况,可以直接向 FLASH 烧录 .bin 文件,也可以烧录对应生成的 .mcs;而如果要烧录多个版本的镜像,则可以在生成 .mcs 时在不同地址载入多个不同的 bit 文件,然后下载这个 .mcs 文件。

Golden Image Initial System Setup

在上图所示的 Golden Image Initial System Setup 启动模式下,上电后 FPGA 会自动加载 Golden 镜像,随后尝试加载 Multiboot 镜像,以重新配置 FPGA,实现代码的更新/功能的更替。

在这种启动方式下:

- IPROG 命令被嵌入在 Golden Image 里(指将 IPROG 命令嵌在比特流文件里),或者通过 Golden Image 里编写的 ICAPE2 原语程序启动对 Multiboot Image 的读取;

- Multiboot Image 应当存储在热启动起始地址寄存器( Warm Boot Start Address Register, WBSTAR )指定的地址处;

- 应当启动 Watchdog 计时器,以在编程失败的情况下执行恢复操作。

在回退(fallback)发生时,嵌入的 IPROG 指令将被忽略,因此不会陷入反复触发加载 Multiboot 的死循环。在回退完成后,WBSTAR 将被 bitstream 重写。

Initial MultiBoot Image System Setup

也可以在上电后先启动 Multiboot 版本镜像,在启动失败的情况下自动回退地址 0 的 Golden 镜像,流程如下图所示

在在线更新功能的设计中,Initial MultiBoot Image System Setup 模式是更加常用的。

在这种启动方式下,对于 Golden Image:

- WBSTAR 应当指向 Multiboot Image,同时应当插入一个 IPROG 指令以在上电时触发对 Multiboot 的下载(在比特流文件里插入 IPROG 命令);

- 需要启动 Configuration Timer;

- 如果 Golden Image 有能力修复 FLASH,则也可以实现 ICAP 原语以重启启动 Multiboot 的加载;

- 对于 SPI 配置模式,在回退 Golden 过程中,始终采用 SPI x1 的模式。

对于 Multiboot Image:

- 需要启动 Configuration Timer;

- Multiboot Image 也可以实现 ICAP 原语以实现对其他 Multiboot Image 的重加载,或对 Golden Image 的受控回退。

IPROG 说明

IPROG(Internal PROGRAM)命令是 PROGRAM_B 引脚功能的一个子集,该命令可以从 ICAP 原语发出,也可以直接嵌入到比特流里。当为后者时,WBSTAR 和 IPROG 应当位于 Golden bit file 的开头,此时在上电后会触发从新地址加载 multiboot Image 的事件;如果加载失败,则将返回地址 0 重新加载比特流,此时会忽略 IPROG,因此加载到的程序将是 Golden Image。

WBSTAR 寄存器

WBSTAR 寄存器保存了 IPROG 命令配置的启动地址,该寄存器的值可以由嵌入在 bitstream 的 IPROG 配置,也可以由 ICAPE2 发出的 IPROG 配置。如果 bitstream 中没有配置 WBSTAR,则地址默认为 0,因此如果从 Golden Image 触发了多重启动,则在加载完 Multiboot Image 后,WBSTAR 将被设置为 0。

上电后,设备将从地址 0 开始读取 FLASH,在加载了 WBSTAR 并发出 IPROG 后,将重定向到 WBSTAR 指定地址读取 Imaeg。

Watchdog 计数器

看门狗有两种模式:配置监视器模式、用户逻辑监视器模式。在配置监视器模式下,Timer Register 通过比特流设置,需要在所有 bit File 中启用这个计数器。Watchdog 由 FPGA 内部锁相环产生的 65MHz 时钟驱动(这一描述和下表中的描述相悖),当计数器回到 0 时,将触发回退。该计数器从比特流起始开始计数,在启动序列结束时被禁用。

从 ICAPE2 原语启动 Multiboot 介绍

当从 ICAPE2 原语触发 Multiboot 时,命令序列为:1. 发送同步码;2. 设置 WBSTAR;3. 发送 IPROG 命令。一个通过 ICAPE2 发送的命令序列如下

ICAPE2 原语

ICAPE2 原语接口如图,调用格式如下

// 7 Series

// Xilinx HDL Language Template, version 2023.2

ICAPE2 #(

.DEVICE_ID (32'h3651093), // Specifies the pre-programmed Device ID value to be used for simulation purposes.

.ICAP_WIDTH ("X32"), // Specifies the input and output data width.

.SIM_CFG_FILE_NAME ("NONE") // Specifies the Raw Bitstream (RBT) file to be parsed by the simulation model.

)

ICAPE2_inst(

.O (O), // 32-bit output: Configuration data output bus

.CLK (CLK), // 1-bit input: Clock Input

.CSIB (CSIB), // 1-bit input: Active-Low ICAP Enable

.I (I), // 32-bit input: Configuration data input bus

.RDWRB (RDWRB) // 1-bit input: Read/Write Select input

);

其中 DEVICE_ID 是设备 ID,与芯片型号有关,譬如对于 K7-325T,ID 如下

嵌入 IPROG 命令启动 Multiboot 介绍

WBSTAR 和 IPROG 命令可以嵌入到一个位流中,如图所示。在 7 系列 FPGA 的 bitstream 中,WBSTAR 默认填入空白,同时保留了 IPROG 的占位符。我们打开一个 .bin 文件,看看到底是如何组织的

可以看到,在地址 0x30 开始的四个字节,为同步码 AA995566,随后是一个 NO OP(20000000),然后是一些其他的命令;在 0x54 开始的 4 个字节,为 Write 1 Word to WBSTAR 命令(30020001),随后四个字节为要写入 WBSTAR 的地址,这里默认是 0;随后紧跟着 Write 1 Word to CMD 命令(30008001),随后四字节为写入的命令,这里默认是占位符 00000000,可以修改为 IPROG (0000000F)以实现 IPROG 命令的嵌入。

这里我们只是观察一下 .bin/.bit 文件中 IPROG 是如何嵌入的,通过直接修改 .bit/.mcs 实现 Multiboot 理论上也是可行的,但实际上我们不会这么做。在实际操作中我们可以通过在 xdc 中增加约束,生成需要的 .bit,然后再组合成 .mcs,下一节就介绍如何通过添加约束实现这一过程。

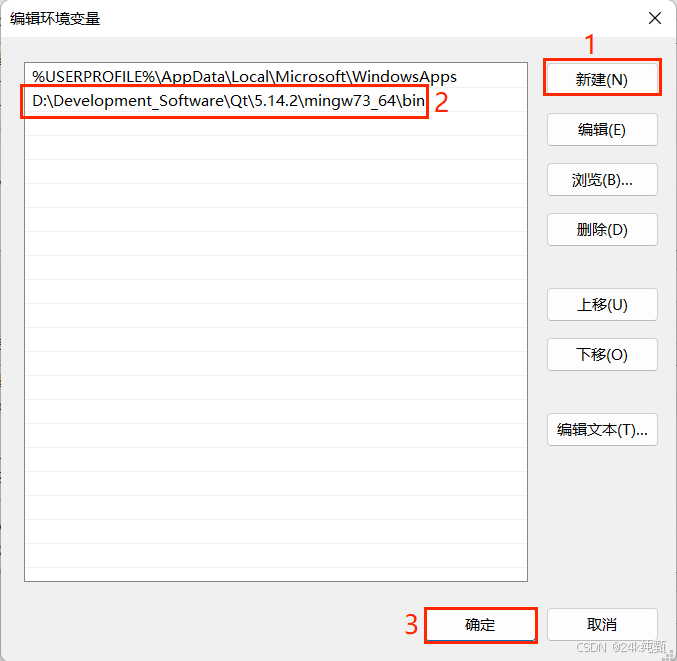

嵌入 IPROG 的操作流程

在编译 Golden Image 时,需要在 xdc 中增加如下约束

set_property BITSTREAM.CONFIG.CONFIGFALLBACK ENABLE [current_design]

set_property BITSTREAM.CONFIG.NEXT_CONFIG_ADDR 0x01000000 [current_design]

set_property CONFIG_MODE SPIX1 [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 1 [current_design]

#由于fallback使用SPIx1,因此请确定一定有此配置

# 如果 FLASH 大小大于等于 256Mb,要增加如下约束,否则高于24位的地址会被忽略,导致无法启动对应的 update 镜像

set_property BITSTREAM.CONFIG.SPI_32BIT_ADDR YES [current_design]

在编译 Multiboot Image 时,需要在 xdc 中使用如下约束

set_property BITSTREAM.CONFIG.CONFIGFALLBACK ENABLE [current_design]

set_property CONFIG_MODE SPIX1 [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 1 [current_design]

#由于fallback使用SPIx1,因此请确定一定有此配置

# 如果 FLASH 大小大于等于 256Mb,要增加如下约束,否则高于24位的地址会被忽略,导致无法启动对应的 update 镜像

set_property BITSTREAM.CONFIG.SPI_32BIT_ADDR YES [current_design]

上述约束中,BITSTREAM.CONFIG.CONFIGFALLBACK 用于启用回退(Fallback)功能,BITSTREAM.CONFIG.NEXT_CONFIG_ADDR 用于设置 WBSTAR 寄存器,由于 Fallback 要求 SPIx1,因此 BITSTREAM.CONFIG.SPI_BUSWIDTH 要设为 1。

编译完成后,我们还是打开 .bit 看一下,Golden Image 的如下

可以看到 WBSTAR 和 IPROG 命令已经被嵌入比特流。

将两个 .bit 文件分别载入地址 0 和高位地址,生成 .mcs,注意 Multiboot Image 所载入的高位地址应当与前面 xdc 配置的 NEXT_CONFIG_ADDR 相同。烧录后,可以看到 update Image 被启动。

ICAPE2 启动 Multiboot 代码示例

Multiboot_ctrl.v

对于 SPI 设备,WBSTAR 地址有如下描述,即 Master SPI 模式下,WBSTAR 只会使用低 24 位,这 24 位为 FLASH 地址的 31:8 bits,在实现时应当注意

代码如下

/*

* file : multiboot_ctrl.v

* author : 今朝无言

* Lab : WHU-EIS-LMSWE

* date : 2023-11-30

* version : v1.0

* description : ICAP 原语实现程控 multiboot(多重启动),K7需要使用 ICAPE2 原语

* Copyright © 2023 WHU-EIS-LMSWE, All Rights Reserved.

*/

`default_nettype none

module multiboot_ctrl(

input wire clk,

input wire rst_n,

input wire multiboot_start, //触发Multiboot, 上升沿有效

input wire [31:0] multiboot_addr, //要启动的Muliboot Image的起始地址

output reg busy

);

//-------------------ICAPE2原语-----------------------------

wire ICAPE2_CLK;

wire [31:0] ICAPE2_O;

reg ICAPE2_CSIB;

wire [31:0] ICAPE2_I;

reg ICAPE2_RDWRB;

assign ICAPE2_CLK = clk;

ICAPE2 #(

.DEVICE_ID (32'h3651093), // Specifies the pre-programmed Device ID value to be used for simulation purposes. K7-325T的为32'h3651093

.ICAP_WIDTH ("X32"), // Specifies the input and output data width.

.SIM_CFG_FILE_NAME ("NONE") // Specifies the Raw Bitstream (RBT) file to be parsed by the simulation model.

)

ICAPE2_inst(

.O (ICAPE2_O), // 32-bit output: Configuration data output bus

.CLK (ICAPE2_CLK), // 1-bit input: Clock Input

.CSIB (ICAPE2_CSIB), // 1-bit input: Active-Low ICAP Enable

.I (ICAPE2_I), // 32-bit input: Configuration data input bus

.RDWRB (ICAPE2_RDWRB) // 1-bit input: Read/Write Select input 1对应rd,0对应wr

);

wire [31:0] Dummy = 32'hFFFFFFFF;

wire [31:0] Sync_Word = 32'hAA995566;

wire [31:0] NOOP = 32'h20000000;

wire [31:0] WR_WBSTAR = 32'h30020001;

/*When using ICAPE2 to set the WBSTAR address, the 24 most significant address bits should be written

to WBSTAR[23:0]. For SPI 32-bit addressing mode, WBSTAR[23:0] are sent as address bits [31:8]. The

lower 8 bits of the address are undefined and the value could be as high as 0xFF. Any bitstream

at the WBSTAR address should contain 256 dummy bytes before the start of the bitstream.*/

wire [31:0] WBSTAR = {3'b000, 5'h0, multiboot_addr[31:8]};

wire [31:0] WR_CMD = 32'h30008001;

wire [31:0] IPROG = 32'h0000000F;

//ICAPE2位翻转

reg [31:0] wrdat;

assign ICAPE2_I = {wrdat[24], wrdat[25], wrdat[26], wrdat[27], wrdat[28], wrdat[29], wrdat[30], wrdat[31],

wrdat[16], wrdat[17], wrdat[18], wrdat[19], wrdat[20], wrdat[21], wrdat[22], wrdat[23],

wrdat[8], wrdat[9], wrdat[10], wrdat[11], wrdat[12], wrdat[13], wrdat[14], wrdat[15],

wrdat[0], wrdat[1], wrdat[2], wrdat[3], wrdat[4], wrdat[5], wrdat[6], wrdat[7]};

//------------------------FSM----------------------------------

localparam S_IDLE = 16'h0001;

localparam S_DUMMY = 16'h0002;

localparam S_SYN_WORD = 16'h0004;

localparam S_NOOP1 = 16'h0008;

localparam S_WR_WBSTAR = 16'h0010;

localparam S_WBSTAR = 16'h0020;

localparam S_WR_CMD = 16'h0040;

localparam S_IPROG = 16'h0080;

localparam S_NOOP2 = 16'h0100;

localparam S_STOP = 16'h0200;

wire multiboot_start_pe;

reg multiboot_start_d0;

reg multiboot_start_d1;

assign multiboot_start_pe = multiboot_start_d0 & (~multiboot_start_d1);

always @(posedge clk) begin

multiboot_start_d0 <= multiboot_start;

multiboot_start_d1 <= multiboot_start_d0;

end

reg [15:0] state = S_IDLE;

reg [15:0] next_state;

always @(posedge clk) begin

if(~rst_n) begin

state <= S_IDLE;

end

else begin

state <= next_state;

end

end

always @(*) begin

case(state)

S_IDLE: begin

if(multiboot_start_pe) begin

next_state <= S_DUMMY;

end

else begin

next_state <= S_IDLE;

end

end

S_DUMMY: next_state <= S_SYN_WORD;

S_SYN_WORD: next_state <= S_NOOP1;

S_NOOP1: next_state <= S_WR_WBSTAR;

S_WR_WBSTAR: next_state <= S_WBSTAR;

S_WBSTAR: next_state <= S_WR_CMD;

S_WR_CMD: next_state <= S_IPROG;

S_IPROG: next_state <= S_NOOP2;

S_NOOP2: next_state <= S_STOP;

S_STOP: next_state <= S_IDLE;

default: next_state <= S_IDLE;

endcase

end

always @(posedge clk) begin

case(state)

S_IDLE: begin

wrdat <= 32'd0;

ICAPE2_CSIB <= 1'b1;

ICAPE2_RDWRB <= 1'b1;

end

S_DUMMY: begin

wrdat <= Dummy;

ICAPE2_CSIB <= 1'b0;

ICAPE2_RDWRB <= 1'b0;

end

S_SYN_WORD: begin

wrdat <= Sync_Word;

ICAPE2_CSIB <= 1'b0;

ICAPE2_RDWRB <= 1'b0;

end

S_NOOP1: begin

wrdat <= NOOP;

ICAPE2_CSIB <= 1'b0;

ICAPE2_RDWRB <= 1'b0;

end

S_WR_WBSTAR: begin

wrdat <= WR_WBSTAR;

ICAPE2_CSIB <= 1'b0;

ICAPE2_RDWRB <= 1'b0;

end

S_WBSTAR: begin

wrdat <= WBSTAR;

ICAPE2_CSIB <= 1'b0;

ICAPE2_RDWRB <= 1'b0;

end

S_WR_CMD: begin

wrdat <= WR_CMD;

ICAPE2_CSIB <= 1'b0;

ICAPE2_RDWRB <= 1'b0;

end

S_IPROG: begin

wrdat <= IPROG;

ICAPE2_CSIB <= 1'b0;

ICAPE2_RDWRB <= 1'b0;

end

S_NOOP2: begin

wrdat <= NOOP;

ICAPE2_CSIB <= 1'b0;

ICAPE2_RDWRB <= 1'b0;

end

S_STOP: begin

wrdat <= 32'd0;

ICAPE2_CSIB <= 1'b1;

ICAPE2_RDWRB <= 1'b1;

end

default: begin

wrdat <= 32'd0;

ICAPE2_CSIB <= 1'b1;

ICAPE2_RDWRB <= 1'b1;

end

endcase

end

always @(*) begin

case(state)

S_IDLE: busy <= 1'b0;

default: busy <= 1'b1;

endcase

end

endmodule

测试

创建两个工程如下

- Prj_1

//生成2个点灯的程序,使用ICAP来回切换这两个Image

//本工程作为 Golden Image 存入地址 0

`default_nettype none

module Prj_1(

input wire clk_sys, //OXCO_10M

input wire [3:0] Key,

output wire [3:0] LED

);

assign LED = 4'b0001;

multiboot_ctrl multiboot_ctrl_inst(

.clk (clk_sys),

.rst_n (1'b1),

.multiboot_start (~Key[0]),

.multiboot_addr (32'h01000000), //加载0x01000000处的Multiboot Image

.busy ()

);

endmodule

- Prj_2

//生成2个点灯的程序,使用ICAP来回切换这两个Image

//本工程作为 Update Image 存入高位地址

`default_nettype none

module Prj_2(

input wire clk_sys, //OXCO_10M

input wire [3:0] Key,

output wire [3:0] LED

);

assign LED = 4'b0010;

multiboot_ctrl multiboot_ctrl_inst(

.clk (clk_sys),

.rst_n (1'b1),

.multiboot_start (~Key[1]),

.multiboot_addr (32'h00000000), //加载0x00000000处的Golden Image

.busy ()

);

endmodule

烧录后,通过按键可以来回切换两个工程,读者可自行验证。

一个注意事项,在烧录完成后,必须拔掉 JTAG 再掉电重启,ICAP 才可以正确启动 Multiboot Image,如果是不拔掉 JTAG 掉电重启,ICAP 触发后只会加载 Golden Image。(真坑人啊,因为这个调了好久 (•́へ•́╬) )

参考文献

- ug470_Config.pdf

- ug953-vivado-7series-libraries.pdf