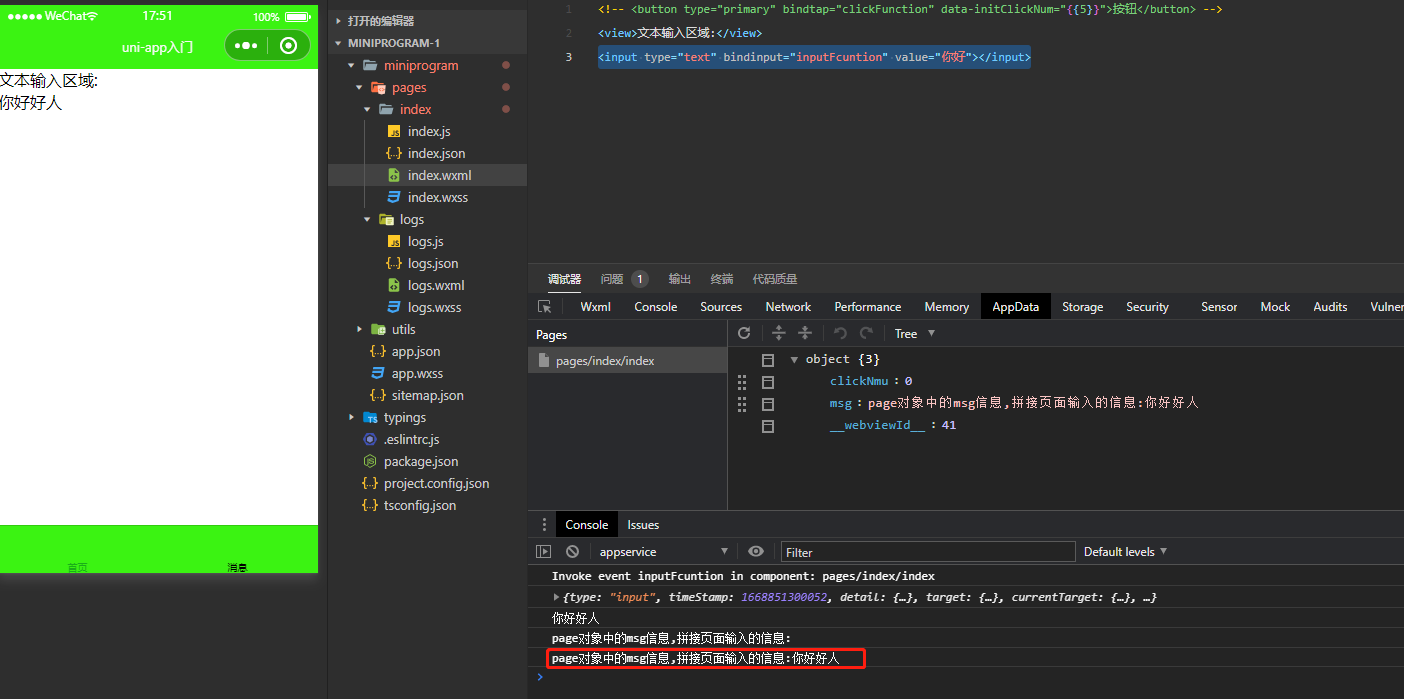

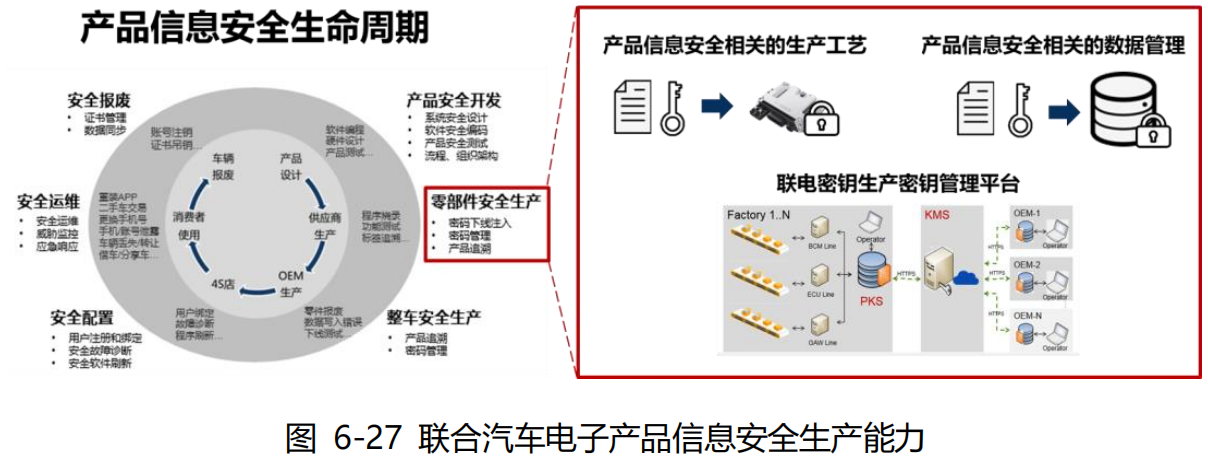

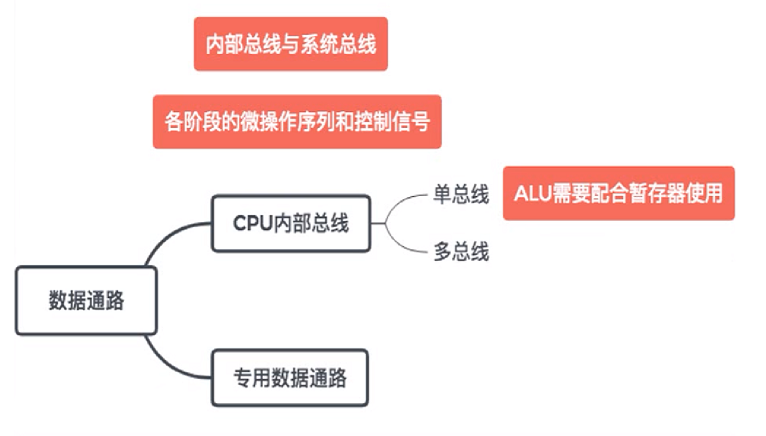

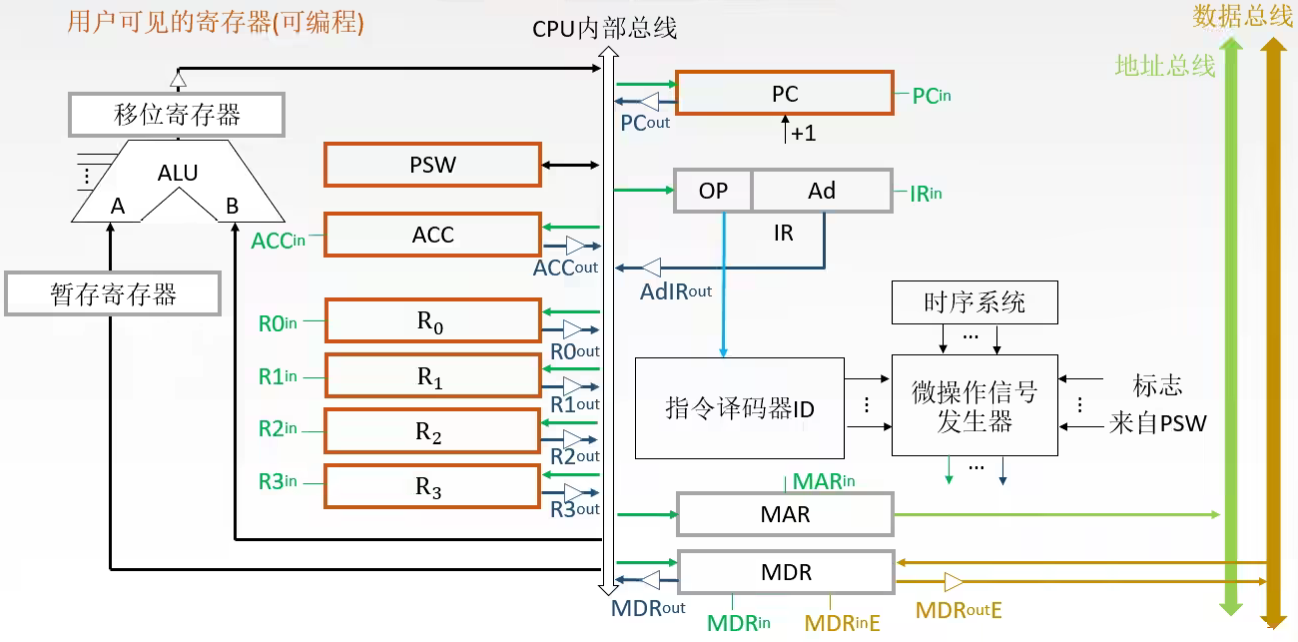

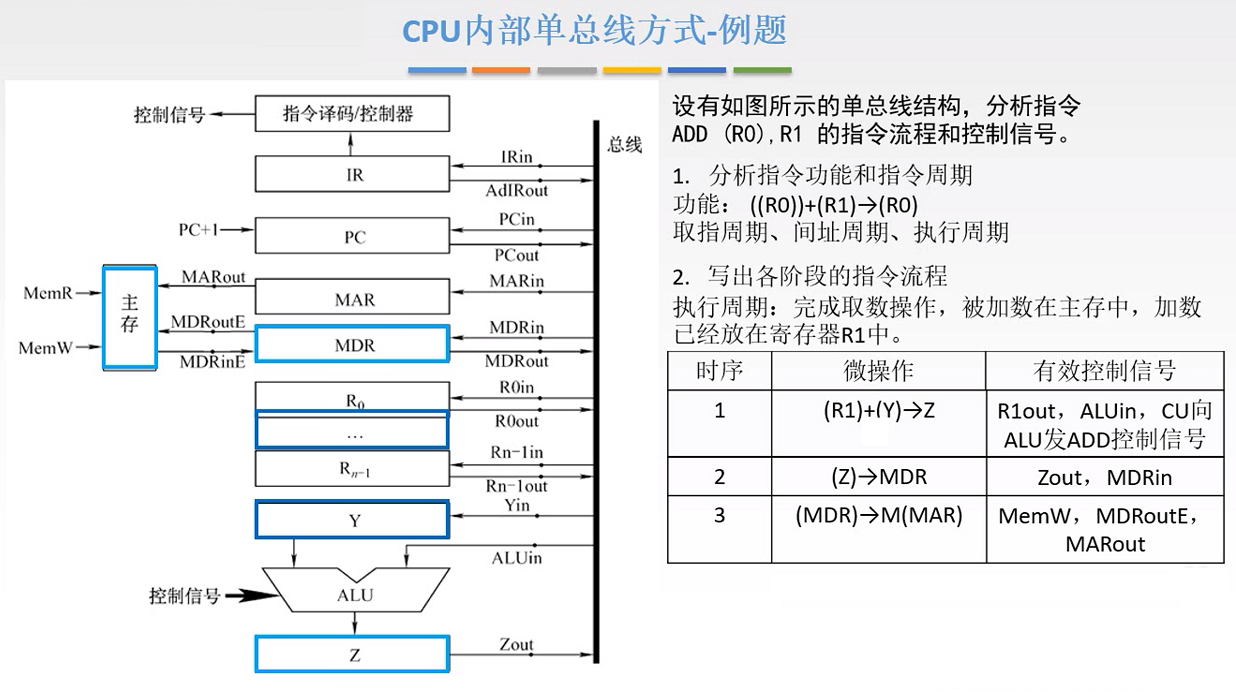

5.3.1 数据通路-CPU内部单总线方式

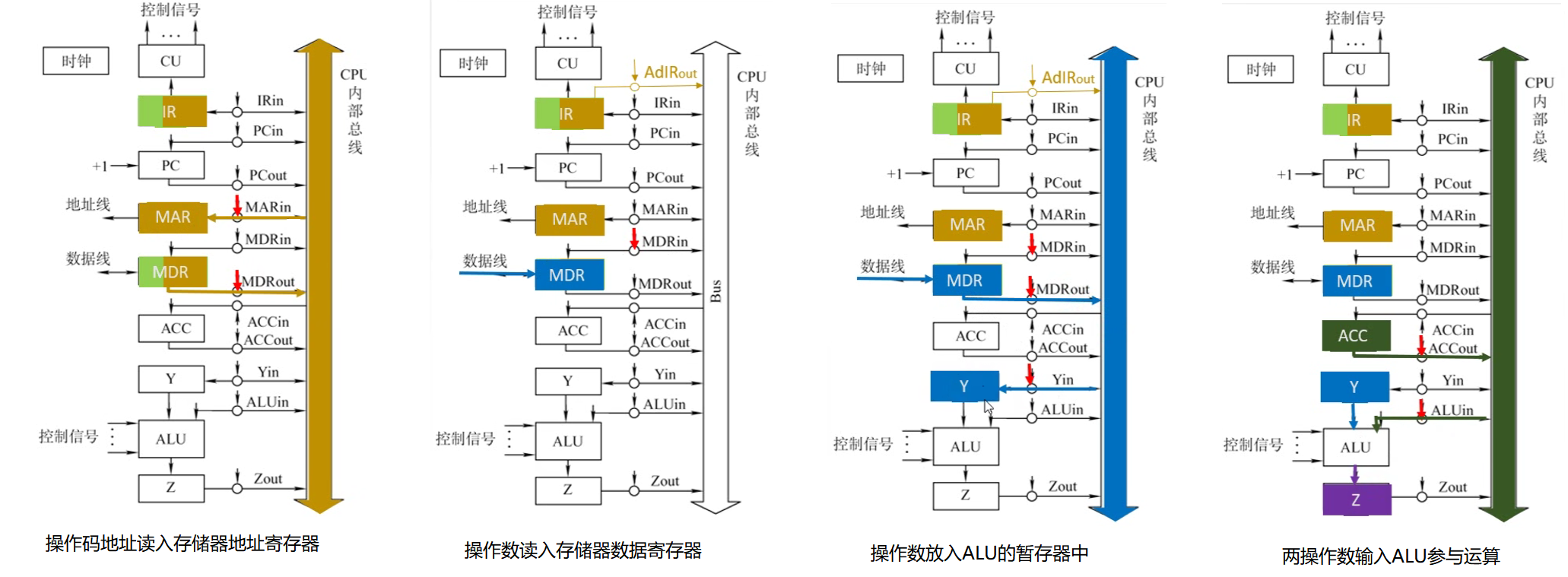

这是第一节的图,将其部件换到一边:

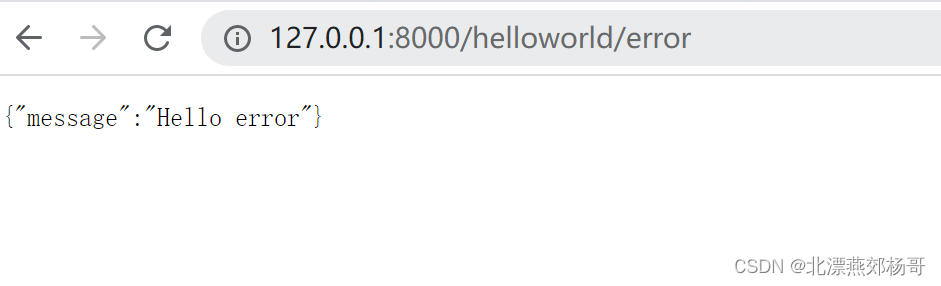

5.3.1.1 CPU内部单总线方式

内部总线是指同一部件,如CPU内部连接各寄存器及运算部件之间的总线;

系统总线是指同一台计算机系统的各部件,如CPU、内存、通道和各类I/O接口间互相连接的总线。

如MAR和MDR作为CPU和主存之间信息交流的寄存器,对外连接地址总线和数据总线

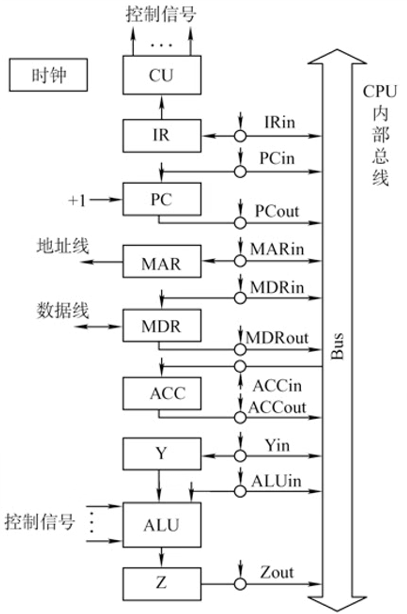

-

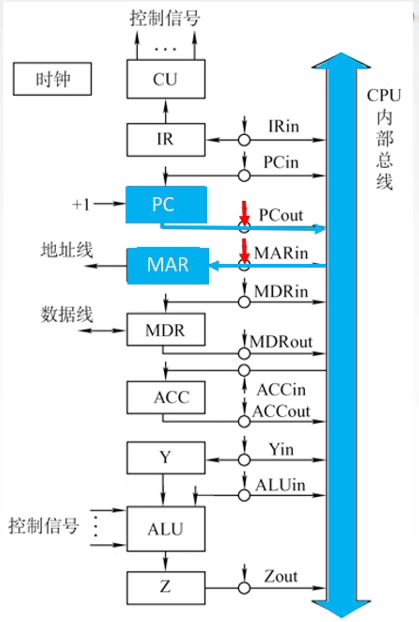

寄存器之间数据传送,比如把PC内容送至MAR,实现传送操作的流程及控制信号为:

(PC)→Bus PCout有效,PC内容送总线

Bus→MAR MARin有效,总线内容送MAR

-

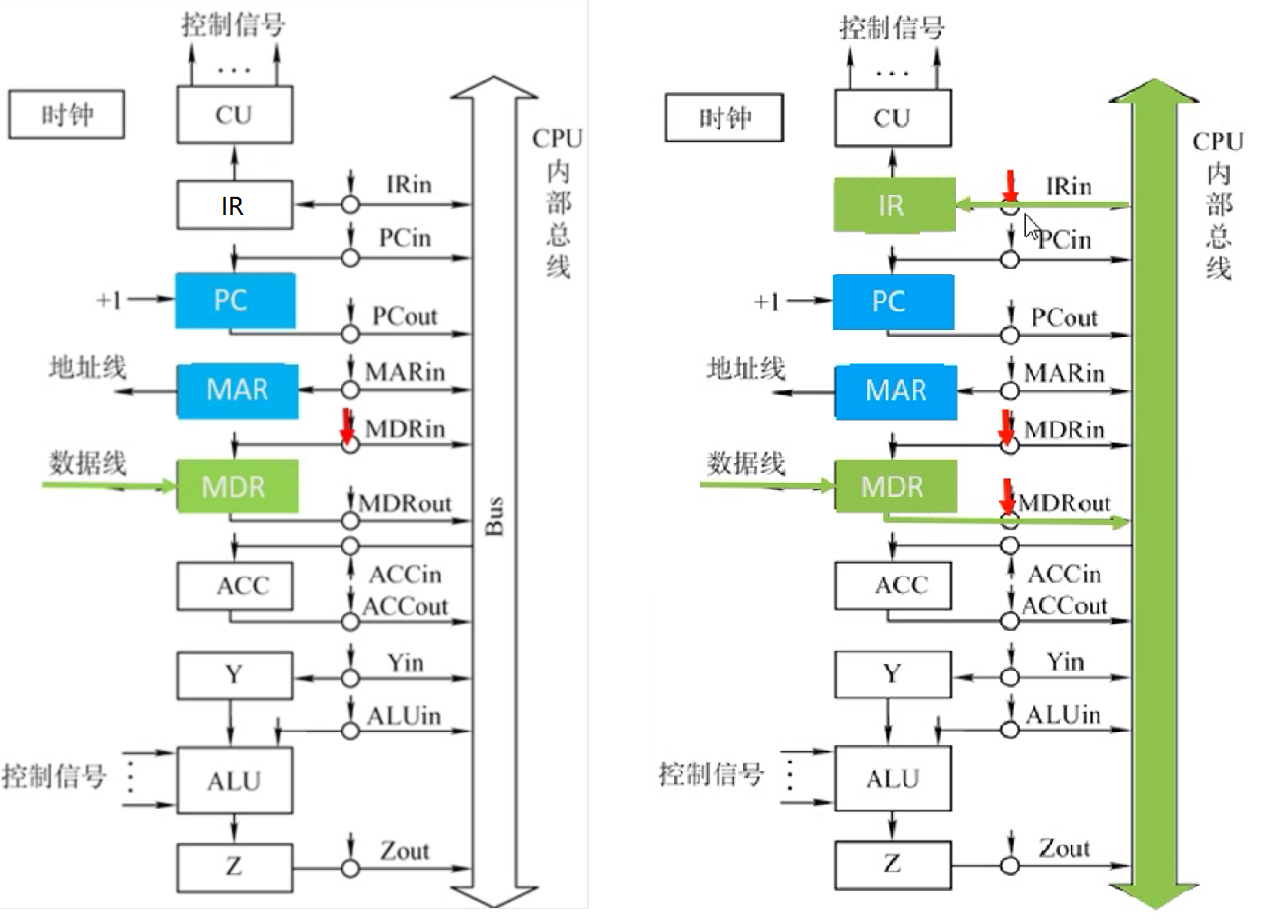

主存与CPU之间的数据传送

比如CPU从主存读取指令,实现传送操作的流程及控制信号为-

(PC)→Bus→MAR PCout和MARin有效,现行指令地址→MAR

-

1→R CU发读命令(通过控制总线发出,图中未画出)

-

MEM(MAR)→>MDR MDRin有效(此处有歧义,MDR一般需要和主存和CPU内部总线交流,所以一般会配用两套总线,此处指的是控制MDR和主存的控制信号)

-

MDR →Bus→IR MDRout和lRin有效,现行指令→IR

-

-

执行算数或逻辑运算

比如现在IR指令寄存器中存的是当前需要执行的指令,由指令的操作码交给控制系统CU便可知道为加法指令,此时需要取操作数:

Ad(IR))→Bus)→MAR MDRout和MADin有效 或AdIRout和MARin有效(如果有提供指令寄存器对外的读口的话)

1→R CU发读命令

MEM(MAR)→数据线→MDR MDRin有效(此处有歧义,MDR一般需要和主存和CPU内部总线交流,所以一般会配用两套总线,此处指的是控制MDR和主存的控制信号)

MDR→Bus→Y MDRout和Yin有效,操作数→Y

(ACC)+(Y)→Z ACCout和ALUin有效,CU向ALU发送加命令Z→ACC Aout和ACCin有效,结果→ACC(图中没给出)

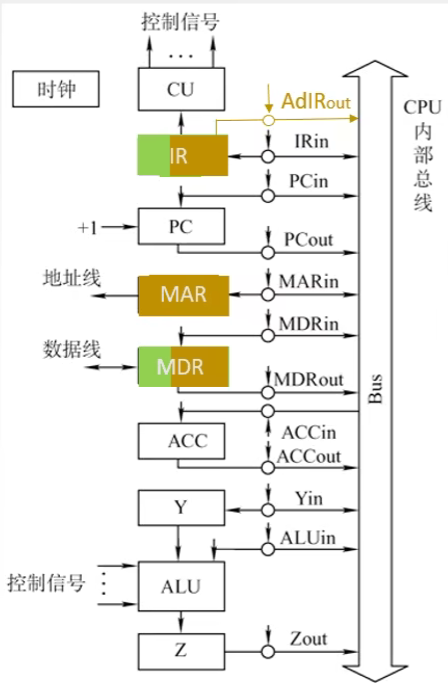

为什么MDR有效,因为图中IR指令寄存器对外没有提供读接口,并且此时MDR存储器数据寄存器和IR指令寄存器中存储的内容都是一样的,所以由MDR来代替IR,将操作码地址交给MAR

当然如果指令寄存器提供了对外读的功能,AdIRout,那么该指令也可以是AdIRout和MARin有效

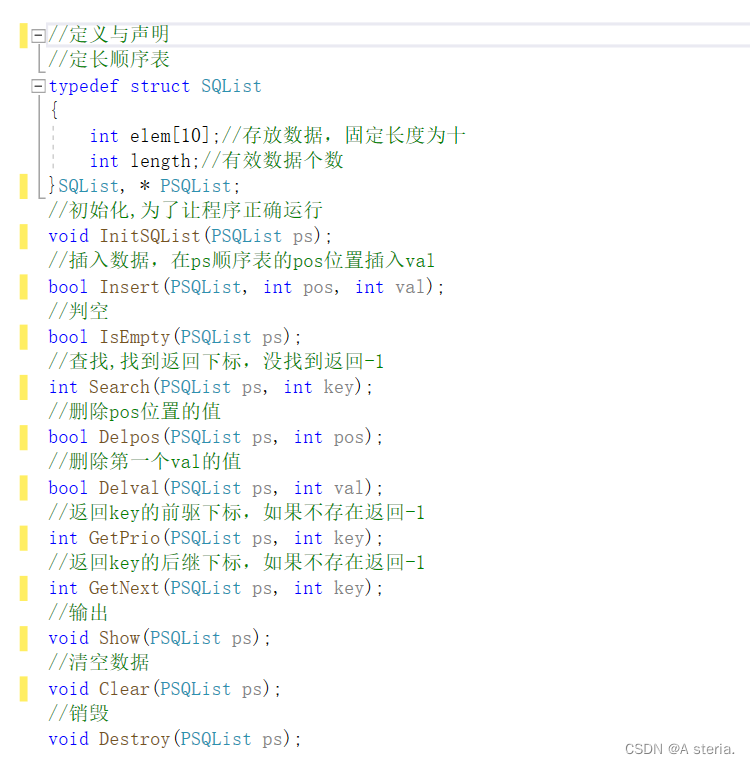

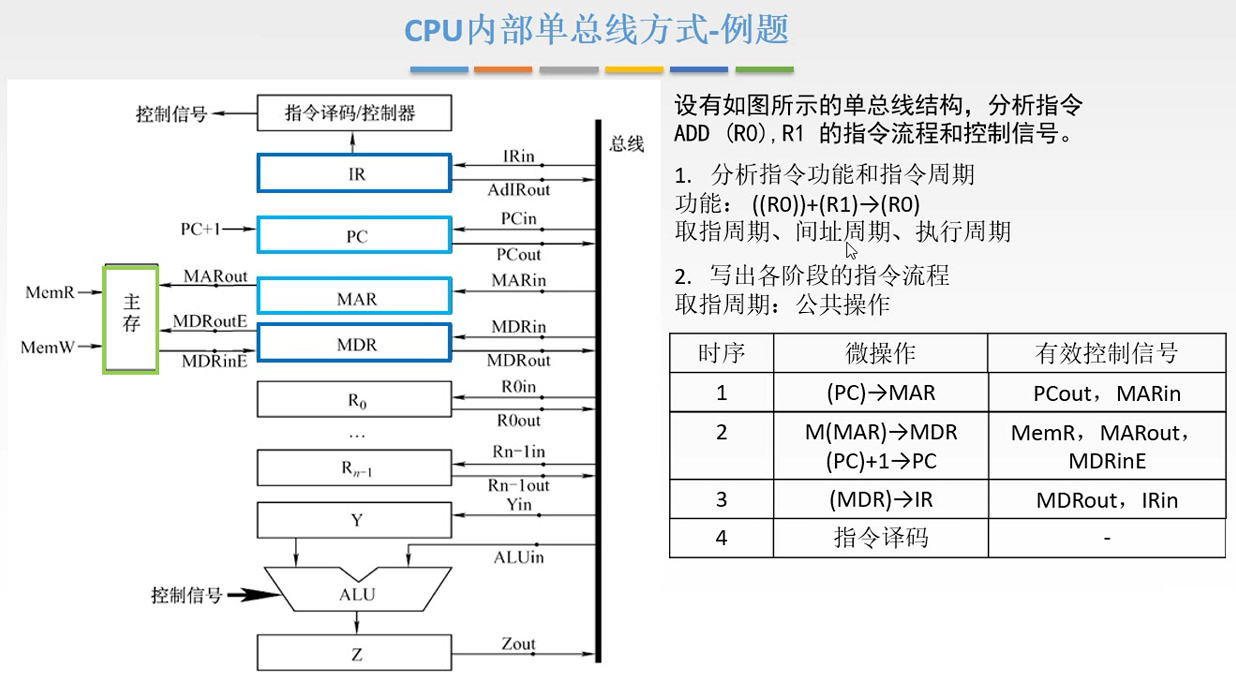

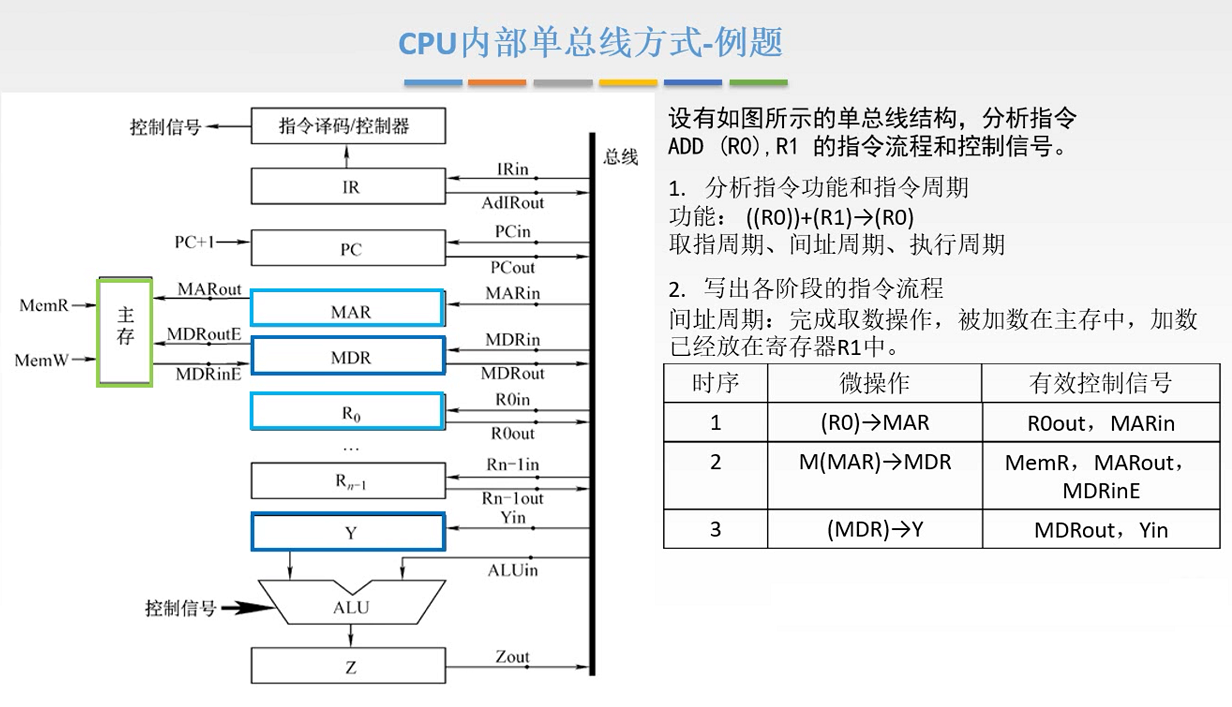

5.3.1.2 例题

注意题目中指令是(R0)意思为R0寄存器存储的内容是操作数的地址,并且R0寄存器存储的内容是结果返回的地址(也就是最后一步,R0初始的内容被记录在MAR中,所以有(MDR)→M(MAR))

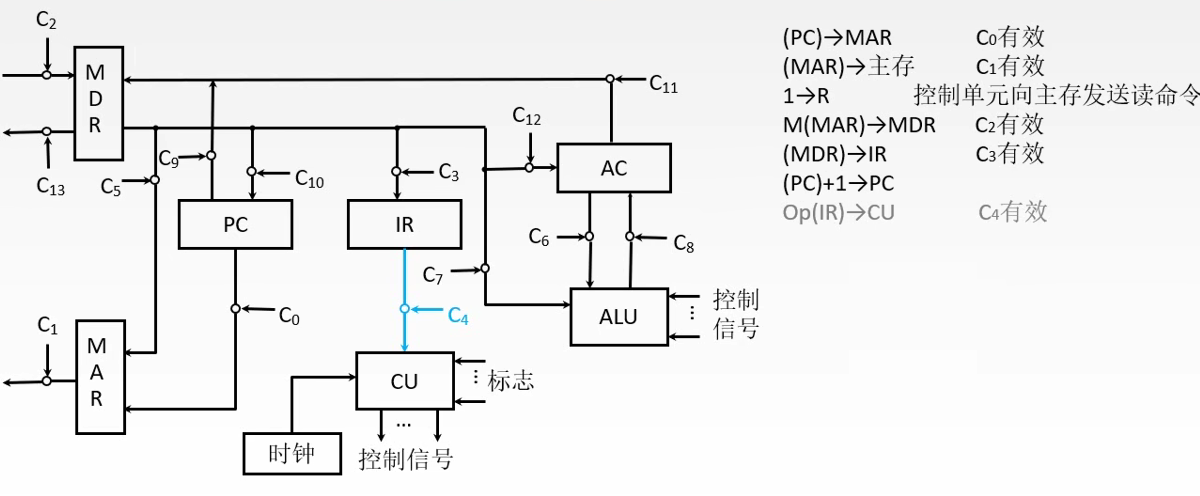

5.3.2 数据通路-专用数据通路

专用数据通路和CPU内部总线方式,数据流动方式是一样的。只是数据不再进过总线,部件之间有自己的连接,通过线路上控制信号协调工作完成数据流通。(这里以取指周期为例,分析数据流通,其余的可以自己类比CPU内部总线的方式)

-

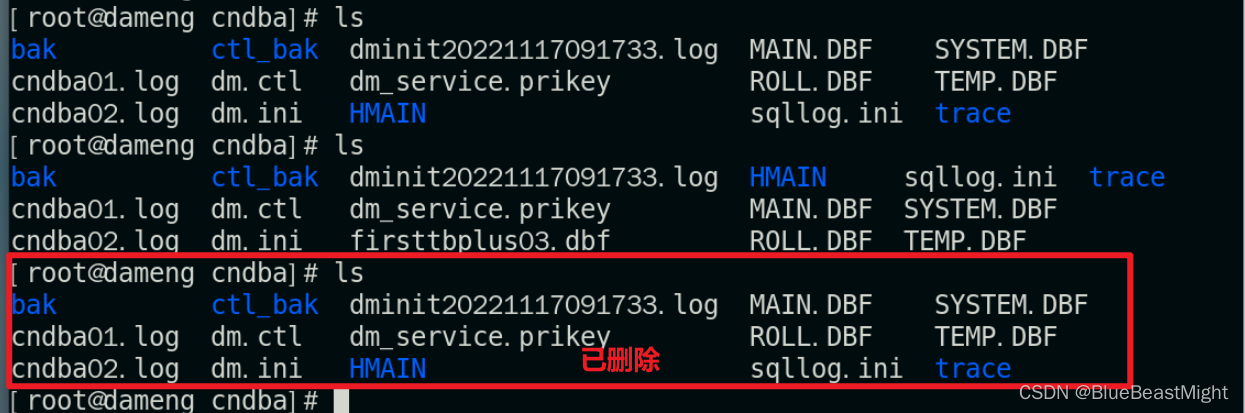

专用数据通路-取指周期

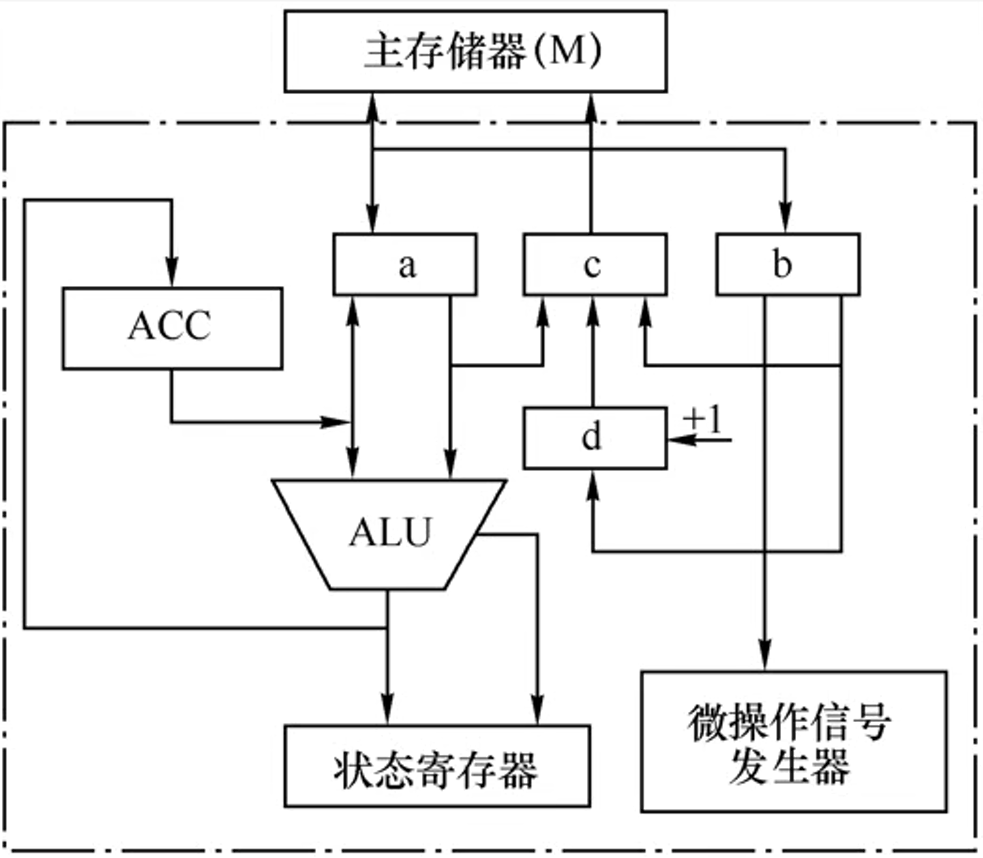

5.3.2.1 例题

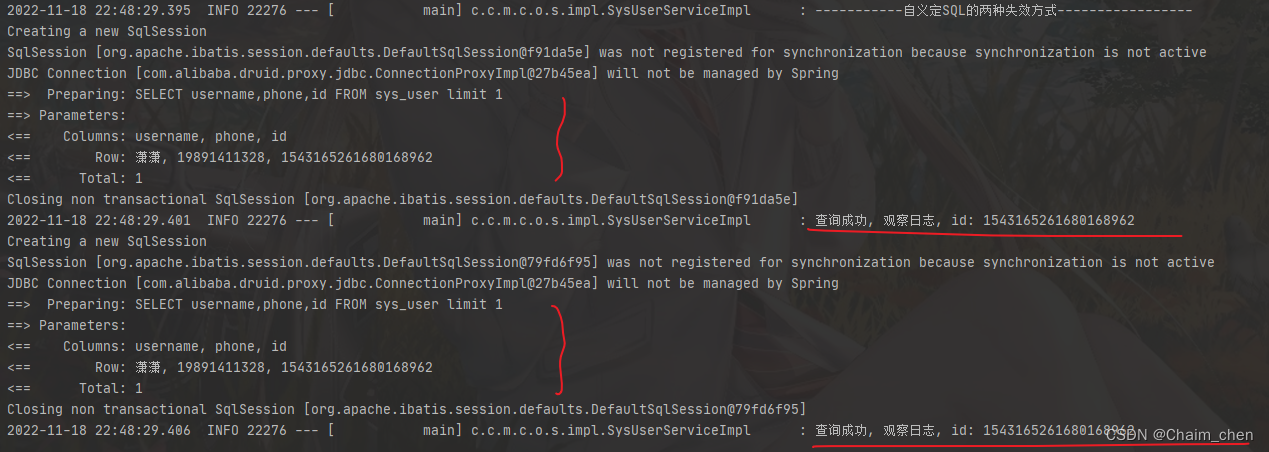

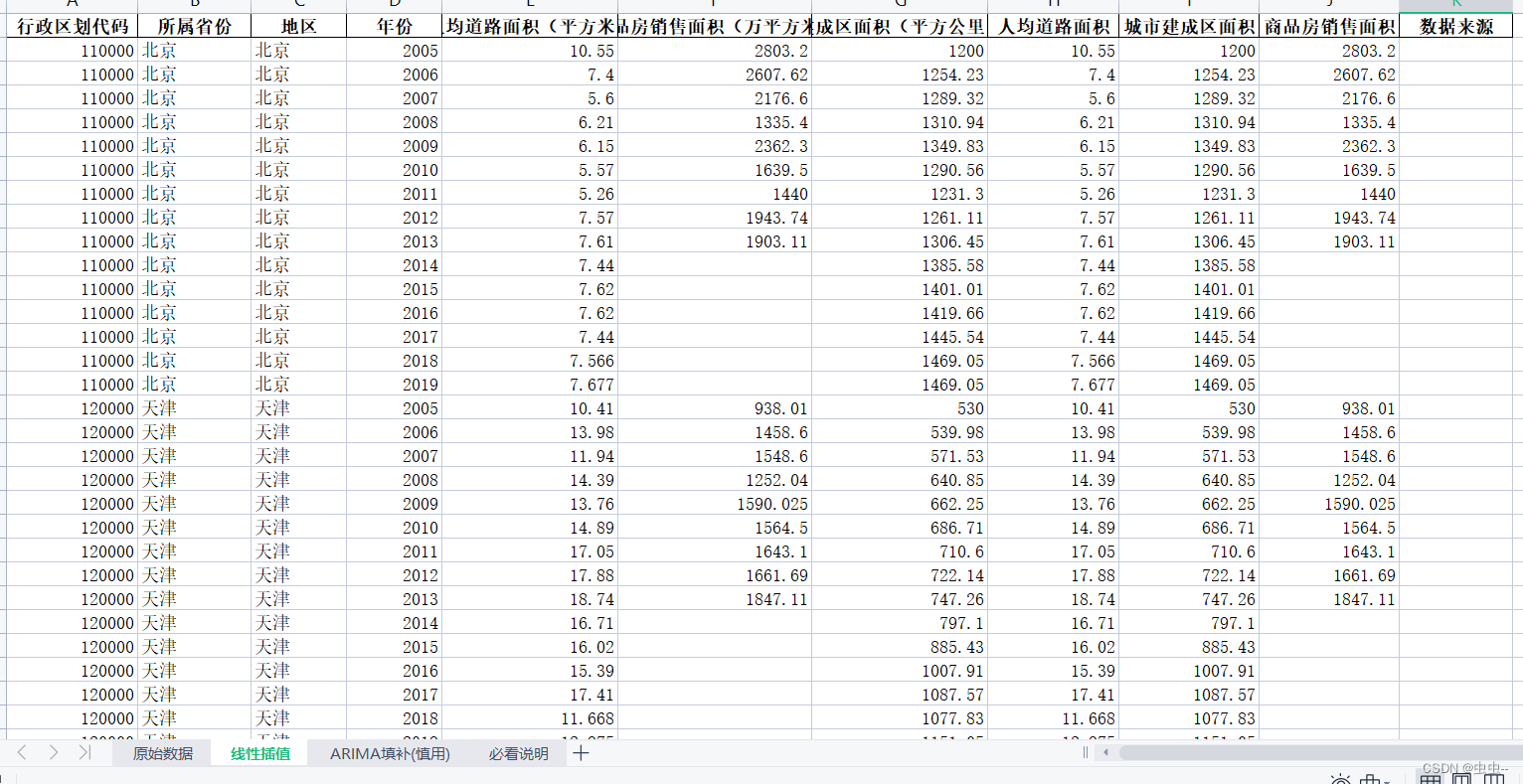

下图是一个简化了的CPU与主存连接结构示意图(图中省略了所有的多路选择器)。其中有一个累加寄存器(ACC)、一个状态数据寄存器和其他4个寄存器:主存地址寄存器(MAR)、主存数据寄存器(MDR)、程序寄存器(PC)和指令寄存器(IR),各部件及其之间的连线表示数据通路,箭头表示信息传递方向。

要求:

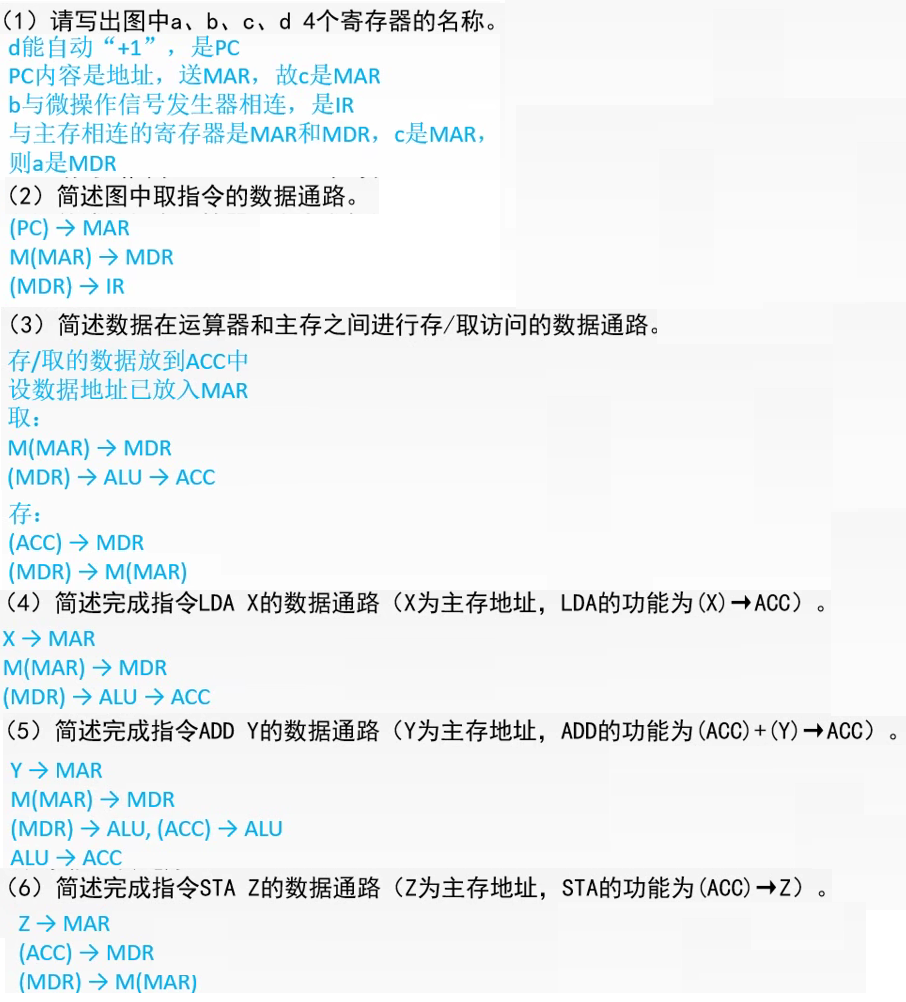

- 请写出图中a、b、c、d 4个寄存器的名称。

- 简述图中取指令的数据通路。

- 简述数据在运算器和主存之间进行存/取访问的数据通路。

- 简述完成指令LDA X的数据通路(X为主存地址,LDA的功能为(X)→ACC)。

- 简述完成指令ADD Y的数据通路(Y为主存地址,ADD的功能为(ACC)+(Y)→ACC)。(6)简述完成指令STA Z的数据通路(Z为主存地址,STA的功能为(ACC)→z)。

答案

图,图的遍历,最小生成树,最短路径算法详解](https://img-blog.csdnimg.cn/img_convert/80156463a3a4d0bcc5b1f36bf81807d9.png)