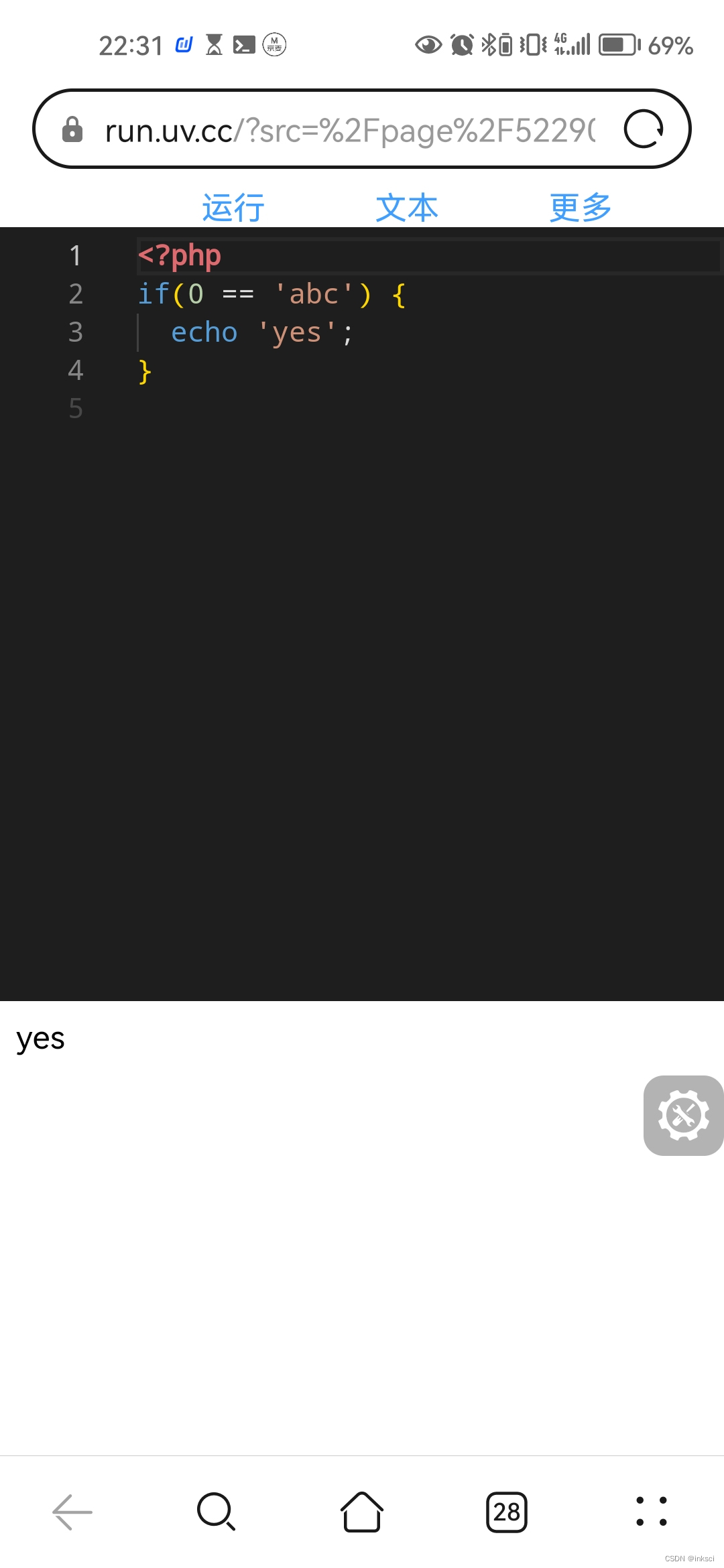

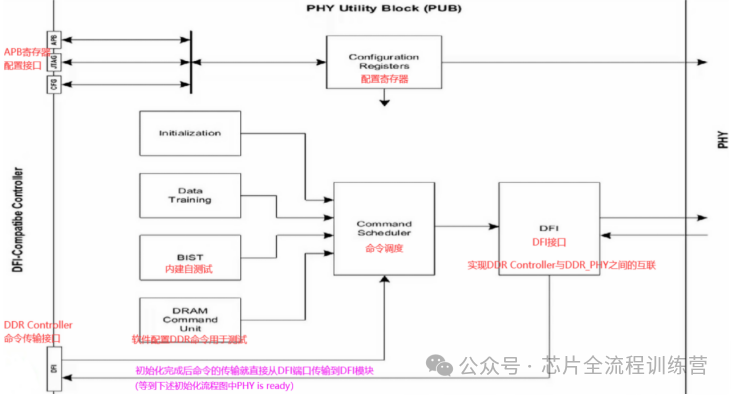

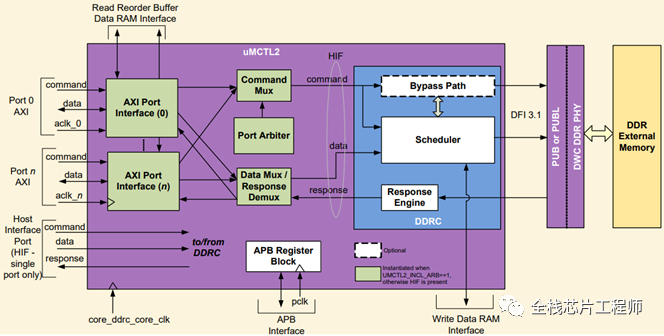

Memory子系统主要由DDR Controller和DDR_PHY(含DDR_IO)两个部分组成。DDR Controller主要承担其它子系统(如CPU)与Memory子系统进行数据交互时的传输效率及调度,DDR_PHY主要负责数据交互过程中的传输速度。

DDR内存接口IP解决方案包括DDR控制器、PHY和接口。当我们提到DDR内存子系统时,我们指的是主机片上系统(SoC)控制和访问DDR内存,以及主机和DDR内存设备之间的接口和互连(通常是PCB),以及DDR SDRAM设备本身。

·DDRC通过AXI接受到来自Master的读写命令

·将来自master的命令转为DDR读写时序序列

·通过DFI协议传给PHY

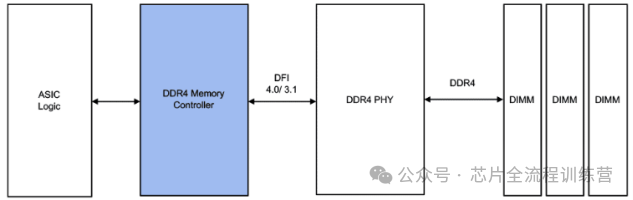

DFI接口如下:

景芯DDR PHY

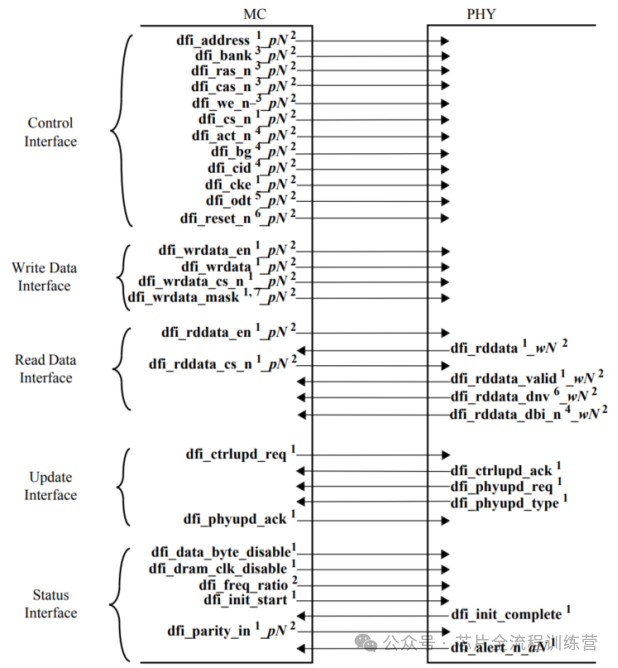

DDR PHY(物理层接口)是存储控制器和DRAM颗粒之间的桥梁,负责数据的传输速度和时序控制。DDR PHY的结构和功能如下:

1.DDR PHY结构组成:DDR PHY主要由Soft IP和Hard IP两部分组成。Soft IP指的是PUB模块(PHY Utility Block),它负责PHY的初始化、training及控制逻辑,支持自动化的DQS gate training、Delay line 校准和VT补偿等功能。

2.PUB模块功能:PUB模块支持最多4个Rank,可以配置为单数据通道或双通道数据配置,并且能够完成自动化Write Leveling、Write、Read的data bit deskew以及DQ/DQS eye training等任务。

1.不支持SDRAM DLL off模式;

2.数据通路的位宽以8bit的增量递增;

3.支持最多4个Rank;

4.支持单数据通道或者双通道数据配置;

5.能够完成PHY的初始化、training及控制逻辑;

6.支持自动化DQS gate training;

7.支持Delay line 校准和VT 补偿;

8.支持自动化Write Leveling;

9.支持自动化Write、Read的data bit deskew;

10.支持自动化DQ/DQS eye training;

11.支持APB或其它通用接口配置寄存器;

12.支持DFI接口;

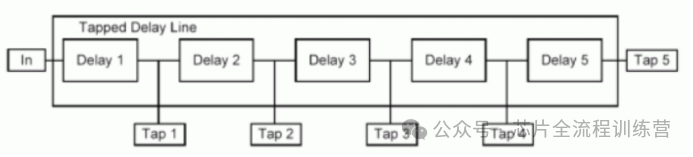

3.Delay line校准:在PLL初始化完成后,进行Delay line calibration,以满足DDR传输过程中data path的时序要求。Delay line由基本的逻辑门组成,包括LCDL(局部校准延迟链)和MDL(主延迟链),它们在初始化和实际操作过程中都需要进行校准。

·LCDL:Local Calibration Delay line,局部校准延迟链,在初始化Delay line校准时只进行一次;

·MDL:Master Delay Line,主延迟链,除了初始化时需要进行校准外,在后续的实际操作过程中任需要不断地进行校准(周期测量)。

数据传输过程中,一般希望时钟CK边沿与DQ/DQS满足90°的相位关系,即CK边沿位于DQ/DQS的正中间位置,但在实际传输过程中通常会存在误差,而Delay line就是为了对相位偏差进行调整,从而满足speed需求。由于后续输出传输会用到Delay line对信号进行一些相位补偿,所以初始化时需要首先对Delay line进行校准。Delay line主要有一些基本的逻辑门组成。

4.Ddift漂移检测和补偿:由于电压和温度变化,Delay line的延迟效果会存在差异,即漂移。漂移检测和补偿机制可以避免漂移对传输过程的影响。

同一条Delay line延迟链在不同的电压与温度下,延迟效果也会存在差异,这种现象被称之为漂移。为了避免漂移对传输过程的影响,就需要有检测漂移变化并对其进行补偿的机制。初始化之后,DATX8中的主延迟线(MDL)会持续的以选择的延迟时间为单位测量DDR的时钟,直到由于温度变化导致周期发生变化。

5.Impedance阻抗校准

阻抗校准时,需要开启ODT功能,具体景芯DDR教程已经讲过ODT原理,此处不再赘述。

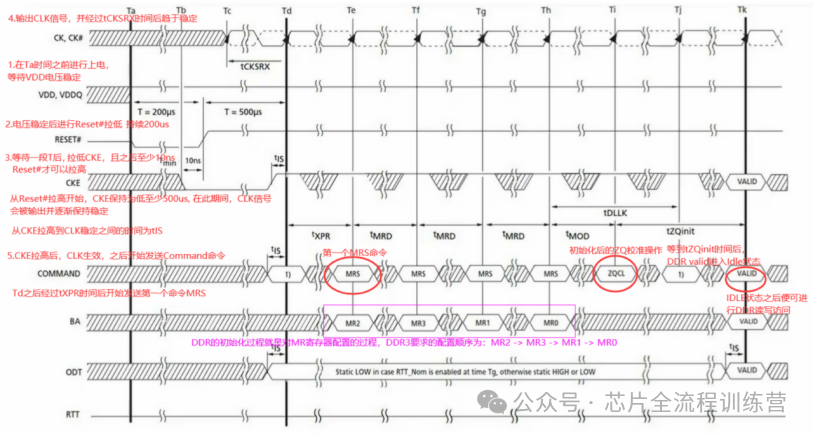

6.SDRAM初始化:SDRAM初始化过程可以由PUB或者DDR Controller执行,需要先配置相关的寄存器时序参数,然后初始化步骤如下,包括RESET#、CKE信号的操作,访问MR寄存器,以及ZQ校准等。

1.上电后,RESET#复位信号被拉低至少200us;

2.复位信号拉低后,CKE信号拉低并至少保持500us;

3.500us之后,CKE可以再次拉高;

4.CKE拉高后,等待至少tXPR时间,之后便可以对DDR寄存器进行访问;

5.依次访问MR寄存器,MR2 -> MR3 -> MR1(使能DLL) -> MR0(复位DLL)。

6.发起ZQ校准命令;

7.等待至少512个DDR clock,保证DLL lock住(tDLLK)并保证ZQ校准完成(tZQinit);

8.接下来便可以对DDR memory进行正常访问。

注意,DDR相关的时序参数:

·tXPR:DDR上电复位后,从CKE拉高到发出第一个有效的命令MRS之间的最小时间间隔;

·tMRD:DDR初始化过程中,两个连续的MRS命令之间持续的最小时间间隔;

·tMOD:MRS命令发送完毕后,让所有寄存器生效需要等待的时间;

·ZQCL:上电初始化之后,对DDR内部的ODT打开进行信号校准操作,属于长延时的操作;

·tZQinit:等待ZQCL校准完成的时间,至少需要512个clock;

·tDLLK:在MR0配置时,同时需要使能DLL,让颗粒中的DLL开始工作,而使能DLL至少需要保持的时间即为tDLLK.

7.DDR Training流程:包括Write Leveling、DQS Gate Training和Data eye Training,这些流程的目的是为了优化信号质量,确保数据的正确传输。

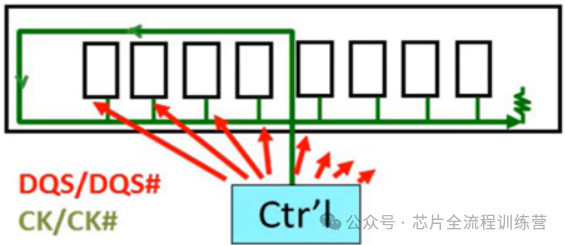

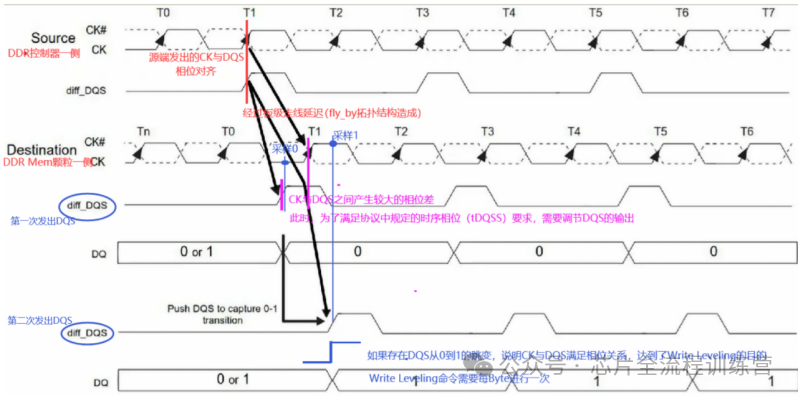

Write Leveling(写数据过程中的training)

为了获取更好的信号质量,DDR3的Mem颗粒采取了一种fly_by的拓扑结构,该结构中所有的Mem颗粒会复用CLK、Address及Command命令信号,(数据DQS/DQ信号不会被复用),这使得每一片Mem颗粒的时钟CLK和数据DQ/DQS的延迟不一样。

Write Leveling目的:不断增加Write DQS的延时以便满足CK与DQS之间的相位关系)

实际的DDR协议中规定了时钟CLK与写数据的DQ/DQS命令之间需满足一定的相位关系(tDQSS、tDSS、tDSH),而fly_by结构引起的颗粒的时钟CLK和数据DQ/DQS的延迟不一致通常难以满足二者之间的相位需求。所以引入了Write Leveling命令就是为了对写数据过程中这种相位差进行不断的调整,直到满足实际需求。注意,DQS的脉冲发送方式不同于CK,CK只发送一次脉冲,DQS依次不断发送脉冲进而通过Write Leveling不断改变DQS延时调整相位。

DQS Gate Training(读数据过程中的training)

在读数据过程中,DDR Controller发出读数据命令经过DDR_PHY传输给DDR memory颗粒,然后mem颗粒收到读数据Command后经过一段时间后会将数据反馈回DDR Controller。

在读数据前后,分别存在一段前导码和一段后导码。当前导码/后导码稳定后,在沿DQS/DQS#的交叉点进行采样时一般不会出现问题。但是,在前导码/后导码形成并持续时间内由于可能会存在缓冲波动(噪音、毛刺等),此时DQ采样就不可避免的会存在读错的情况。为了过滤掉噪声导致的不稳定因素,在DDR_PHY接收数据之前,颗粒通常需要给出比较干净的DQS信号避免数据读错,而设计中一般会采用DQS Gate信号来控制DQS的有效区间,进而避免前导码/后导码持续时间段内的噪音干扰读数据过程。

DQS Gate信号为什么需要进行Training呢?这是因为fly-by拓扑结构中CK、Address、Command信号的复用(DQS信号是通过CK信号产生),数据DQ信号是非复用的,这就导致DQ与DQS信号之间是异步关系,即Command到达不同颗粒存在先后顺序,而不同mem颗粒返回读数据则必然存在先后差异,所以需要对DQS Gate信号进行training,将其调整到规定的窗口区间。

Data eye Training(数据training)

Data eye Training的目的是为了让DQS/DQS#的采样交叉点恰好处于DQ eye数据信号的正中间,保证信号不会被漏采。

8. 物理设计方法:DDR PHY的物理设计关键在于时序路径的设计,包括时钟输入到输出信号的各个阶段,以及如何通过Innovus工具解决时序路径的时间预算、延时优化和路径对齐等问题]。

9. 内存初始化和校准序列:在系统复位后,PHY执行内部校准步骤,包括BISC、内存上电初始化序列、写入和读取数据路径的时序校准等。

10. LPDDR4/4X CS和CA训练:对于高频操作的LPDDR4/4X SDRAM,提供了一种对命令总线进行训练的机制,以确保信号与时钟对齐。

DDR3/4实战+SoC集成

DDR是SoC设计的关键技术,景芯SoC DDR4/3设计实战训练营将帮助您掌握DDR设计技术并成为芯片大拿。本门课程不仅教您学习DDR+PHY,还教您学会DDR的SoC集成、驱动、SoC仿真!

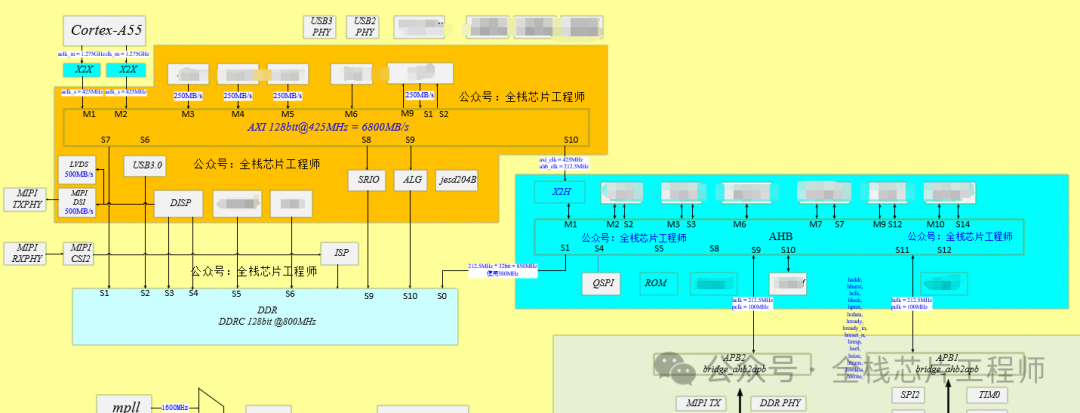

1)DDR课程所带的SoC系统架构如下:

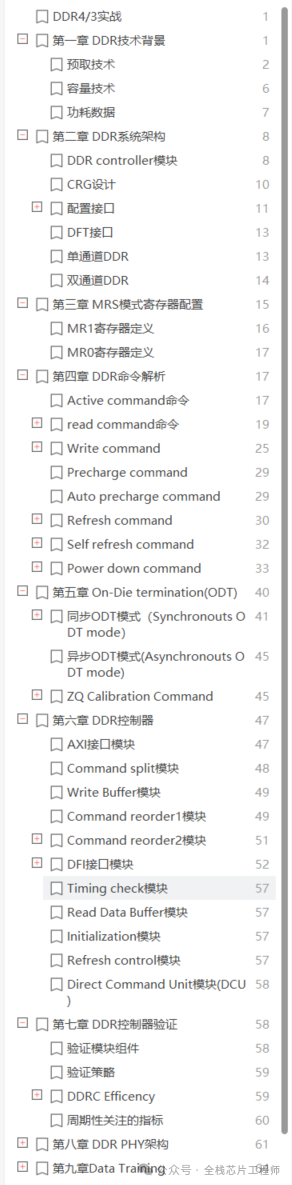

2)DDR课程架构

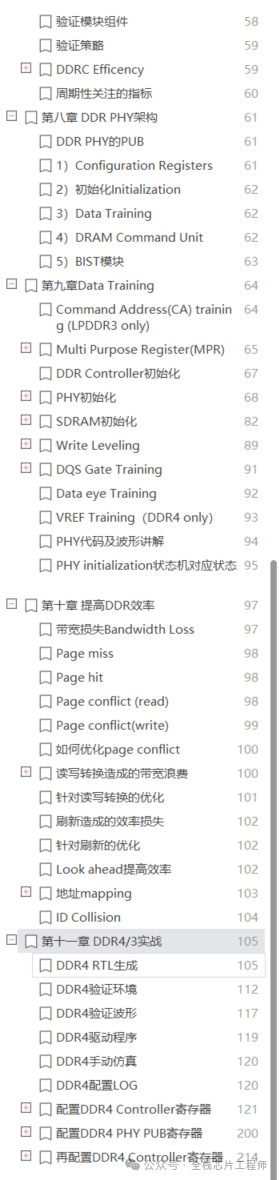

3)DDR课程目录如下:

以上就是今天分享的内容,如果您和小编一样渴求进步,想掌握芯片设计全流程,欢迎加入小编知识星球,疯狂成长,一起进步!早日成为芯片大佬!

![[译] How things get done on the Go Team](https://img-blog.csdnimg.cn/img_convert/0d7023e7d624fee39f5751eb6512c0fb.png)