🧊🧊🧊单项选择题(共40道)

🧊数据结构(11道)

🥥1.2.考察的都是栈和队列的入栈(队)出栈(队)问题

这道题目重点是掌握各种栈和队列的入栈(队)出栈(队)方法,这里提一嘴第2题,这道题目其实有个小窍门,就是说,只要该选项是可以被在队列中排列出来的,那么他就可以成功出队。

🥥3.线索二叉树

线索二叉树:通过添加额外的指针,使得在遍历时可以直接访问前驱节点和后继节点,而无需递归。这些额外的指针称为"线索",因此线索二叉树的关键特点是:对于每个节点,除了左右子节点的指针外,还有指向中序遍历的前驱节点和后继节点的线索。

前驱节点:搜索顺序中当前节点前边的那个节点

后继节点:搜索顺序中当前节点后边的那个节点

线索的构建准则:左子树为空,则左指针指向前驱节点;右子树为空,则右指针指向后继节点

这道题目按照后序遍历方式,那么搜索顺序是 d b c a,根据上述构建准则可得出结果。

🥥4.平衡二叉树的平衡过程(各种旋转)

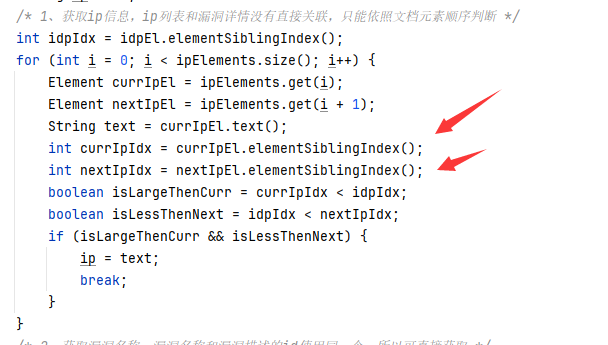

这道题目会遇到先右旋后左旋的情况:

旋转判断过程:

- 找到第一个不平衡节点(|左子树高度-右子树高度|>1),基于该节点判断旋转方式

- 根据形态选择合适的方法和方向进行旋转,都是将三个的中间位置的节点放到根节点处,需要注意的是,比如这道题目中的48,在旋转后可能移动到兄弟节点上了,注意保证搜索二叉树的特性(小中大)

图片摘自平衡二叉树旋转_平衡二叉树的旋转-CSDN博客,感兴趣的同学可以移步链接看一下具体过程。

🥥5.树的结点数量

这道题目需要构建一个等式。假设共n个节点,n5表示度为5的节点数量,对树来说就是有n-1条边也就是n-1个度,据此得出等式:

- n=n0+n1+n2+n3+n4

- n-1=n1+2*n2+3*n3+4*n4

据此可以解得n0也就是叶子节点共有82个。

🥥6.哈夫曼树

哈夫曼树:一个二叉树,它的叶子节点对应于要编码的字符或符号,每个叶子节点带有一个权值(频率)。构造的目标是使得权重较高的字符具有较短的编码,权重较低的字符具有较长的编码,从而实现压缩。

哈夫曼树的构造过程:从初始的叶子节点开始构建哈夫曼树,通过不断合并权重最小的两棵树(可以是单个节点也可以是子树),生成新的父节点。

根据哈夫曼树的定义和构造过程,我们可以知道,哈夫曼树是带权路径长度最小的二叉树,不一定是完全二叉树(最后一层从左到右分布,左边全满);由于两两结合,所以没有度为1的结点。

🥥7.连通图中边的数量

要保证无向图G在任何情况下都是连通的,即任意变动图G中的边,G始终保待连通,首先需要G的任意6个结点构成完全连通子图GI, 需n(n-1)/2 = 6x(6-1)/2 = 15条边, 然后再添一条边将第7个结点与Gl连接起来, 共需16条边。

❓❓❓这道题目我其实是有些疑问的,如果说要保证变动G中的任意边都要求保持连通的话,那我如果动的是完全来南通子图GI和第7个节点的那个边岂不是也不连通了?所以不太懂这道题,有没有懂的uu能在评论区帮忙解答一下?欢迎大家一起讨论,我们评论区见~

🥥8.拓扑序列

经典的拓扑序列求取问题,只要把握住,“每次选取的点都是没有入度的点,选完后把这个点及其连接的边一同删掉”,就可以了,写出所有可能的拓扑序列,最后发现有三种:abced、abecd、aebcd。

🥥9.折半查找的对比次数问题

折半查找法在查找成功时进行的关键字比较次数最多为Llog2(n)」+ 1, 即判定树的高度;折半查找法在查找不成功时进行的关键字比较次数最多为Llog2(n)」+ 1。 题中n = 16, 因此最多比较Llog2(16)」+1=5次。 也可以画出草图求解。

🥥10.递归快排的特点

快递排序的递归次数与元素的初始排列有关。若每次划分后分区比较平衡,则递归次数少; 若划分后分区不平衡, 则递归次数多。但快速排序的递归次数与分区处理顺序无关, 即先处理较长的分区或先处理较短的分区都不影响递归次数。 此外,可以形象地把快速排序的递归调用过程用一个二叉树描述,先处理较长或较短分区,可以想象为交换某一递归结点处的左右子树, 这并不会影响树中的分支数 。

🥥11.排序算法问题

这道题目主要是可以发现,每一趟排序都将最大的数放到了该到的位置,所以是冒泡排序(也可能是选择排序,这个重点看是两两交换的还是只有两个元素交换的,前者是冒泡,后者是选择)

希尔排序:希尔排序的基本思想是将原始数组分成若干个子序列,对每个子序列进行插入排序,然后逐步缩小子序列的间隔,直至间隔为1,最后对整个序列进行一次插入排序。

基数排序:基数排序是一种非比较性的排序算法,适用于处理整数或字符串这类具有固定位数的数据。基数排序通过将数据按照每一位进行排序,从最低有效位到最高有效位,以实现整体的排序效果。

🍨🍨🍨需要排序算法总结的宝子评论区告诉我,呼声高的话整理各类排序算法哦~~~

🧊计算机组成原理(11道)

🥥1.影响程序执行时间的因素

- CPU时钟频率(主频)越高,完成指令的一个执行步骤所用的时间就越短,执行指令的速度越快,I正确。

- 数据通路的功能是实现CPU内部的运算器和寄存器以及寄存器之间的数据交换,优化数据通路结构,可以有效提高计算机系统的吞吐量,从而加快程序的执行,II正确。

- 计算机程序需要先转化成机器指令序列才能最终得到执行,通过对程序进行编译优化可以得到更优的指令序列,从而使得程序的执行时间也越短,III正确。

🥥2.溢出问题

这道题目其实考的并不是补码乘法运算,而是考察进制转换。FEH转为二进制是11111110,补码为10000001+1=10000010,也就是-2,同理得出r2=-14, r3=-112, r4=-8, 得r2 x r3=1568, 远超出了表示范围,发生溢出。

🥥3.数据类型转换

题中三种数据类型的精度从低到高为int-float-double, 从低到高的转换通常可以保持其值不变,I 和III正确,而从高到低的转换可能会有数据的舍入,从而损失精度。 对于II, 先将float型的f转换为int型,小数点后的数位丢失,故其结果不为真。 对于IV, 初看似乎没有问题,但浮点运算d+f时需要对阶 ,对阶后f的尾数有效位被舍去而变为 o, 故d+f仍然为d, 再减去d后结果为 o, 故 IV结果不为真。 此外,根据不同类型数据混合运算的 ” 类型提升” 原则,在IV中,等号左端的类型为double型,结果不为真。

🥥4.芯片分组地址问题

8K×8 / 2K×4 = 4×2,也就是4组,每组2块,根据2K可以得出每块的大小是0000111111111111=07FFH,据此得到4组的范围,进而得出芯片所在地址

🥥5.RAM vs ROM

这道题选A,ROM只可读,不可用做cache,cache多由高速SRAM构造。DRAM需要定期刷新,而ROM不需要刷新。

🥥6.访存命中问题

Cache中存放的是主存的一部分副本,TLB(快表)中存放的是Page(页表)的一部分副本。在同时具有虚拟页式存储器(有TLB )和Cache的系统中,CPU发出访存命令,先查找对应的Cache块。

- 若Cache命中,则说明所需内容在 Cache 内, 其所在页面必然已调入主存,因此Page必然命中,但TLB 不一定命中。

- 若Cache不命中,并不能说明所需内容未调入主存,和TLB、Page命中与否没有联系。但若TLB命中,Page也必然命中;而当Page命中,TLB则未必命中,故D不可能发生。

主存、Cache、TLB和Page的关 系如下图所示。

【提示】本题看似既涉及虚拟存储器又涉及Cache, 实际上这里并不需要考虑Cache命中与否。 因为一旦缺页,说明信息不在主存, 那么TLB 中就一定 没有该页表项,所以不存在TLB命中、Page缺失的情况,也根本谈不上访问 Cache 是否命中。

🥥7.寄存器与程序员可见性

首先必须明白 “ 汇编语言程序员可见 ” 的含义,即汇编语言程序员通过汇编程序可以对某个寄存器进行访问。 汇编程序员可以通过指定待执行指令的地址来设置PC的值,如转移指令、子程序调用指令等。 而IR、MAR、MDR 是CPU的内部工作寄存器,程序员无法直接获取和设置它们的值,也无法直接对它们进行 其他 操作,所以对程序员不可见。

【提示】1指令寄存器IR中的内容总是根据PC所取出的指令代码。2在CPU的专用寄存器中,只有PC和PSWR是汇编程序员可见的。

🥥8.流水线阻塞成因

🥥9.总线标准

典型的总线标准有: ISA、EISA、VESA、PCI、PCI-Expres s、AGP、USB、R S-232C等。A 中的CR T是纯平显示器;B 中的CPI 是每条指令的时钟周期数;C中的RAM 是半导体随机存储器、MIPS是每秒执行多少百万条指令数。

🥥10.中断服务程序执行顺序

注意,关中断、保存断点是硬件做的,开中断是服务程序做的,单级不能在处理阶段继续接收中断信号,所以要在返回前才开中断。

在单级(或单重) 中断系统中, 不允许中断嵌套。中断处理过程为:1关中断;2保存断点;3识别中断源;4保存现场;5中断事件处理;6恢复现场;7开中断;8中断返回。其中, 1~3由硬件完成,4~8由中断服务程序完成, 故选A。

🥥11.总带宽计算

刷新所需带宽=分辨率x色深X帧频= 1600 x 1200 x 24bit x 85Hz = 3916.SMbps, 显存总带宽的 50%用来刷屏, 于是需要的显存总带宽为 3916.SMbps/0.5= 7833.6Mbps=7834Mbps。

🧊创作不易,点个赞吧~

🧊点赞收藏不迷路~