一、静态时序分析:

静态时序分析(Static Timing Analysis)简称 STA,采用穷尽的分析方法来提取出整个电路存在的所有时序路径,计算信号在这些路径上的传播延时,检查信号的建立和保持时间是否满足时序要求,通过对最大路径延时和最小路径延时的分析,找出违背时序约束的错误并报告。

STA 不需要输入向量就能穷尽所有的路径,且运行速度很快、占用内存较少、覆盖率极高,不仅可以对芯片设计进行全面的时序功能检查,而且还可以利用时序分析的结果来优化设计。所以 STA 不仅是数字集成电路

设计 Timing Sign-off 的必备手段,也越来越多地被用到设计的验证调试工作中。

STA 在 FPGA 设计中也一样重要,但不同于一般数字集成电路的设计,FPGA 设计中的静态时序分析工具一般都整合在芯片厂商提供的实现工具中。在 Vivado 中甚至没有一个独立的界面,而是通过几个特定的时序

报告命令来实现。

二、时序命令与报告

Vivado 中用于时序分析的命令主要有以下两条,且都有对应的图形化设置界面。

- report_timing_summary 主要用于实现后的 timing sigh-off

- report_timing 主要用于交互式的约束验证以及更细致具体的时序报告与分析

1.report_timing_summary命令

report_timing_summary 实际上隐含了 report_timing、report_clocks 、check_timing 以及部分的 report_clock_interaction 命令,所以我们最终看到的报告中也包含了这几部分的内容。

Timing Summary 报告把路径按照时钟域分类,每个组别下缺省会报告 Setup、Hold 以及 Pulse Width 检查最差的各 10 条路径,还可以看到每条路径的具体延时报告。

每条路径具体的报告会分为 Summary、Source Clock Path、Data Path 和 Destination Clock Path 几部分,详细报告每部分的逻辑延时与连线延时。用户首先要关注的就是 Summary 中的几部分内容,发现问题后再根据具体情况来检查详细的延时数据。其中,Slack 显示路径是否有时序违例,Source 和 Destination 显示源驱动时钟和目的驱动时钟及其时钟频率, Requirement 显示这条路径的时序要求是多少,Data Path 显示数据路径上的延时,Logic Level 显示这条路径的逻辑级数,而 Clock Path Skew 和 Clock Uncertainty 则显示时钟路径上的不确定性。

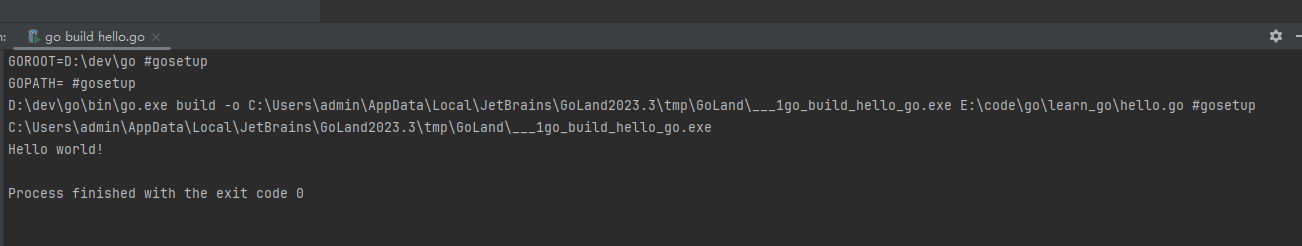

report_timing_summary示例

report_timing_summary

INFO: [Timing 38-91] UpdateTimingParams: Speed grade: -2, Delay Type: min_max.

INFO: [Timing 38-191] Multithreading enabled for timing update using a maximum of 32 CPUs

Copyright 1986-2022 Xilinx, Inc. All Rights Reserved.

-----------------------------------------------------------------------------------------------

| Tool Version : Vivado v.2022.1 (lin64) Build 3526262 Mon Apr 18 15:47:01 MDT 2022

| Date : Fri May 24 18:24:22 2024

| Host : deep-PowerEdge-R730xd running 64-bit Ubuntu 20.04.6 LTS

| Command : report_timing_summary

| Design : single_bit_syn

| Device : 7vx485t-ffg1157

| Speed File : -2 PRODUCTION 1.12 2014-09-11

------------------------------------------------------------------------------------------------

Timing Summary Report

------------------------------------------------------------------------------------------------

| Timer Settings

| -----------------------------------------------------------------------------------------------

Enable Multi Corner Analysis : Yes

Enable Pessimism Removal : Yes

Pessimism Removal Resolution : Nearest Common Node

Enable Input Delay Default Clock : No

Enable Preset / Clear Arcs : No

Disable Flight Delays : No

Ignore I/O Paths : No

Timing Early Launch at Borrowing Latches : No

Borrow Time for Max Delay Exceptions : Yes

Merge Timing Exceptions : Yes

Corner Analyze Analyze

Name Max Paths Min Paths

------ --------- ---------

Slow Yes Yes

Fast Yes Yes

-----------------------------------------------------------------------------------------------------------

| Report Methodology

| ---------------------------------------------------------------------------------------------------------

Rule Severity Description Violations

--------- -------- ----------------------------- ----------

TIMING-9 Warning Unknown CDC Logic 1

TIMING-18 Warning Missing input or output delay 2

Note: This report is based on the most recent report_methodology run and may not be up-to-date. Run report_methodology on the current design for the latest report.

| check_timing report(check_timing)

Table of Contents

-----------------

1. checking no_clock (0) // There are 0 register/latch pins with no clock.

2. checking constant_clock (0)// There are 0 register/latch pins with constant_clock.

3. checking pulse_width_clock (0)// There are 0 register/latch pins which need pulse_width check

4. checking unconstrained_internal_endpoints (0) // There are 0 pins that are not constrained for maximum delay.// There are 0 pins that are not constrained for maximum delay due to constant clock.

5. checking no_input_delay (0)//There are 0 input ports with no input delay specified. There are 0 input ports with no input delay but user has a false path constraint.

6. checking no_output_delay (0)// There are 0 ports with no output delay specified. There are 0 ports with no output delay but user has a false path constraint There are 0 ports with no output delay but with a timing clock defined on it or propagating through it

7. checking multiple_clock (0)//There are 0 register/latch pins with multiple clocks.

8. checking generated_clocks (0)// There are 0 generated clocks that are not connected to a clock source.

9. checking loops (0)// There are 0 combinational loops in the design.

10. checking partial_input_delay (0)// There are 0 input ports with partial input delay specified.

11. checking partial_output_delay (0)// There are 0 ports with partial output delay specified.

12. checking latch_loops (0)// There are 0 combinational latch loops in the design through latch input

------------------------------------------------------------------------------------------------

| Design Timing Summary

| ----------------------------------------------------------------------------------------------

WNS(ns) TNS(ns) TNS Failing Endpoints TNS Total Endpoints WHS(ns) THS(ns) THS Failing Endpoints THS Total Endpoints WPWS(ns) TPWS(ns) TPWS Failing Endpoints TPWS Total Endpoints

------- ------- --------------------- ------------------- ------- ------- --------------------- ------------------- -------- -------- ---------------------- --------------------

2.845 0.000 0 6 0.043 0.000 0 6 4.650 0.000 0 5

All user specified timing constraints are met.

------------------------------------------------------------------------------------------------

| Clock Summary (report_clocks)

| -------------------------------------------------------------------------------------------------------------

Clock Waveform(ns) Period(ns) Frequency(MHz)

----- ------------ ---------- --------------

clk_a {0.000 5.000} 10.000 100.000

clk_b {5.000 15.000} 20.000 50.000

------------------------------------------------------------------------------------------------

| Intra Clock Table

| -----------------------------------------------------------------------------------------------------------------

Clock WNS(ns) TNS(ns) TNS Failing Endpoints TNS Total Endpoints WHS(ns) THS(ns) THS Failing Endpoints THS Total Endpoints WPWS(ns) TPWS(ns) TPWS Failing Endpoints TPWS Total Endpoints

----- ------- ------- --------------------- ------------------- ------- ------- --------------------- ------------------- -------- -------- ---------------------- --------------------

clk_a 2.845 0.000 0 3 0.043 0.000 0 3 4.650 0.000 0 2

clk_b 12.395 0.000 0 3 0.066 0.000 0 3 9.650 0.000 0 3

------------------------------------------------------------------------------------------------

2.补充:工艺上的知识:OCV(在芯片上的不确定性) 与 PVT (工艺/电压/温度)

-

OCV:即便是同一种 FF(触发器),在同一个芯片上不同操作条件下的延时都不尽相同,我们称这种现象为 OCV(on-chip variation)。OCV 表示的是芯片内部的时序偏差,虽然很细小,但是也必须严格考虑到时序分析中去。

-

PVT(Process / Voltage / Temperature)三 个方面,而 STA 要做的就是针对不同工艺角(Process Corner)下特定的时 序模型来分析时序路径,从而保证设计在任何条件下都能满足时序要求, 可以正常工作。通常 PVT 对芯片性能的影响如下图所示, 栅极间的距离越小,温度越低,电压越高,电平变换和门延迟越小就越好。

-

通俗的来讲:由于工艺的原因,在这些cornor下可能会有不同的性能。在FPGA设计中的静态时序分析一般仅考虑Best Case和Worst Case,也称作Fast Process Corner 和Slow Process Corner,分别对应极端的PVT条件。

Fast Corner Model: 最好的工艺+最低温度+最高电压下的模型;Slow Corner Model: 最差的工艺+最高温度+最低电压下的模型;在Vivado中,会对以上两个corner进行时序分析,并给出最差情况的报告。在setup中分析的是slow process corner,在hold中分析的是fast process corner。如果在在slow process corner模型下能满足setup的要求,那么其他模型也就都能满足;如果在fast process corner模型下能满足hold的要求,那么其他模型下也都能满足。

|Timing Details (report_timing)

From Clock: clk_a To Clock: clk_a

Setup : 0 Failing Endpoints, Worst Slack 2.845ns, Total Violation 0.000ns//暂无时序违例

Hold : 0 Failing Endpoints, Worst Slack 0.043ns, Total Violation 0.000ns

PW : 0 Failing Endpoints, Worst Slack 4.650ns, Total Violation 0.000ns

Max Delay Paths// 最大Timing_path

--------------------------------------------------------------------------------------

Slack (MET) : 2.845ns (required time - arrival time)

Source: data_in

(input port clocked by clk_a {rise@0.000ns fall@5.000ns period=10.000ns})

Destination: d1

(output port clocked by clk_a {rise@0.000ns fall@5.000ns period=10.000ns})

Path Group: clk_a

Path Type: Max at Slow Process Corner //最差大的工艺,最高温度,最低电压下的模型

Requirement: 10.000ns (clk_a rise@10.000ns - clk_a rise@0.000ns) //要求你的时序路径在规定delay要到达的要求;目前是同一个时钟域就是clka的时钟周期,不同时钟域路径就是2个clk之间的最小时钟沿的差距。

Data Path Delay: 3.120ns (logic 2.653ns (85.050%) route 0.466ns (14.950%)) //Data Path Delay主要分为logic delay + route delay,一般各占比50%左右表示最优,若建立时间违例且占比严重不均匀,则需要进行优化

Logic Levels: 2 (IBUF=1 OBUF=1)

Input Delay: 2.000ns

Output Delay: 2.000ns

Clock Uncertainty: 0.035ns ((TSJ^2 + TIJ^2)^1/2 + DJ) / 2 + PE//Uncertainty: 该值来自SDC, 通常signoff uncertainty = foundry requirest margin + PLL jitter + IR-drop modeling.

Total System Jitter (TSJ): 0.071ns

Total Input Jitter (TIJ): 0.000ns

Discrete Jitter (DJ): 0.000ns

Phase Error (PE): 0.000ns

最大Timing_path

Location Delay type Incr(ns) Path(ns) Netlist Resource(s) //通过该单元的延时是Incr;

------------------------------------------------------------------- -------------------

(clock clk_a rise edge) 0.000 0.000 r //r代表上升延迟;f代表下降延迟。

input delay 2.000 2.000 //输入延迟

0.000 2.000 r data_in (IN) //芯片输入端口到芯片内部真正数据输入端之间的线延时,是2.000ns。(可以认为是管脚的延时)

net (fo=0) 0.000 2.000 data_in

IBUF (Prop_ibuf_I_O) 0.620 2.620 r inst_0/O

net (fo=2, unplaced) 0.466 3.086 d1_OBUF

OBUF (Prop_obuf_I_O) 2.034 5.120 r d1_OBUF_inst/O

net (fo=0) 0.000 5.120 d1

r d1 (OUT)

------------------------------------------------------------------- -------------------

(clock clk_a rise edge) 10.000 10.000 r

clock pessimism 0.000 10.000

clock uncertainty -0.035 9.965

output delay -2.000 7.965

-------------------------------------------------------------------

required time 7.965 //required time 在此时间内达到时序要求的时间

arrival time -5.120 //arrival time 是实际到达的时间

-------------------------------------------------------------------

slack 2.845 //arrival time - required time

Min Delay Paths// 最小Timing_path

--------------------------------------------------------------------------------------

Slack (MET) : 0.043ns (arrival time - required time)

Source: data_in

(input port clocked by clk_a {rise@0.000ns fall@5.000ns period=10.000ns})

Destination: inst_8/D

(rising edge-triggered cell FDRE clocked by clk_a {rise@0.000ns fall@5.000ns period=10.000ns})

Path Group: clk_a

Path Type: Hold (Min at Slow Process Corner)//对于hold check来说,它会检测最短最快的组合逻辑路径和最晚的arrival time。

Requirement: 0.000ns (clk_a rise@0.000ns - clk_a rise@0.000ns)

Data Path Delay: 0.957ns (logic 0.513ns (53.678%) route 0.443ns (46.322%))

Logic Levels: 1 (IBUF=1)

Input Delay: 1.000ns

Clock Path Skew: 1.763ns (DCD - SCD - CPR)

Destination Clock Delay (DCD): 1.763ns

Source Clock Delay (SCD): 0.000ns

Clock Pessimism Removal (CPR): -0.000ns

Clock Uncertainty: 0.035ns ((TSJ^2 + TIJ^2)^1/2 + DJ) / 2 + PE

Total System Jitter (TSJ): 0.071ns

Total Input Jitter (TIJ): 0.000ns

Discrete Jitter (DJ): 0.000ns

Phase Error (PE): 0.000ns

Location Delay type Incr(ns) Path(ns) Netlist Resource(s)

(clock clk_a rise edge) 0.000 0.000 r

input delay 1.000 1.000

0.000 1.000 r data_in (IN)

net (fo=0) 0.000 1.000 data_in

IBUF (Prop_ibuf_I_O) 0.513 1.513 r inst_0/O

net (fo=2, unplaced) 0.443 1.957 d1_OBUF

FDRE r inst_8/D

(clock clk_a rise edge) 0.000 0.000 r

0.000 0.000 r clk_a (IN)

net (fo=0) 0.000 0.000 clk_a

IBUF (Prop_ibuf_I_O) 0.620 0.620 r inst_2/O

net (fo=1, unplaced) 0.466 1.086 wire_0

BUFG (Prop_bufg_I_O) 0.093 1.179 r inst_3/O

net (fo=1, unplaced) 0.584 1.763 wire_6

FDRE r inst_8/C

clock pessimism 0.000 1.763

clock uncertainty 0.035 1.799

FDRE (Hold_fdre_C_D) 0.115 1.914 inst_8

required time -1.914//同一寄存器inst_8完成从D到Q的数据传输后的-1.914s

arrival time 1.957//同一寄存器inst_8完成从D到Q的数据传输后的1.957

slack 0.043

这里required time 是负的指的是inst_8寄存器开始从D 到Q开始启动的(launch event)之前就要从clka端口开始走,因此是在启动之前,所以用负号。对于slack=实际时间arrival time-要求时间required time的数值对应数值是第21行和第8行的数值进行计算。

Pulse Width Checks//脉冲宽度检查:默认情况下,这些时钟未被选中,因为它们仅用于报告目的,不影响实现工具的结果质量。

--------------------------------------------------------------------------------------

Clock Name: clk_a

Waveform(ns): { 0.000 5.000 }

Period(ns): 10.000

Sources: { clk_a }

Check Type Corner Lib Pin Reference Pin Required(ns) Actual(ns) Slack(ns) Location Pin

Min Period n/a BUFG/I n/a 1.408 10.000 8.591 inst_3/I

Low Pulse Width Slow FDRE/C n/a 0.350 5.000 4.650 inst_8/C

High Pulse Width Slow FDRE/C n/a 0.350 5.000 4.650 inst_8/C

From Clock: clk_b To Clock: clk_b

Setup : 0 Failing Endpoints, Worst Slack 12.395ns, Total Violation 0.000ns//暂无时序违例

Hold : 0 Failing Endpoints, Worst Slack 0.066ns, Total Violation 0.000ns

PW : 0 Failing Endpoints, Worst Slack 9.650ns, Total Violation 0.000ns

(1)Max Delay Paths //最大Timing_path

--------------------------------------------------------------------------------------

Slack (MET) : 12.395ns (required time - arrival time)

Source: inst_10/C

(rising edge-triggered cell FDRE clocked by clk_b {rise@5.000ns fall@15.000ns period=20.000ns})

Destination: data_out

(output port clocked by clk_b {rise@5.000ns fall@15.000ns period=20.000ns})

Path Group: clk_b

Path Type: Max at Slow Process Corner

Requirement: 20.000ns (clk_b rise@25.000ns - clk_b rise@5.000ns)

Data Path Delay: 2.806ns (logic 2.340ns (83.378%) route 0.466ns (16.622%))

Logic Levels: 1 (OBUF=1)

Output Delay: 3.000ns

Clock Path Skew: -1.763ns (DCD - SCD + CPR)

Destination Clock Delay (DCD): 0.000ns = ( 25.000 - 25.000 )

Source Clock Delay (SCD): 1.763ns = ( 6.763 - 5.000 )

Clock Pessimism Removal (CPR): 0.000ns

Clock Uncertainty: 0.035ns ((TSJ^2 + TIJ^2)^1/2 + DJ) / 2 + PE

Total System Jitter (TSJ): 0.071ns

Total Input Jitter (TIJ): 0.000ns

Discrete Jitter (DJ): 0.000ns

Phase Error (PE): 0.000ns

Location Delay type Incr(ns) Path(ns) Netlist Resource(s)

------------------------------------------------------------------- -------------------

(clock clk_b rise edge) 5.000 5.000 r

0.000 5.000 r clk_b (IN)

net (fo=0) 0.000 5.000 clk_b

IBUF (Prop_ibuf_I_O) 0.620 5.620 r inst_4/O

net (fo=1, unplaced) 0.466 6.086 wire_1

BUFG (Prop_bufg_I_O) 0.093 6.179 r inst_5/O

net (fo=2, unplaced) 0.584 6.763 wire_7

FDRE r inst_10/C

------------------------------------------------------------------- -------------------

FDRE (Prop_fdre_C_Q) 0.223 6.986 r inst_10/Q

net (fo=2, unplaced) 0.466 7.453 q3_OBUF

OBUF (Prop_obuf_I_O) 2.117 9.569 r inst_1/O

net (fo=0) 0.000 9.569 data_out

r data_out (OUT)

------------------------------------------------------------------- -------------------

(clock clk_b rise edge) 25.000 25.000 r

clock pessimism 0.000 25.000

clock uncertainty -0.035 24.965

output delay -3.000 21.965

-------------------------------------------------------------------

required time 21.965

arrival time -9.569

-------------------------------------------------------------------

slack 12.395

(2)Min Delay Paths// 最小Timing_path

--------------------------------------------------------------------------------------

Slack (MET) : 0.066ns (arrival time - required time)

Source: inst_9/C

(rising edge-triggered cell FDRE clocked by clk_b {rise@5.000ns fall@15.000ns period=20.000ns})

Destination: inst_10/D

(rising edge-triggered cell FDRE clocked by clk_b {rise@5.000ns fall@15.000ns period=20.000ns})

Path Group: clk_b

Path Type: Hold (Min at Fast Process Corner)

Requirement: 0.000ns (clk_b rise@5.000ns - clk_b rise@5.000ns)

Data Path Delay: 0.194ns (logic 0.100ns (51.619%) route 0.094ns (48.381%))

Logic Levels: 0 Clock Path Skew: 0.145ns (DCD - SCD - CPR)

Destination Clock Delay (DCD): 0.825ns = ( 5.825 - 5.000 )

Source Clock Delay (SCD): 0.498ns = ( 5.498 - 5.000 )

Clock Pessimism Removal (CPR): 0.182ns

Location Delay type Incr(ns) Path(ns) Netlist Resource(s)

(clock clk_b rise edge) 5.000 5.000 r

0.000 5.000 r clk_b (IN)

net (fo=0) 0.000 5.000 clk_b

IBUF (Prop_ibuf_I_O) 0.126 5.126 r inst_4/O

net (fo=1, unplaced) 0.231 5.358 wire_1

BUFG (Prop_bufg_I_O) 0.026 5.384 r inst_5/O

net (fo=2, unplaced) 0.114 5.498 wire_7

FDRE r inst_9/C

FDRE (Prop_fdre_C_Q) 0.100 5.598 r inst_9/Q

net (fo=1, unplaced) 0.094 5.692 wire_4

FDRE r inst_10/D

(clock clk_b rise edge) 5.000 5.000 r

0.000 5.000 r clk_b (IN)

net (fo=0) 0.000 5.000 clk_b

IBUF (Prop_ibuf_I_O) 0.293 5.293 r inst_4/O

net (fo=1, unplaced) 0.243 5.536 wire_1

BUFG (Prop_bufg_I_O) 0.030 5.566 r inst_5/O

net (fo=2, unplaced) 0.259 5.825 wire_7

FDRE r inst_10/C

clock pessimism -0.182 5.643

FDRE (Hold_fdre_C_D) -0.017 5.626 inst_10

-------------------------------------------------------------------

required time -5.626

arrival time 5.692

-------------------------------------------------------------------

slack 0.066

Pulse Width Checks 检查时钟波形的占空比

Clock Name: clk_b

Waveform(ns): { 5.000 15.000 }

Period(ns): 20.000

Sources: { clk_b }

Check Type Corner Lib Pin Reference Pin Required(ns) Actual(ns) Slack(ns) Location Pin

Min Period n/a BUFG/I n/a 1.408 20.000 18.591 inst_5/I

Low Pulse Width Slow FDRE/C n/a 0.350 10.000 9.650 inst_10/C

High Pulse Width Slow FDRE/C n/a 0.350 10.000 9.650 inst_10/C

3.report_timing命令

report_timing 是更具体的时序报告命令,经常用来报告某一条或是某些共享特定节点的路径。用户可以在

设计的任何阶段使用 report_timing,甚至是一边设置 XDC,一边用其来验证约束的可行性与优先级。

在进行 Setup Check 时会加上一定的 clock pessimism,而 Hold Check 时则会减去一定的 clock pessimism。

report_timing示例

report_timing

INFO: [Timing 38-91] UpdateTimingParams: Speed grade: -2, Delay Type: max.

INFO: [Timing 38-191] Multithreading enabled for timing update using a maximum of 32 CPUs

INFO: [Timing 38-78] ReportTimingParams: -max_paths 1 -nworst 1 -delay_type max -sort_by slack.

Copyright 1986-2022 Xilinx, Inc. All Rights Reserved.

------------------------------------------------------------------------------------

| Tool Version : Vivado v.2022.1 (lin64) Build 3526262 Mon Apr 18 15:47:01 MDT 2022

| Date : Fri May 24 18:39:15 2024//注意看清日期避免低级错误

| Host : deep-PowerEdge-R730xd running 64-bit Ubuntu 20.04.6 LTS

| Command : report_timing

| Design : single_bit_syn

| Device : 7vx485t-ffg1157

| Speed File : -2 PRODUCTION 1.12 2014-09-11

------------------------------------------------------------------------------------

Timing Report

--------------------------------------------------------------------------------------------------------------

Slack (MET) : 2.845ns (required time - arrival time)

Source: data_in

(input port clocked by clk_a {rise@0.000ns fall@5.000ns period=10.000ns})

Destination: d1

(output port clocked by clk_a {rise@0.000ns fall@5.000ns period=10.000ns})

Path Group: clk_a//这里我们做CDC的隔离了,一个clk一个group;大多数工具默认会为每一个clock 定义一个path group,用户可以根据需求自定义path group, 如无用户自定义的path group 某条path 会被归为该path endpoint 驱动时钟对应的group.

Path Type: Max at Slow Process Corner //Max=max delay analysis 最大延迟分析;=setup

Requirement: 10.000ns (clk_a rise@10.000ns - clk_a rise@0.000ns)

Data Path Delay: 3.120ns (logic 2.653ns (85.050%) route 0.466ns (14.950%))//Data Path Delay主要分为logic delay + route delay,一般各占比50%左右表示最优,若建立时间违例且占比严重不均匀,则需要进行优化。

Logic Levels: 2 (IBUF=1 OBUF=1)//逻辑级数大或者扇出导致的;使用流水线,在过于冗长的组合逻辑增加寄存器进行打拍子。

Input Delay: 2.000ns

Output Delay: 2.000ns

Clock Uncertainty: 0.035ns ((TSJ^2 + TIJ^2)^1/2 + DJ) / 2 + PE

Total System Jitter (TSJ): 0.071ns

Total Input Jitter (TIJ): 0.000ns

Discrete Jitter (DJ): 0.000ns

Phase Error (PE): 0.000ns

Location Delay type Incr(ns) Path(ns) Netlist Resource(s)

------------------------------------------------------------------- -------------------

(clock clk_a rise edge) 0.000 0.000 r

input delay 2.000 2.000

0.000 2.000 r data_in (IN)

net (fo=0) 0.000 2.000 data_in

IBUF (Prop_ibuf_I_O) 0.620 2.620 r inst_0/O

net (fo=2, unplaced) 0.466 3.086 d1_OBUF

OBUF (Prop_obuf_I_O) 2.034 5.120 r d1_OBUF_inst/O

net (fo=0) 0.000 5.120 d1

r d1 (OUT)

------------------------------------------------------------------- -------------------

(clock clk_a rise edge) 10.000 10.000 r

clock pessimism 0.000 10.000 //在进行 Setup Check 时会加上一定的 clock pessimism,而 Hold Check 时则会减去一定的 clock pessimism。

clock uncertainty -0.035 9.965 //该值来自SDC, 通常signoff uncertainty = foundry requirest margin + PLL jitter + IR-drop modeling.

output delay -2.000 7.965

-------------------------------------------------------------------

required time 7.965

arrival time -5.120

-------------------------------------------------------------------

slack 2.845 //首先,确认所有路径的时序裕量(slack)都为正,确保没有时序违例。

4.get_timing_paths

Vivado 中还提供一个 get_timing_paths 的命令,可以根据指定的条件找到一些特定的路径。我们可以利用其返回值中的一些属性来快速定位设计中的问题。

例如逻辑级数(Logic Levels)这个影响 FPGA 性能的一大因素,因为经常隐藏在时序报告后很难被发现。在 Vivado 中,除了 借助综合后的报告来找到那些可能因为逻辑级数较高而导致的时序难满足的路径外,还有一个更直接的办法,可 以一次性报告出设计中那些高逻辑级数的路径,方便我们有针对性的深入分析和优化。

report_property -all [get_timing_paths ]示例

Property Type Read-only Value

ARRIVAL_TIME double true 6.739

CLASS string true timing_path

CLOCK_PESSIMISM double true 0.000

CORNER string true Slow

DATAPATH_DELAY double true 4.739

DATAPATH_LOGIC_DELAY double true 2.615

DATAPATH_NET_DELAY double true 2.124

DELAY_TYPE string true max

ENDPOINT_CLOCK clock true clk_a

ENDPOINT_CLOCK_DELAY double true 0.000

ENDPOINT_CLOCK_EDGE double true 10.000

ENDPOINT_CLOCK_ROOT string true

ENDPOINT_PIN port true d1

EXCEPTION string true

EXCEPTION_ID int* true

GROUP string true clk_a

INPUT_DELAY double true 2.000

INTER_SLR_COMPENSATION double true

LOGIC_LEVELS int true 2

MAX_FANOUT int true 2

NAME string true {data_in --> d1}

OUTPUT_DELAY double true 2.000

REQUIRED_TIME double true 7.965

REQUIREMENT double true 10.000

ROUTABLE_NETS int true unset***

SKEW double true

SLACK double true 1.225

STARTPOINT_CLOCK clock true clk_a

STARTPOINT_CLOCK_DELAY double true 0.000

STARTPOINT_CLOCK_EDGE double true 0.000

STARTPOINT_CLOCK_ROOT string true

STARTPOINT_PIN port true data_in

TIME_BORROWED_FROM_ENDPOINT double true

TIME_GIVEN_TO_STARTPOINT double true

UNCERTAINTY double true 0.035

USER_UNCERTAINTY double true

我们现在可以看一下不同颜色标记出来的地方就是我们可以关注去优化的点。