电子技术——MOS管的物理特性

增强型 MOSFET 是应用最广泛的场效应晶体管。除了最后一节,我们整章讨论的都是增强型 MOSFET 。我们从它的物理元件结构和物理操作入手,在下一节我们会在本节的基础上学习 MOSFET 的电流-电压特性。

元件结构

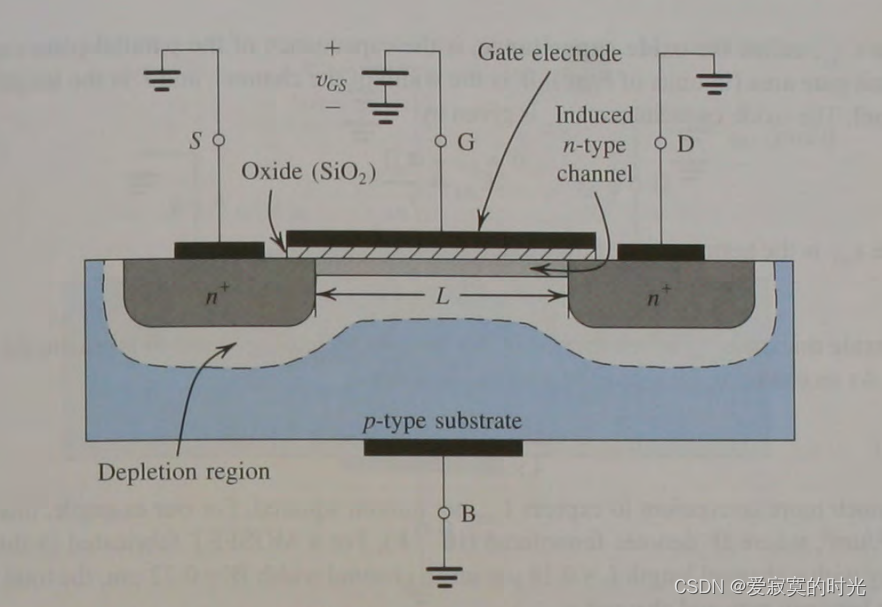

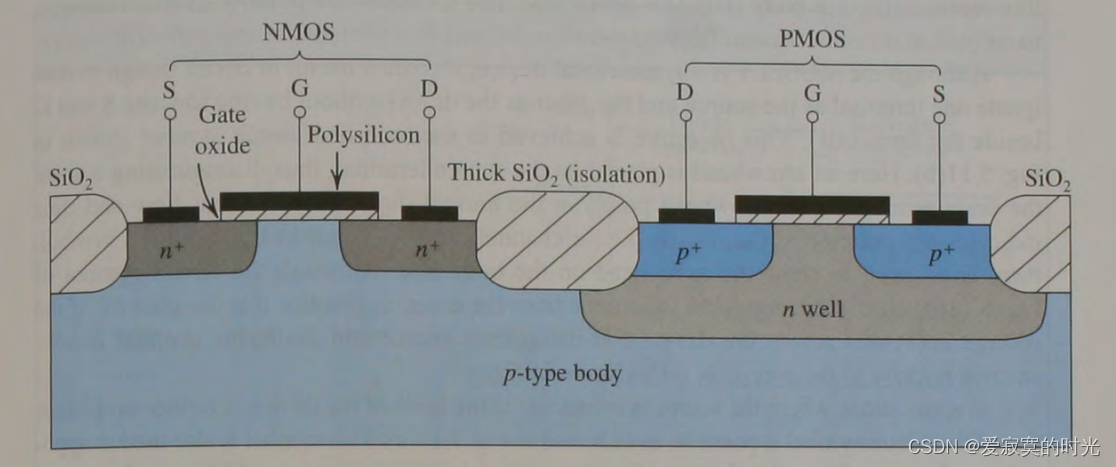

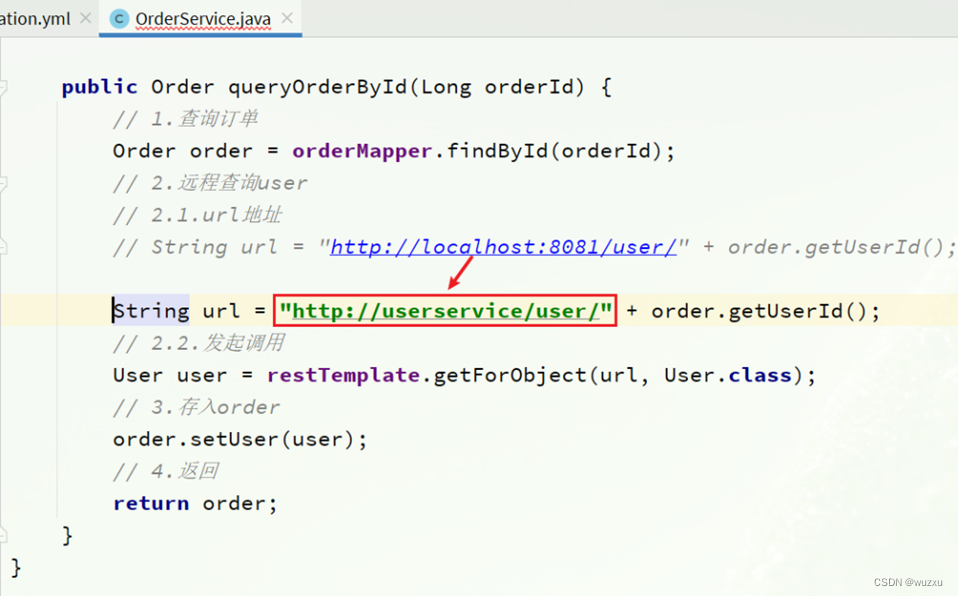

上图展示了n-沟道 增强型MOSFET的物理结构,首先第一步我们看到整个元件制作在一个以p类型的底物上,这通常是在一个单晶硅晶圆上切割下来的。第二步,在p类型底物上开出两个n类型的区域,分别为

n

+

n^+

n+ 源极 和

n

+

n^+

n+ 漏极 。第三步,将一层很薄的硅氧化物

S

i

O

2

SiO_2

SiO2 铺在源极和漏极之间的区域,硅氧化物是绝佳的绝缘体,这个厚度为

t

o

x

t_{ox}

tox 通常在1到10纳米左右。第四步,在源极、漏极、硅氧化物、底物上铺一层金属导体,在硅氧化物上铺一层金属负责形成栅极电极,简称 栅极 。在底物上的称为 体极 。字母分别简写为源极S,漏极D,栅极G,体极B。

介绍到这里这个名字的意义就显示出来(金属-氧化物-FET晶体管)。另外,还存在另一种不使用栅极的场效应管。实际上,大多数现代MOSFET都使用硅栅工艺进行制作,也就是多晶硅来形成栅极。我们今后不考虑工艺的影响。

MOSFET的另外一个名称是 隔绝栅极的场效应管 或是 IGFET 。通过观察物理结构我们发现,栅极通过硅氧化物从源极漏极隔离出来,不与源极漏极相连,实际使用上的栅极电流在 1 0 − 15 10^{-15} 10−15 安培左右。

底物分别和源极和漏极形成了两个pn结。在大多数情况下,这两个pn结总是反向偏置的。因为,我们以后会看到,漏极电压总是比源极电压高,因此在栅极无作用电压的情况下,漏极和源极被pn结所阻断不导通。在这里我们假设底物对pn结的作用无影响,进而MOSFET被看做是一个三端元件(分别是源极S,漏极D,栅极G)。马上我们将会展示,栅极电压G控制着源极S到漏极D之间的电流强度。电流从漏极纵向的通过沟道区域流向源极。注意到MOSFET的沟道区域有宽度 W W W 和长度 L L L 两个重要的参数。 一般情况下,长度大多在0.03到1微米之间,宽度在0.1到100微米之间。最后一点,MOSFET是一个对称元件,意味着源极和栅极可以交换而不影响电路的特性(实际上不总是这样,因为有结内电容和寄生二极管的影响)。

零栅极电压

假设栅极电压为零,那么源极和漏极直接可以看做是两个背对背的二极管,两个背对背的二极管阻断了源极和漏极直接的电流,因此在栅极电压为零的情况下,源极和漏极之间具有很高的阻抗,大概在 1 0 12 10^{12} 1012 欧姆的数量级。

创建电流沟道

考虑下图的情况:

在这里我们将源极和漏极接地,并且在栅极应用一个正电压

v

G

S

v_{GS}

vGS 接下来我们考虑这个正电压对MOS管造成的影响。

首先第一方面,栅极附近(沟道区域)底物中的空穴(带正电)被向下排斥离开沟道区域,在沟道区域形成耗散区。这个耗散区填充了带价电子的接受原子。这些电荷是“裸露的”因为中性空穴被推至底物的下侧。

另一方面,栅极的正电压吸引源极和漏极中的电子,进入耗散区。当大量的电子聚集在栅极极板的下方,一个临时的连接着漏极和源极的n类型区域就被创建,如下图所示:

如果现在漏极和源极直接存在电压差,那么在漏极和源极之间就会形成由移动电子形成的电流,因此这个区域被称为电子沟道,也称 n-沟道 。这种类型的MOS管称为 n-沟道的MOSFET 简称 NMOS 晶体管。NMOS的工作方式是将沟道中的p类型底物翻转成n类型,导电的n层也称为 翻转层 。

为了形成沟道,电压 v G S v_{GS} vGS 有一个最低数值,称为 阈值电压 ,记作 V t V_t Vt 。显然 V t V_t Vt 对于NMOS来说是正电压,范围在0.3V-1.0V左右。

沟道和栅极的金属极板之间形成了一个平行板电容器,硅氧化物层充当电容的电介质。栅极的金属极板带正电为正极板,而沟道带负点为负极板。因为是平行板电容器,所以在电介质存在垂直的匀强电场。电场控制着沟道中电子的数量,进而决定沟道的导电性。也就是说,源极和漏极直接的电流强度受栅极和底物之间电容电场的控制,这个现象称为 场效应 。场效应晶体管因此得名。

平行板电容器直接的电压必须大于 V t V_t Vt 才能形成沟道。当源极和漏极均接地,也就是电压均为零,此时沟道沿着水平方向的电压是均匀的均为零,也就是平行板电容器之间的电压为 v G S v_{GS} vGS 。 v G S v_{GS} vGS 超过 V t V_t Vt 的电压称为 有效电压 或是 过驱动电压 ,并且过驱动电压的值决定着沟道中的电子数量,在本课程中,我们将 v G S − V t v_{GS} - V_t vGS−Vt 记为 v O V v_{OV} vOV 。

v O V ≡ v G S − V t v_{OV} \equiv v_{GS} - V_t vOV≡vGS−Vt

那么平行板电容器中的电荷量为:

∣ Q ∣ = C o x ( W L ) v O V |Q| = C_{ox} (WL) v_{OV} ∣Q∣=Cox(WL)vOV

在这里 C o x C_{ox} Cox 称作 氧化物容值 。这个是平行板电容器的单位面积电容值(单位 F / m 2 F/m^2 F/m2)。 W W W 是沟道宽度, L L L 是沟道长度。氧化物容值由以下方程给出:

C o x = ϵ o x t o x C_{ox} = \frac{\epsilon_{ox}}{t_{ox}} Cox=toxϵox

在这里 ϵ o x \epsilon_{ox} ϵox 是硅氧化物的介电常数。

ϵ o x = 3.9 ϵ 0 = 3.45 × 1 0 − 11 F / m \epsilon_{ox} = 3.9\epsilon_0 = 3.45 \times 10^{-11} F/m ϵox=3.9ϵ0=3.45×10−11F/m

氧化物层厚度 t o x t_{ox} tox 由半导体制作工艺决定。

电荷量可以由沟道深度体现,也就是 v O V v_{OV} vOV 和电荷量和沟道深度成正比, v O V v_{OV} vOV 越大沟道越深。

应用小电压 v D S v_{DS} vDS

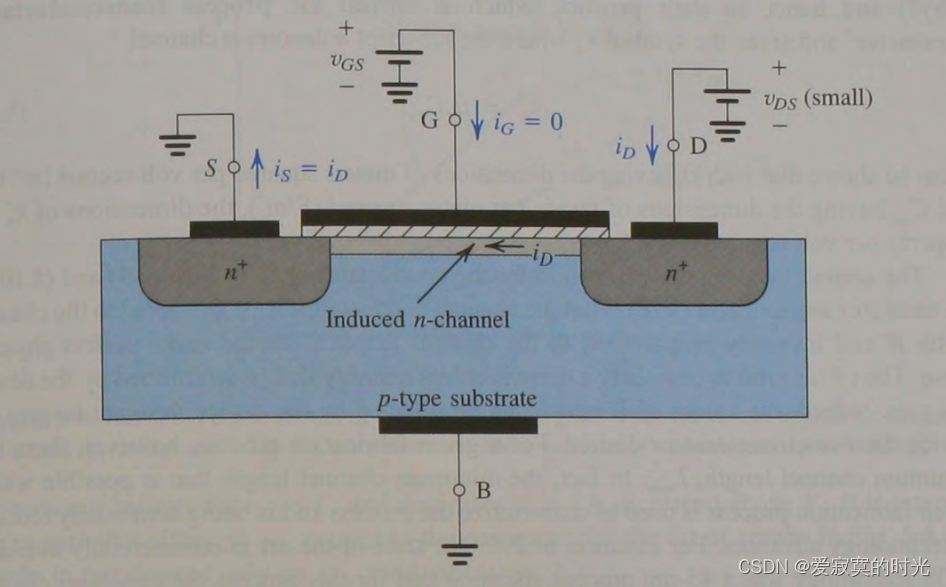

介绍完MOS的导电原理-沟道,我们在源极和漏极之间应用电压 v D S v_{DS} vDS 。如下图所示:

我们假设电压值

v

D

S

v_{DS}

vDS 足够小(50mv左右),这个电压会在沟道中产生电流,电流由漏极流向源极,电子的方向相反。

我们想计算 i D i_D iD 的值,我们假设电压值 v D S v_{DS} vDS 足够小,以至于我们依然可以看沟道沿着水平方向的电压是均匀的并且等于 v G S v_{GS} vGS。进而沟道沿着水平方向的有效电压均为 v O V v_{OV} vOV ,则单位长度的电容值是:

∣ Q ∣ L = C o x W v O V \frac{|Q|}{L} = C_{ox} W v_{OV} L∣Q∣=CoxWvOV

沟道的水平电场强度为:

∣ E ∣ = v D S L |E| = \frac{v_{DS}}{L} ∣E∣=LvDS

这个沟道的水平电场强度决定了电子的漂移速度:

v e = μ n ∣ E ∣ = μ n v D S L v_e = \mu_n |E| = \mu_n \frac{v_{DS}}{L} ve=μn∣E∣=μnLvDS

在这里 μ n \mu_n μn 是电子在n类型区域的迁移率。这个值取决于半导体制作工艺。

因此根据电流的微观表达式,漏极电流等于单位长度长的电荷量乘以电子的漂移速度:

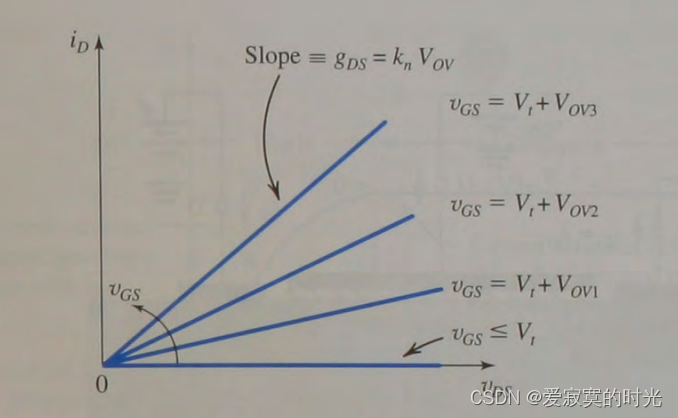

i D = [ ( μ n C o x ) ( W / L ) v O V ] v D S i_D = [(\mu_nC_{ox})(W/L)v_{OV}]v_{DS} iD=[(μnCox)(W/L)vOV]vDS

因为沟道沿着水平方向的电压是均匀的,也可以写作是:

i D = [ ( μ n C o x ) ( W / L ) ( v G S − V t ) ] v D S i_D = [(\mu_nC_{ox})(W/L)(v_{GS} - V_t)]v_{DS} iD=[(μnCox)(W/L)(vGS−Vt)]vDS

i D i_D iD 和 v D S v_{DS} vDS 之前存在电导关系,电导 g D S g_{DS} gDS 为:

g D S = ( μ n C o x ) ( W / L ) v O V = ( μ n C o x ) ( W / L ) ( v G S − V t ) g_{DS} = (\mu_nC_{ox})(W/L)v_{OV} = (\mu_nC_{ox})(W/L)(v_{GS} - V_t) gDS=(μnCox)(W/L)vOV=(μnCox)(W/L)(vGS−Vt)

第一个因子 ( μ n C o x ) (\mu_nC_{ox}) (μnCox) 由硅半导体本身和半导体的制作工艺决定,也被称为 工艺互导参数 对于NMOS记为:

k n ′ = μ n C o x k_n' = \mu_nC_{ox} kn′=μnCox

单位为 A / V 2 A/V^2 A/V2 。

第二个因子 W / L W/L W/L 称为MOS管的 宽长比 。这个参数由MOS的型号、设计者所决定。通过改变MOS管的宽长比获得不同的导电特性。因为 W / L W/L W/L 具有无量纲特性,因此MOS的尺寸可以做的无限小。尽管如此,取决于当前的半导体的制作工艺,也存在一个最小值 L m i n L_{min} Lmin ,2009年45nm制程,到目前为止(2023年)最小制程为7nm,向5nm推进。最后,氧化层厚度也会随着减小。

将前两个因子相乘,我们得到特定MOS管的导电系数:

k n = k n ′ ( W / L ) k_n = k_n' (W/L) kn=kn′(W/L)

第三个因子 v O V v_{OV} vOV 由电路设计者决定, v O V v_{OV} vOV 决定了沟道的导电性。

给定一个确定的 g D S g_{DS} gDS 我们可以将MOS管看成一个电阻,具有阻值:

r

D

S

=

1

g

D

S

r_{DS} = \frac{1}{g_{DS}}

rDS=gDS1

上图是阻性的CV特性曲线,当

v

G

S

v_{GS}

vGS 小于

V

t

V_t

Vt 的时候,表现出无穷阻抗,随着

v

G

S

v_{GS}

vGS 增大,阻值减小,沟道变深,这个现象称为 沟道增强 因此这种的NMOS全称为 增强型 n-沟道 金属-氧化物场效应晶体管 。

最后一点,因为栅极的隔绝性导致 i G = 0 i_G = 0 iG=0 ,因此 i S = i D i_S = i_D iS=iD 。

应用大电压 v D S v_{DS} vDS

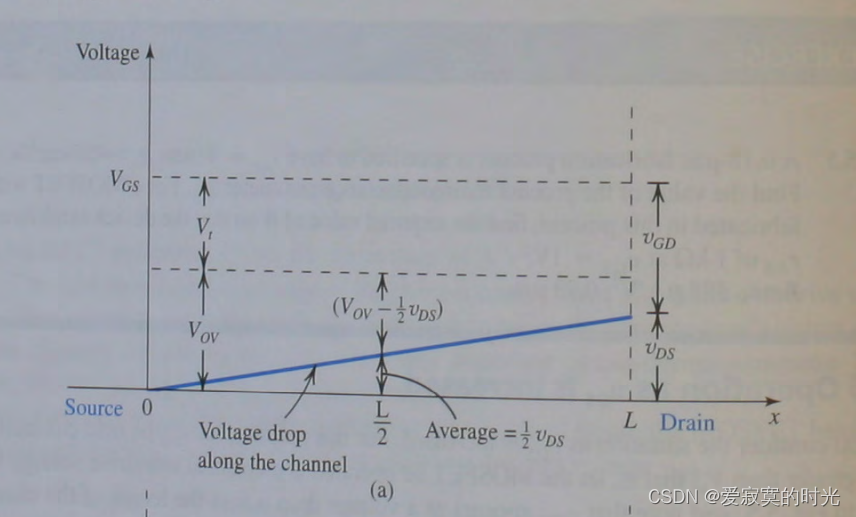

接下来我们考虑当 v D S v_{DS} vDS 继续增大的情况。我们依旧假设 v G S > V t v_{GS} > V_t vGS>Vt ,此时我们不能再看沟道沿着水平方向的电压是均匀的,而是一种沿水平方向的线性变化,如图:

此时,沟道电压从源极到漏极由零线性增长到

v

D

S

v_{DS}

vDS 。因此,平行板电容器电压从

v

G

S

v_{GS}

vGS 减小到

v

G

S

−

v

D

S

v_{GS} - v_{DS}

vGS−vDS 。下图是使用图像表示电压分布:

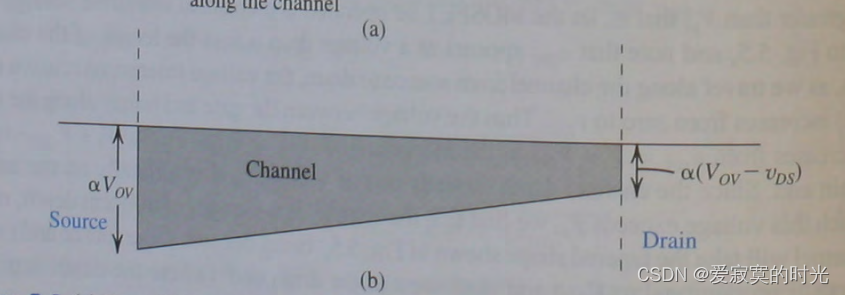

则对应的沟道深度图像为:

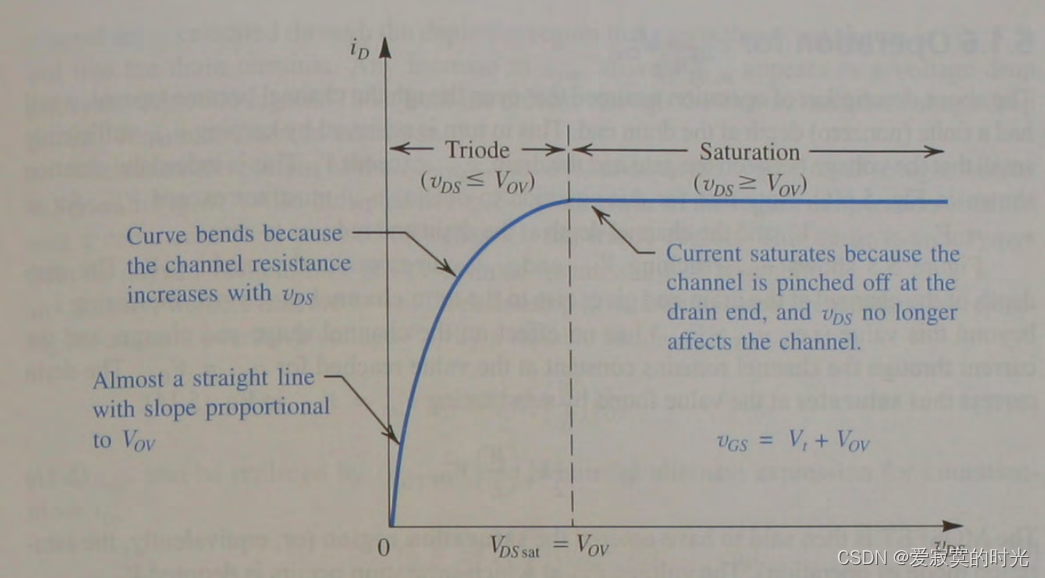

当 v D S v_{DS} vDS 增大,沟道会变得更窄,进而沟道的电阻会逐渐变大。因此,则 i D − v D S i_D-v_{DS} iD−vDS 曲线不再是一条直线,而是一条阻值逐渐变大的弯曲曲线,如图(注意我们现在只关心MOS在 v D S < V O V v_{DS} < V_{OV} vDS<VOV 的区域):

现在我们想计算

i

D

i_D

iD ,我们可以使用对极板水平路径进行积分,可得:

i D = ∫ v G S − v D S − V t v G S − V t [ ( μ n C o x ) ( W / L ) x ] v D S d x i_D = \int^{v_{GS}-V_t}_{v_{GS}-v_{DS}-V_t} [(\mu_nC_{ox})(W/L)x]v_{DS} dx iD=∫vGS−vDS−VtvGS−Vt[(μnCox)(W/L)x]vDSdx

最终得到:

i D = k n ′ ( W / L ) ( v O V − 1 2 v D S ) v D S i_D = k_n' (W/L) (v_{OV}-\frac{1}{2}v_{DS})v_{DS} iD=kn′(W/L)(vOV−21vDS)vDS

该方程就是上图中, v D S < V O V v_{DS} < V_{OV} vDS<VOV 内的曲线方程, v D S v_{DS} vDS 的下限是 0 0 0 上限是 V O V V_{OV} VOV 。当 v D S v_{DS} vDS 足够小接近原点的时候,我们可以忽略 − 1 2 v D S -\frac{1}{2}v_{DS} −21vDS 也就是应用小电压 v D S v_{DS} vDS 的时候的直线方程。

v D S > V O V v_{DS} > V_{OV} vDS>VOV 的区域

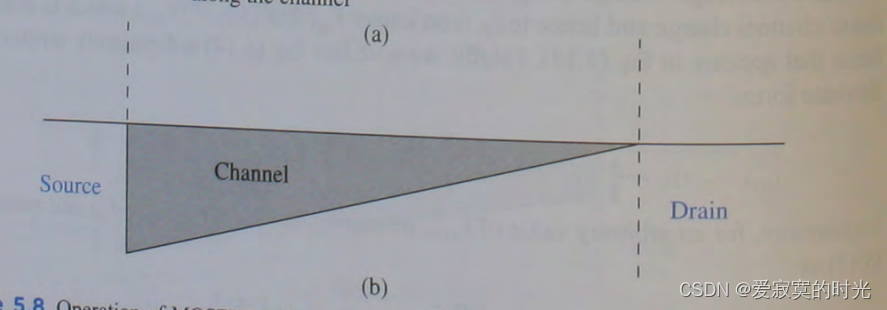

上面的讨论都是基于在漏极处的沟道有有限深度的时候,那如果当 v D S > V O V v_{DS} > V_{OV} vDS>VOV 会怎样呢?下图展示了当 v D S = V O V v_{DS} = V_{OV} vDS=VOV 极限情况下的电压分布。

以及在这个情况下的沟道深度:

此时在漏极处的沟道深度为零,MOS管进入 沟道夹断 态。增大

v

D

S

v_{DS}

vDS 对沟道的形状和电荷无影响(起点终点值不变,积分值不变),进而导致电流不会再发生变化,此时称该状态的电路为MOS管的饱和电流:

i D = 1 2 k n ′ ( W / L ) V O V 2 i_D = \frac{1}{2} k_n' (W/L) V_{OV}^2 iD=21kn′(W/L)VOV2

此时MOS管进入 饱和区 。饱和区电压 V D S s a t = V O V = V G S − V t V_{DSsat} = V_{OV} = V_{GS} - V_t VDSsat=VOV=VGS−Vt 。

值得注意的是沟道夹断并不意味着沟道电流被阻断,电子继续通过被夹断的沟道,电流继续通过被夹断的沟道。任何大于 V D S s a t V_{DSsat} VDSsat 的部分都将变成MOS管的源极漏极之间的直接压降,此时MOS管表现出恒流源的特性。

理想饱和区的区域是一条水平的直线,恒定通过电流,并保存无穷大的阻抗。相对的, v D S < V O V v_{DS} < V_{OV} vDS<VOV 的区域被称为 三极管区 。

对于给定的 v O V 2 v_{OV}^2 vOV2 的如果MOS工作在饱和区,那么通过MOS的电流将是恒定的,与 v D S v_{DS} vDS 无关,此时漏极电流为:

i D = 1 2 k n ′ ( W / L ) v O V 2 i_D = \frac{1}{2} k_n' (W/L) v_{OV}^2 iD=21kn′(W/L)vOV2

这个方程被称为MOS的饱和电流公式。

p-沟道 MOSFET

下图展示了p-沟道 MOSFET的物理结构,它的结构和NMOS很像,只不过将底物换成了n类型,把源极和漏极换成了p类型。所有的分析都和NMOS相反。PMOS和NMOS称为 互补元件 。

如果想让PMOS导通,必须使得:

v G S ≤ V t p v_{GS} \le V_{tp} vGS≤Vtp

这里 V t p V_{tp} Vtp 是PMOS的阈值电压。或者,为了不想处理负号,我们可以写作:

∣ v G S ∣ ≥ ∣ V t p ∣ |v_{GS}| \ge |V_{tp}| ∣vGS∣≥∣Vtp∣

则PMOS的导电系数为:

k p ′ = μ p C o x k_p' = \mu_p C_{ox} kp′=μpCox

之前,PMOS占据了MOS的大部分市场,随着技术的成熟,NMOS逐渐进入主导地位,主要原因是 μ p = 0.25 μ n \mu_p = 0.25\mu_n μp=0.25μn 说明电子在P类型区域的的漂移速度不如N类型区域。现在的技术,可以在同一个芯片中制作PMOS和NMOS,这种技术称为,互补MOS,简称CMOS。下图展示了如何制作CMOS的一种方法:

注意到NMOS直接在p底物上实现,而PMOS,则先制作一个n类型的井状区域,称为 n井 然后再在其上制作PMOS。相邻的两个MOS直接通过一个使用硅氧化物制作的一段隔离区域隔离开来。

亚阈值区域

之前我们说过,当 v G S < V t v_{GS} < V_t vGS<Vt 的时候,MOS管处于截止区域,没有电流通过MOS,实际上,并不总是这样。依然存在一个极小的电路流过MOS。这个区域称为亚阈值区域,漏极电流和 v G S v_{GS} vGS 呈现指数关系。

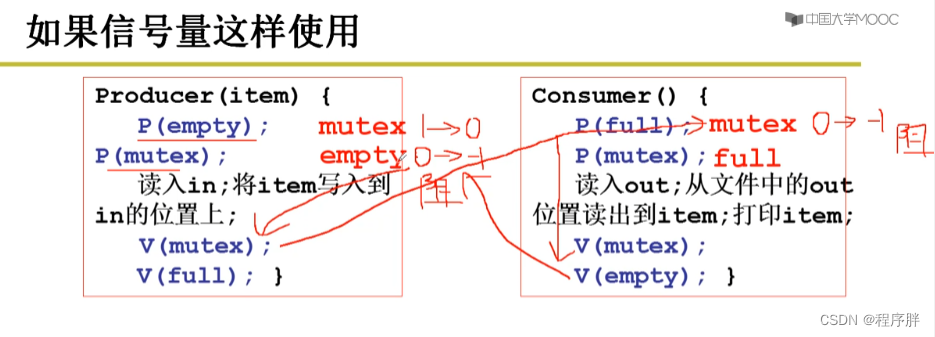

![[Linux]生产者消费者模型(基于BlockQueue的生产者消费者模型 | 基于环形队列的生产者消费者模型 | 信号量 )](https://img-blog.csdnimg.cn/c5d9adce58ec4fe89fd3578009b89f18.png)