目录

- 时钟资源(参考ug472)

- 7系列 FPGA 时钟连接差异

- 时钟资源连接关系表

- 时钟资源连接示意图

- 不同时钟区域资源连接图

- Clock-Capable Inputs

- 介绍

- 布局规则

- 全局时钟 buffer

- BUFGCTRL

- 介绍

- 原语

- 参数及端口

- INIT_OUT

- PRESELECT_I0/1

- I0/1

- CE0/1

- S0/1

- IGNORE0/1

- 真值表

- 时序

- BUFG

- BUFGCE,BUFGCE_1

- 原语

- 时序

- BUFGMUX,BUFGMUX_1

- 原语

- 时序

- BUFGMUX_CTRL

- 原语

- 时序

- Asynchronous MUX with BUFGCTRL

- BUFGMUX_CTRL with a Clock Enable

- BUFIO

- BUFR

- 原语

- 参数及端口

- BUFR_DIVIDE

- CE

- CLR

- 时序

- 驱动

- BUFMR,BUFMRCE

- 原语

- Driving Multiple BUFIOs

- Driving Multiple BUFRs

- Driving Multiple BUFRs (with Divide) and BUFIO

- Driving Multiple BUFRs (With and Without Divide)

- BUFR Alignment

- BUFH/BUFHCE

- 原语

- Stacked Silicon Interconnect Clocking

- CMT

- MMCM

- 输出时钟频率计算公式

- 结构图

- 原语

- 参数

- BANDWIDTH

- CLKOUT[1:6]_DIVIDE

- CLKOUT[0]_DIVIDE_F

- CLKOUT[0:6]_PHASE

- CLKOUT[0:6]_DUTY_CYCLE

- CLKFBOUT_MULT_F

- DIVCLK_DIVIDE

- CLKFBOUT_PHASE

- REF_JITTER1,2

- CLKIN1_PERIOD,CLKIN2_PERIOD

- CLKFBOUT_USE_FINE_PS

- CLKOUT0_USE_FINE_PS

- CLKOUT[1:6]_USE_FINE_PS

- STARTUP_WAIT

- CLKOUT4_CASCADE

- COMPENSATION

- SS_EN

- SS_MODE

- SS_MOD_PERIOD

- 端口

- CLKIN1,CLKIN2

- CLKFBIN

- CLKINSEL

- RST

- PWRDWN

- DADDR[6:0],D[15:0],DWE,DEN,DCLK,DO[15:0],DRDY

- PSCLK,PSEN,PSINCDEC,PSDONE

- CLKOUT[0:6]

- CLKOUT[0:3]B

- CLKFBOUT

- CLKFBOUTB

- CLKINSTOPPED

- CLKFBSTOPPED

- LOCKED

- PLL

- 结构图

- 原语

- 参数及端口

- 参考资料

时钟资源(参考ug472)

7系列 FPGA 时钟连接差异

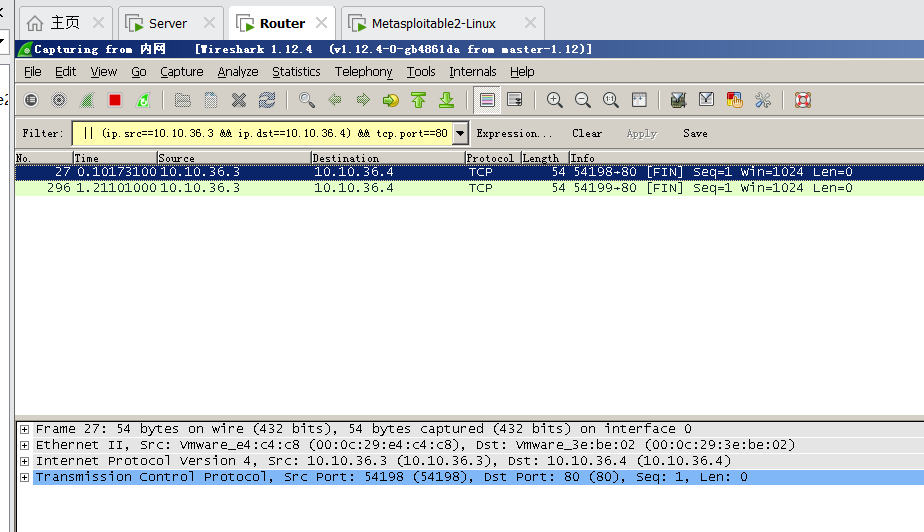

时钟资源连接关系表

时钟资源连接示意图

- BUFG 不属于任何一个时钟区域,且可以到达所有时钟区域

- 通常每个时钟区域包含多列 CLB,RAM,DSP( 50 个 CLB 每列,10 个 36K BRAM 每列,20 个 DSP 每列),12 个 BUFH,1 个 CMT(PLL/MMCM)

- BUFIO 只能驱动 I/O 时钟资源(ILOGIC/OLOGIC)

- BUFR 不仅可以驱动 I/O 资源,还能驱动逻辑资源

- BUFG 也可以驱动 BUFH(下图没有画出来)

- BUFG 和 BUFH 共享 HROW 的12 路布线资源

- 每个 GT quad 包含 10 路布线资源用于驱动 CMT 和 clock backbone 的时钟 buffer(BUFG,BUFH)

- 同一时钟区域的时钟资源(CMT,CC,GT)可以通过 BUFH 驱动水平相邻的时钟区域

不同时钟区域资源连接图

Clock-Capable Inputs

介绍

-

clock-capable(CC)inputs,主要用于从 FPGA 外部输入时钟信号,也可以当中普通 I/O 使用

-

每个 I/O bank 对应一个时钟区域,包含 50 个 I/O,其中包含 4 对 CC 引脚(2 对 SRCC + 2 对 MRCC),每对 CC 引脚又分为 master 和 slave(对应差分信号的 P 和 N 端口)

-

若使用单端时钟信号输入,则连接 P 端口,而该对 CC 引脚的 N 端口此时只能作为普通 I/O 使用

-

SRCC(single-region clock-capable I/O)可以驱动:

- 同一 bank 的 4 个 BUFIO、4 个 BUFR、2 个 BUFMR

- 同一 bank 和上下相邻两个 bank 的 CMT(1 个 CMT 包含 1 个 MMCM 和 1 个 PLL)

- 同一侧(上或下)的 16 个 BUFG

- 同一 bank 和水平相邻 bank 的 BUFH

-

MRCC(multi-region clock-capable I/O)相比 SRCC 增加了可以驱动同一 bank 的 2 个 BUFMR

-

每个 CCIO 所能连接的 BUFIO 和 BUFMR 位置是固定的

-

驱动上下相邻两个 bank 的 CMT 需要增加如下约束:

-

驱动 CMT 的专用布线资源是有限的,若要连接的 CMT 有专用布线资源,则约束:

set_property CLOCK_DEDICATED_ROUTE BACKBONE [get_nets net_name] -

若要连接的 CMT 没有专用布线资源或者该时钟信号不是从 CC 引脚输入,则约束:

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets net_name]注:Nets (get_nets) directly connected to the input of a global clock buffer (BUFG, BUFGCE, BUFGMUX, BUGCTRL)

-

布局规则

全局时钟 buffer

BUFGCTRL

介绍

- 用于异步时钟切换

- 其他所有全局时钟 buffer 都是基于 BUFGCTRL 更改的

原语

// BUFGCTRL: Global Clock Control Buffer

// Kintex-7

// Xilinx HDL Language Template, version 2020.1

BUFGCTRL #(

.INIT_OUT(0), // Initial value of BUFGCTRL output ($VALUES;)

.PRESELECT_I0("FALSE"), // BUFGCTRL output uses I0 input ($VALUES;)

.PRESELECT_I1("FALSE") // BUFGCTRL output uses I1 input ($VALUES;)

)

BUFGCTRL_inst (

.O(O), // 1-bit output: Clock output

.CE0(CE0), // 1-bit input: Clock enable input for I0

.CE1(CE1), // 1-bit input: Clock enable input for I1

.I0(I0), // 1-bit input: Primary clock

.I1(I1), // 1-bit input: Secondary clock

.IGNORE0(IGNORE0), // 1-bit input: Clock ignore input for I0

.IGNORE1(IGNORE1), // 1-bit input: Clock ignore input for I1

.S0(S0), // 1-bit input: Clock select for I0

.S1(S1) // 1-bit input: Clock select for I1

);

// End of BUFGCTRL_inst instantiation

参数及端口

INIT_OUT

- 属性值:0(default)| 1

- 指定 FPGA 加载后的 BUFGCTRL 初始输出值以及时钟切换过程中的输出值

- 设置上升沿切换条件(1)或下降沿切换条件(0)

PRESELECT_I0/1

- 设置 FPGA 加载后至设备工作之前的使用 I0 还是 I1 作为输出时钟

- TRUE 为使能,两个参数不能同时为 TRUE

I0/1

- 时钟输入

CE0/1

- 时钟使能信号,高有效,需要满足建立保持时间

- 可以将 S0/1 都置 1,只通过 CE 信号进行时钟切换,不需要等待之前时钟的下降沿或上升沿条件

S0/1

- 时钟选择信号,高有效,没有建立保持时间要求,建议使用该信号实现时钟切换功能

IGNORE0/1

- 忽略时钟切换条件,高有效(根据 INIT_OUT 参数值,需要检测到当前时钟的上升沿 1 或者下降沿 0 才能进行时钟切换)

- 该信号置位会导致 glitch 保护功能禁用,也就是可能会产生 glitch

真值表

时序

- 时刻 3 后 TBCCK_O 时间后,输出时钟由 I0 切换至 I1。时刻 3 是发生在 CE 和 S 切换后,检测到 I0 时钟的下降沿且后续检测到 I1 的上升沿时刻

- 时刻 4 将 IGNORE1 置 1,也就是 I1 切换为 I0 时不需要检测 I1 的下降沿这个前置条件

BUFG

BUFGCE,BUFGCE_1

原语

// BUFGCE: Global Clock Buffer with Clock Enable

// Kintex-7

// Xilinx HDL Language Template, version 2020.1

BUFGCE BUFGCE_inst (

.O(O), // 1-bit output: Clock output

.CE(CE), // 1-bit input: Clock enable input for I0

.I(I) // 1-bit input: Primary clock

);

// End of BUFGCE_inst instantiation

// BUFGCE_1: Global Clock Buffer with Clock Enable and Output State 1

// Kintex-7

// Xilinx HDL Language Template, version 2020.1

BUFGCE_1 BUFGCE_1_inst (

.O(O), // 1-bit output: Clock output

.CE(CE), // 1-bit input: Clock enable input for I0

.I(I) // 1-bit input: Primary clock

);

// End of BUFGCE_1_inst instantiation

时序

- BUFGCE:

- CE 只有在时钟低电平切换才有效

- CE 拉低后,默认输出低电平

- BUFGCE_1:

- CE 只有在时钟高电平切换才有效

- CE 拉低后,默认输出高电平

BUFGMUX,BUFGMUX_1

- 通过控制 CE 信号实现时钟切换功能,CE 信号时序必须满足要求

- 原语只有 UltraScale+ 才有参数,7系列没有参数

原语

// BUFGMUX: Global Clock Mux Buffer

// Kintex-7

// Xilinx HDL Language Template, version 2020.1

BUFGMUX #(

)

BUFGMUX_inst (

.O(O), // 1-bit output: Clock output

.I0(I0), // 1-bit input: Clock input (S=0)

.I1(I1), // 1-bit input: Clock input (S=1)

.S(S) // 1-bit input: Clock select

);

// End of BUFGMUX_inst instantiation

// BUFGMUX_1: Global Clock Mux Buffer with Output State 1

// Kintex-7

// Xilinx HDL Language Template, version 2020.1

BUFGMUX_1 #(

)

BUFGMUX_1_inst (

.O(O), // 1-bit output: Clock output

.I0(I0), // 1-bit input: Clock input (S=0)

.I1(I1), // 1-bit input: Clock input (S=1)

.S(S) // 1-bit input: Clock select

);

// End of BUFGMUX_1_inst instantiation

时序

BUFGMUX_CTRL

- 通过控制 S 信号实现时钟切换功能

原语

// BUFGMUX_CTRL: 2-to-1 Global Clock MUX Buffer

// Kintex-7

// Xilinx HDL Language Template, version 2020.1

BUFGMUX_CTRL BUFGMUX_CTRL_inst (

.O(O), // 1-bit output: Clock output

.I0(I0), // 1-bit input: Clock input (S=0)

.I1(I1), // 1-bit input: Clock input (S=1)

.S(S) // 1-bit input: Clock select

);

// End of BUFGMUX_CTRL_inst instantiation

时序

- S 信号可以在任何时刻变化,最多 3 个时钟周期(慢时钟)就能完成时钟切换

- 上图为 S 信号在时钟高电平时切换;S 信号在时钟高电平时切换的时序见 BUFGCTRL 时序章节

Asynchronous MUX with BUFGCTRL

BUFGMUX_CTRL with a Clock Enable

BUFIO

具体连接关系表见 “时钟资源连接关系表” 章节

BUFR

原语

// BUFR: Regional Clock Buffer for I/O and Logic Resources within a Clock Region

// Kintex-7

// Xilinx HDL Language Template, version 2020.1

BUFR #(

.BUFR_DIVIDE("BYPASS"), // Values: "BYPASS, 1, 2, 3, 4, 5, 6, 7, 8"

.SIM_DEVICE("7SERIES") // Must be set to "7SERIES"

)

BUFR_inst (

.O(O), // 1-bit output: Clock output port

.CE(CE), // 1-bit input: Active high, clock enable (Divided modes only)

.CLR(CLR), // 1-bit input: Active high, asynchronous clear (Divided modes only)

.I(I) // 1-bit input: Clock buffer input driven by an IBUF, MMCM or local interconnect

);

// End of BUFR_inst instantiation

参数及端口

BUFR_DIVIDE

- 输出时钟分频系数设置

- 属性值:BYPASS(default), 1, 2, 3, 4, 5, 6, 7, 8

- BUFR 输出延迟:BYPASS 最小,其余都一样且比 BYPASS 大

- BUFR 输入与输出相位关系:除了 BYPASS,其余都一样

CE

- 异步输出时钟使能,高有效,BYPASS 下不能使用

- 若 GSR 置位,则BUFR 处于复位状态

CLR

- 异步清除信号,高有效,BYPASS 下不能使用

- 置位后输出低电平

- 若输入时钟变化,则需要置位 CLR 进行复位

时序

- 奇分频输出时钟占空比不是 50/50

驱动

BUFMR,BUFMRCE

- 使用 MRCC 驱动 BUFMR,只能使用 MRCC 的 P 端口

原语

// BUFMR: Multi-Region Clock Buffer

// Kintex-7

// Xilinx HDL Language Template, version 2020.1

BUFMR BUFMR_inst (

.O(O), // 1-bit output: Clock output (connect to BUFIOs/BUFRs)

.I(I) // 1-bit input: Clock input (Connect to IBUF)

);

// End of BUFMR_inst instantiation

// BUFMRCE: Multi-Region Clock Buffer with Clock Enable

// Kintex-7

// Xilinx HDL Language Template, version 2020.1

BUFMRCE #(

.CE_TYPE("SYNC"), // SYNC, ASYNC

.INIT_OUT(0) // Initial output and stopped polarity, (0-1)

)

BUFMRCE_inst (

.O(O), // 1-bit output: Clock output (connect to BUFIOs/BUFRs)

.CE(CE), // 1-bit input: Active high buffer enable

.I(I) // 1-bit input: Clock input (Connect to IBUF)

);

// End of BUFMRCE_inst instantiation

注:参数 INIT_OUT 同 BUFGCTRL 参数

Driving Multiple BUFIOs

- 虽然 BUFR 也可以驱动 I/O logic,但是 BUFIO 性能更高

Driving Multiple BUFRs

Driving Multiple BUFRs (with Divide) and BUFIO

Driving Multiple BUFRs (With and Without Divide)

- 若 BUFIO 不够使用,可以使用纯 BUFR 驱动 ISERDES/OSERDES

BUFR Alignment

- 当 BUFR 非 BYPASS 模式时,必须进行多个 BUFR 间输出时钟相位对齐操作,具体操作如下:

- 拉低 BUFMRCE 的 CE 信号,禁止 BUFMRCE 的输出

- 同时置位所有 BUFR 的 CLR 信号对 BUFR 进行复位

- 重新置位 BUFMRCE 的 CE 信号,使能 BUFMRCE 的输出

- 同时拉低所有 BUFR 的 CLR 信号对 BUFR 进行复位释放

- 若要禁用所有 BUFR 的时钟输出,需先置位所有 BUFR 的 CLR 信号对 BUFR 进行复位,然后再拉低 BUFMRCE 的 CE 信号,禁止 BUFMRCE 的输出

BUFH/BUFHCE

具体连接关系表见 “时钟资源连接关系表” 章节

原语

// BUFH: HROW Clock Buffer for a Single Clocking Region

// Kintex-7

// Xilinx HDL Language Template, version 2020.1

BUFH BUFH_inst (

.O(O), // 1-bit output: Clock output

.I(I) // 1-bit input: Clock input

);

// End of BUFH_inst instantiation

// BUFHCE: HROW Clock Buffer for a Single Clocking Region with Clock Enable

// Kintex-7

// Xilinx HDL Language Template, version 2020.1

BUFHCE #(

.CE_TYPE("SYNC"), // "SYNC" (glitchless switching) or "ASYNC" (immediate switch)

.INIT_OUT(0) // Initial output value (0-1)

)

BUFHCE_inst (

.O(O), // 1-bit output: Clock output

.CE(CE), // 1-bit input: Active high enable

.I(I) // 1-bit input: Clock input

);

// End of BUFHCE_inst instantiation

Stacked Silicon Interconnect Clocking

- There are 32 global clock buffers (BUFGs) and 32 global clock lines (the clock backbone) in each super logic region (SLR).

- 关于多个 SLR 更详细开发说明见 Xilinx Large FPGA Methodology Guide (UG872)

CMT

- In 7 series FPGAs, the clock management tile (CMT) includes a mixed-mode clock manager (MMCM) and a phase-locked loop (PLL). The PLL contains a subset of the MMCM functions.

- CLKFB 不能连接 GT 时钟

MMCM

输出时钟频率计算公式

- M 对应参数 CLKFBOUT_MULT_F

- D 对应参数 DIVCLK_DIVIDE

- O 对应参数 CLKOUT_DIVIDE

结构图

原语

参数

BANDWIDTH

-

影响抖动、相位裕度等 MMCM 参数

-

属性值:HIGH | LOW | OPTIMIZED(default)

CLKOUT[1:6]_DIVIDE

- 对应输出时钟频率计算公式里的 O

- 属性值:整数 1 ~ 128,默认 1

CLKOUT[0]_DIVIDE_F

- 对应输出时钟频率计算公式里的 O,MMCM 的 CLKOUT0 支持小数分频

- 属性值:

- 整数 1 ~ 128,默认 1

- 实数 2.000 ~ 128.000,步进值 0.125

CLKOUT[0:6]_PHASE

- 输出时钟功能相位

- 属性值:-360.000 ~ 360.000,默认 0.0,具体参考步进值参考ug472-7 Series FPGAs Clocking Resources User Guide Limitations 章节

CLKOUT[0:6]_DUTY_CYCLE

- 输出时钟占空比

- 属性值:0.01 ~ 0.99,默认 0.50

CLKFBOUT_MULT_F

- 对应输出时钟频率计算公式里的 M

- 属性值:2 ~ 64 或 2.000 ~ 64.000,步进值 0.125,默认 5

DIVCLK_DIVIDE

- 对应输出时钟频率计算公式里的 D

- 属性值:1 ~ 106,默认 1

CLKFBOUT_PHASE

- 改变反馈时钟相位,进而改变所有 MMCM 的输出时钟产生负相移

- 属性值:0.00 ~ 360.00,默认0.0

REF_JITTER1,2

- 只用于仿真

- 属性值:0.000 ~ 0.999,默认0.010

CLKIN1_PERIOD,CLKIN2_PERIOD

- 属性值:0.938 ~ 100.00,默认 0.000,单位 ps

CLKFBOUT_USE_FINE_PS

CLKOUT0_USE_FINE_PS

CLKOUT[1:6]_USE_FINE_PS

STARTUP_WAIT

CLKOUT4_CASCADE

COMPENSATION

- 输入时钟补偿

SS_EN

- 扩频功能使能

SS_MODE

SS_MOD_PERIOD

端口

CLKIN1,CLKIN2

- 输入时钟,输入源见 “时钟资源连接关系表” 章节

CLKFBIN

- 反馈时钟输入

- 输入源:当前 MMCM 的 CLKFBOUT,IBUG,BUFG,BUFH

注意:为了与外部输入时钟对齐,反馈时钟连接的 buffer 类型需同外部输入时钟一样(除了 BUFR,BUFR 无法补偿)

CLKINSEL

- 输入时钟选择,1 = CLKIN1,0 = CLKIN2

注意:切换时钟后需对 MMCM 进行复位操作

RST

- 异步复位,MMCM 内部会做同步释放处理

PWRDWN

DADDR[6:0],D[15:0],DWE,DEN,DCLK,DO[15:0],DRDY

- 动态配置接口,不使用该功能时 DADDR[6:0],D[15:0],DWE,DEN,DCLK 全部置 0

PSCLK,PSEN,PSINCDEC,PSDONE

- 动态相移配置接口

CLKOUT[0:6]

- 输出时钟

CLKOUT[0:3]B

- 输出反相时钟

CLKFBOUT

- 反馈时钟

CLKFBOUTB

- 反馈时钟反相输出,该信号不能作为反馈信号输入到 MMCM

CLKINSTOPPED

- 输入时钟状态指示

- 当输入时钟消失,一个时钟内会置位该信号;当输入时钟恢复且 LOCKED 置位,该信号拉低

CLKFBSTOPPED

- 反馈时钟状态指示

- 当反馈时钟消失,一个时钟内会置位该信号;当反馈时钟恢复且 LOCKED 置位,该信号拉低

LOCKED

- 指示当前时钟频率及相位在预设误差范围内,可以使用

- FPGA 上电后会自动 LOCK,不需要进行复位操作

- 加载成功后,若 LOCKED 拉低,则必须进行 MMCM 复位操作,且在 LOCKED 置位前不能使用该时钟

PLL

结构图

原语

参数及端口

- 基本同 MMCM 作用相同,具体详见 ug472-7 Series FPGAs Clocking Resources User Guide

参考资料

- ug472-7 Series FPGAs Clocking Resources User Guide