基于FPGA的双向移位寄存器

摘 要

本文使用verilog HDL语言设计双向移位寄存器,使电路受外部信号控制,实现数字信号的双向移位等功能,其电路设计模块主要分为三个部分,分别为接受判断控制信号的组合逻辑电路部分、实现存储、运算和输出数据的时序逻辑电路部分以及时钟信号输入部分。之后对设计的电路进行仿真,判断电路设计结构的正确性。verilog语言,全称为verilog HDL(Hardware Description Language),是一种硬件描述语言。它通过文本的形式来描述数字电路系统的结构和功能,可以用于设计、模拟和验证数字电路系统。具体来说,verilog可以表示逻辑电路图、逻辑表达式,以及数字逻辑系统所完成的逻辑功能。设计者可以利用这种语言,采用自顶向下的设计方法,逐层描述自己的数字逻辑设计结构,联动一系列分层次的模块来表示复杂的数字系统。

关键词:双向移位寄存器;verilog HDL语言;数字逻辑设计

Verilog modeling and simulation of bidirectional shift register modules

Abstract

In this paper, the verilog HDL is used to design a bidirectional shift-register, which is controlled by external digital signals to realize the functions of bidirectional digital signals shifting, and the module of the circuit is mainly divided into three parts, namely the combinational circuit part that accepts the external signals, the sequential logic circuit part that storage and output data, and the part of clock-signal input .The designed circuit is simulated to judge the correctness of the design. Verilog HDL is a hardware description language. It describes the structure and function of digital circuit systems in the form of text, and can be used to design, simulate, and verify digital circuit systems. Specifically, verilog can show logic circuit diagrams, logic expressions, and the logical functions accomplished by a digital logic system. Designers can use this language to describe their digital logic design structure layer by layer using a top-down design approach, linking a series of hierarchical modules to represent complex digital systems.

Keywords: Bidirectional shift-register;verilog HDL language;digital logic design

1 绪论

使用verilog HDL语言以及相应编程软件可以实现双向移位寄存器电路的描述、设计建模和仿真验证过程。实现在两个方向上(左移和右移)移动寄存器存储的二进制数据。这种寄存器在数据处理、通信系统和密码学等多个领域具有广泛应用。双向移位寄存器的操作通常受控于时钟信号和方向控制信号。

1.1 研究背景

双向移位寄存器广泛应用于数据处理、通信系统、密码学以及临时数据存储等领域,包括电子通信、计算机网络、数字信号处理、图像处理以及密码学等。在这些领域中,双向移位寄存器发挥着关键作用,如实现数据的加密、解密、压缩和解压缩等操作。

并行与串行数据转换:在数字系统中,数据可以以并行或串行的形式存在。双向移位寄存器能够实现并行数据和串行数据之间的转换,这在数据传输和通信中非常有用。例如,串行输入并行输出移位寄存器(SIPO)可以将串行数据转换为并行数据,而并行输入串行输出移位寄存器(PISO)则可以将并行数据转换为串行数据。

灵活性:与传统的单向移位寄存器相比,双向移位寄存器提供了更高的灵活性。它可以根据需要向左或向右移动数据,这使得它在处理复杂的数据操作和多方向数据流时更具优势。

高效数据传输:双向移位寄存器可以高效地处理数据传输任务。通过控制信号的适当设置,数据可以在寄存器中快速且准确地移动,从而实现高效的数据传输和缓冲。

多维数据处理:除了基本的一维移位寄存器外,还有多维的移位寄存器。这些寄存器可以处理更复杂的数据结构,如矩阵和图像等。实现这种多维移位寄存器的方法之一是将多个具有相同位数的双向移位寄存器并联起来。

双向移位寄存器还用于功率因数自动补偿器,作为补偿电容的自动投切控制电路[2]。

随着技术的不断发展,对双向移位寄存器的研究也在不断深入。研究人员致力于提高其性能、降低功耗、优化设计等方面的工作,以满足日益增长的应用需求。

1.2 研究目的

通过深入研究双向移位寄存器的工作原理、逻辑功能以及其在不同操作模式下的行为特性,可以为数字电路的设计和实现提供更深入的理论支持。

随着数字系统的复杂性不断增加,对移位寄存器的性能要求也越来越高。研究双向移位寄存器的目的之一是寻求更高效、更稳定、更低功耗的设计方案,以满足现代数字系统的需求,并实现多功能的复用,以扩展双向移位寄存器的应用。

双向移位寄存器作为数字电路中的重要组成部分,其研究和发展对于推动整个数字电路技术的进步具有重要意义。通过对双向移位寄存器的研究,可以不断推动数字电路设计的创新和发展,为现代电子系统的实现提供更有力的支持。

综上所述,研究双向移位寄存器不仅可以加深对数字电路的理解和掌握,还可以为数字电路的设计和应用提供新的思路和方法,推动相关技术的发展和进步。

1.3 相关技术

EDA技术简而言之就是现代电子设计自动化,现代计算机、集成电路和电子系统高速发展,电子设计应运而生,这个技术的出现让人们对电子电路系统的设计能力和理解能力的了解更加深入[3]。EDA(Electronic Design Automation,电子设计自动化)技术是一种利用计算机辅助设计、分析和优化电路的方法,并可以生成电路图以及相应的物理实现布局。EDA技术涵盖多个关键环节,包括虚拟原型验证、逻辑合成、物理综合、电路模拟分析和版图设计等。EDA技术的应用广泛,包括FPGA设计、电路设计、嵌入式系统设计、通信系统设计、系统集成以及芯片设计等[4]。在FPGA设计中,EDA技术利用FPGA设备的可编程性实现复杂的数字电路功能。在电路设计中,EDA技术涵盖了数字、模拟及混合信号电路的设计,包括原理图设计、仿真、综合、优化及验证等环节。EDA技术是一种强大的工具,它极大地提高了电路设计的效率和准确性,并在多个领域有着广泛的应用。随着技术的不断进步,EDA技术将继续在电子设计领域发挥重要作用。

1.3.1 Verilog HDL

本设计采用verilog HDL语言实现电路功能,verilog HDL语言主要有以下作用:

仿真和验证:通过verilog,设计师可以进行仿真来验证电路的功能和时序。这有助于在实际硬件实现之前发现和修复设计中的错误。此外,verilog还支持各种仿真工具,这些工具可以自动执行仿真并生成详细的报告[5]。

描述和建模:Verilog能够形式化地抽象表示点的行为与结构,具有强大的硬件描述功能,已经成为目前应用最为广泛的硬件描述语言之一[6]。

综合和实现:Verilog代码可以被综合工具转换为实际的硬件实现,如FPGA或ASIC。综合是一个将高级描述转换为低级描述(如门级网表)的过程,而实现则是将网表映射到具体的硬件设备上。

模块化和重用:Verilog支持模块化的设计,这意味着设计师可以创建可重用的模块,并在多个项目中共享这些模块。这提高了设计效率,降低了开发成本。

跨平台兼容性:由于verilog是一种标准化的硬件描述语言,因此它可以在不同的EDA工具和平台上使用。这使得设计师能够灵活地选择最适合他们需求的工具和平台。

与其他语言的兼容:虽然verilog本身是一种强大的语言,但它也可以与其他硬件描述语言(如VHDL)和软件编程语言(如C、C++等)一起使用。这使得设计师能够利用多种语言的优势来完成复杂的设计任务。

1.3.2 寄存器

寄存器主要应用于存储指令和数据,作为数据传输的通道,用于在寄存器之间或与其他组件之间快速传输数据,以实现高速运算和数据交换。寄存器可以协助CPU进行各种运算,如算术运算、逻辑运算等。在运算过程中,寄存器暂存操作数和中间结果,以提高运算速度。寄存器作为计算机内部的数据存储单元,能够存储指令、操作数和中间结果等数据。尽管其容量相对较小,但其读写速度非常快,能够满足计算机对于短期存储的需求。

寄存器是执行运算和操作的数据源和目的地。例如,在进行加法运算时,数字需要从内存中加载到寄存器中进行计算,计算结果再存储回内存。这种特性使得计算机可以更加高效地进行运算。

寄存器还可以存储计算机的运算状态,例如程序计数器(PC)用来存储计算机当前执行的指令地址;标志寄存器(FLAGS)用来存储在运算过程中产生的条件结果,如溢出、零、负等。

在函数调用过程中,寄存器用来传递参数和返回值。由于寄存器的读写速度较快,可以节省数据在内存和寄存器之间的传输时间,从而提高函数调用的效率。寄存器可以用来控制程序的跳转和分支,确保程序的正常运行。

寄存器在计算机的运算、控制、数据传输等各个方面都扮演着重要的角色,是计算机能够高效、稳定运行的关键组件之一。

2 电路设计

2.1 组合逻辑电路

本文设计双向移位寄存器根据控制信号不同逻辑状态实现不同功能,如表1中,外部输入的控制信号有异步置零信号R、控制信号S1、控制信号S0以及电路检测信号C。

表1:双向移位寄存器功能表

| Rset | rst | R | 工作状态 |

| 0 | X | X | 异步置零 |

| 1 | 0 | 1 | 右移 |

| 1 | 0 | 0 | 左移 |

| 1 | 1 | X | 并行输入 |

2.1.1 异步置零信号

如表1所示,当异步置零信号有效时,无论电路处于何种状态且不受时钟信号影响,电路所有输出端全部输出低电平。

2.1.2 控制信号R

如表1所示,R有两种不同逻辑状态,分别为0、1。在并行输入信号无效的情况下,R为1状态,在下一时钟信号到来时,寄存器中存储的数据右移一位,并且在右移输入端接收一位数据,在输出端输出一位数据;R为0状态,在下一时钟信号到来时,寄存器中存储的数据左移一位,在左移输入端接收一位数据,在输出端输出一位数据;当Rset为1状态,无论控制信号为何种状态,在下一时钟信号到来时,所有寄存器接收并行输入端的相应数据。

2.2 时序逻辑电路

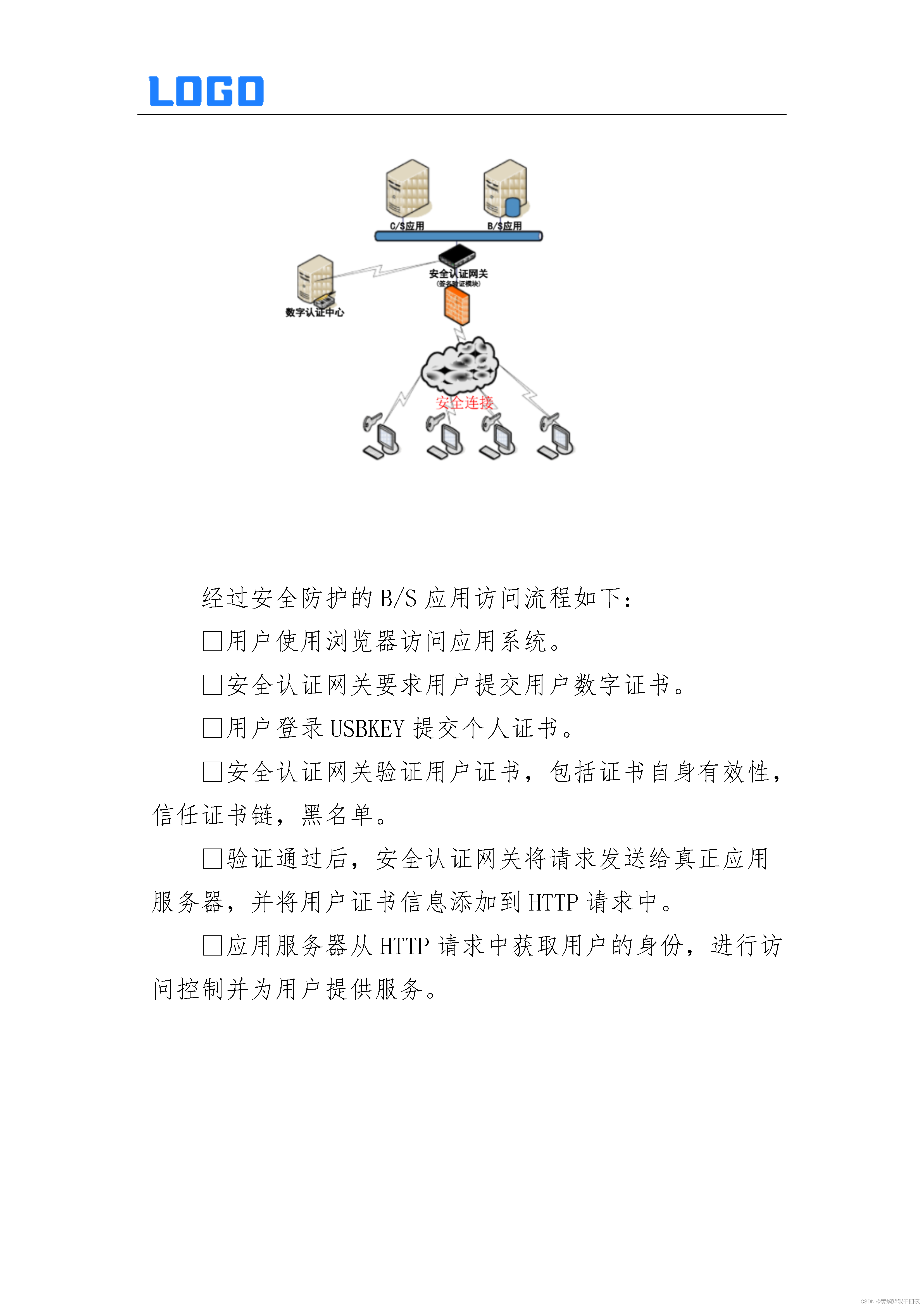

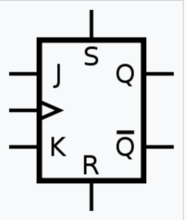

如图1所示,74194双向移位寄存器时序逻辑电路部分由JK触发器组成。由于JK触发器特性,在实际应用中产生一定问题,本文设计的双向移位寄存器改用D触发器实现。

图1:JK触发器逻辑符号

JK触发器是数字电路触发器中的一种基本电路单元,具有多种功能:

置0功能:当J、K为01状态时,JK触发器可以将输出设置为0。

置1功能:与置0功能相反,当J、K为10时,JK触发器可以将输出设置为1。

保持功能:当J、K为00状态时,触发器的输出保持不变,即具有记忆能力。

翻转功能:当J、K当J、K为11状态时,触发器的输出会发生翻转,即如果原输出为0,则翻转为1;如果原输出为1,则翻转为0。在结构上,JK触发器和基本的RS触发器有相似之处,但是它们的区别在于,RS触发器不允许R与S同时为1,而JK触发器允许J与K同时为1。此电路采用上升沿触发方式的JK触发器,即触发翻转只发生在时钟脉冲信号的正跳变边沿处。由于输入信号的传入和接收过程在时钟脉冲信号上升沿前完成,在上升沿触发翻转,上升沿后触发器被封锁,所以不存在一次翻转的特性,使得边沿触发方式的JK触发器具有良好的抗干扰性能和快速的工作速度。

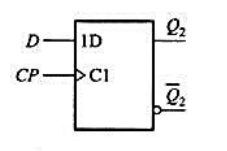

图2:D触发器逻辑符号

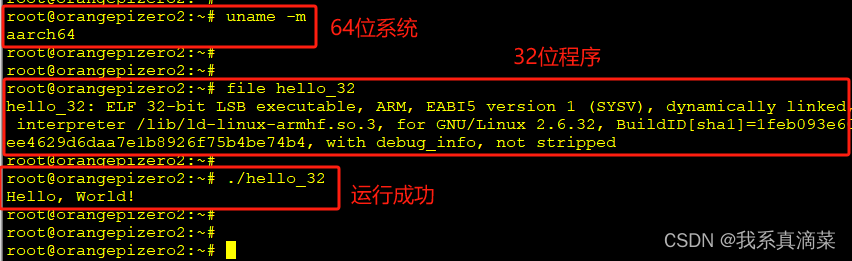

D触发器的功能相较于JK触发器较为单一,D触发器的次态取决于触发前D端的状态,即次态=D。因此,它具有置0、置1两种功能。对于边沿D触发器,由于在CP=1期间电路具有维持阻塞作用,所以在CP=1期间,D端的数据状态变化,不会影响触发器的输出状态。

2.3 时钟信号输入

时钟信号令时序逻辑电路的各个器件协同工作,形成一个整体,并且时钟信号可以为电路的不同元件提供参考时间,使得电路的不同模块根据相同的时间基础上运行,可以有效的避免时序逻辑电路的竞争和冒险[8]。时钟信号还可以控制电路中各个元件的操作顺序以及控制这些操作的时序。通过调整时钟信号的频率和占空比,进而调整电路中不同器件的工作顺序和速度,以保持电路的稳定性。

3 波形仿真及验证

3.1 仿真软件

Quartus II软件提供了仿真功能,以验证设计的电路功能是否符合设计要求。Quartus II仿真主要包括前仿真(功能仿真)、综合后的仿真、布局布线后的仿真(时序仿真)以及在线仿真。前仿真主要用于验证电路的功能正确性,通过专用工具对设计进行功能仿真,可以发现设计中的错误,加快设计进度,提高设计的可靠性。综合后的仿真主要估计门延时带来的影响,但结果并不十分准确,因此在实际应用中可能会省略此环节。布局布线后的仿真即时序仿真,用于验证设计的时序正确性。在线仿真则是在加载配置目标板之后,通过Quartus II在线逻辑分析仪进行分析,实时读取FPGA内部信号。Quartus II的仿真功能非常强大,可以帮助用户有效地验证设计的电路功能,提高设计的可靠性。

3.2 仿真结果及波形分析

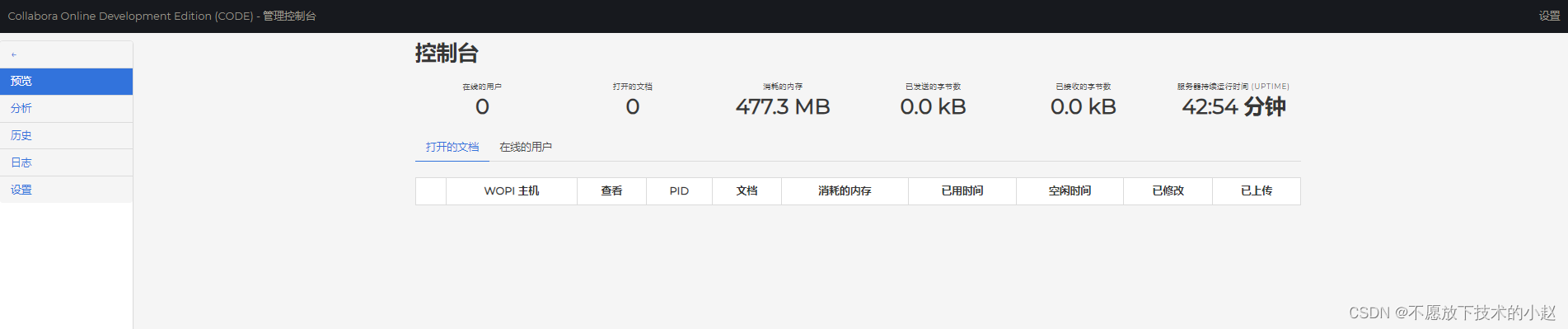

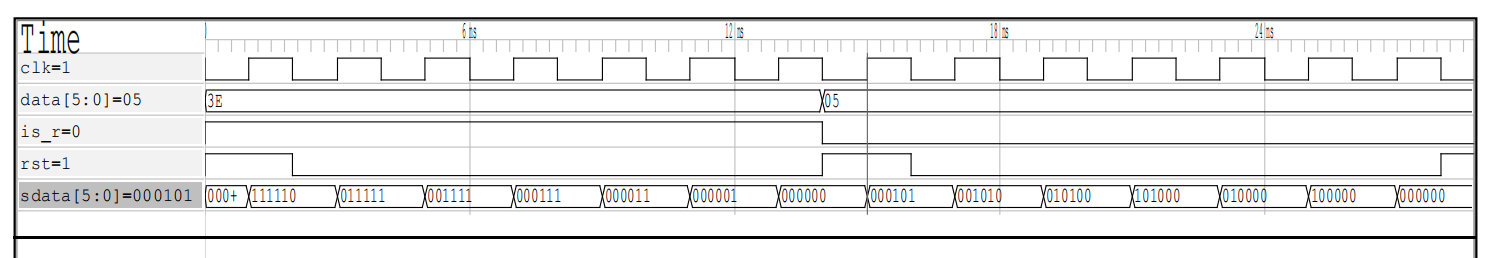

图3:双向移位寄存器的波形仿真

图3:双向移位寄存器的波形仿真

由图3结果显示,当rst=1时,进行并行输入操作;当时钟信号clk上升沿到来时,进行移位操作;当控制信号R=1时,进行右移操作,并且在左端置入0;当控制信号R=0时,进行左移操作,并且在右端置入0;如图3所示,寄存器中存储数据由111110->011111->001111->000111->000011->000001->000000,当rst=1,置入000101->001010->010100->101000->100000->000000。

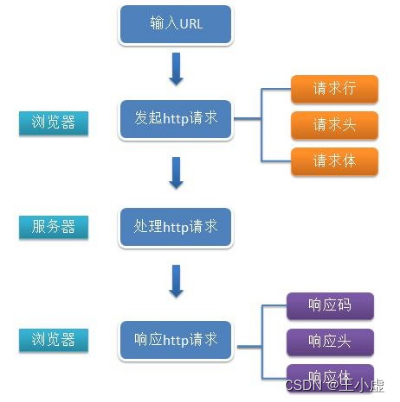

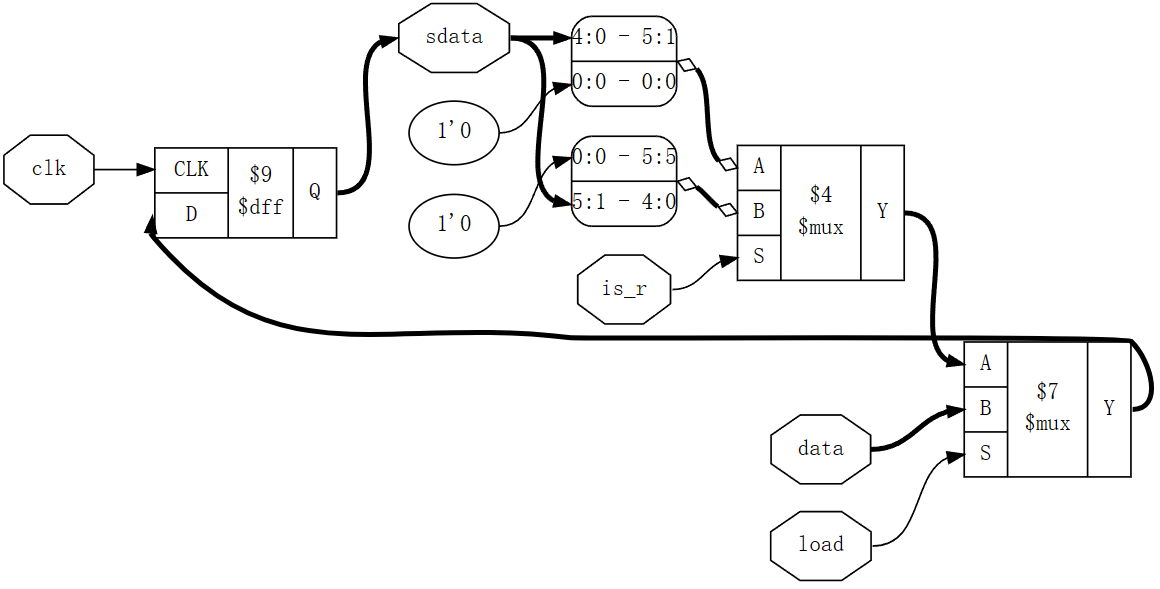

图4:双向移位寄存器的流程图

图4:双向移位寄存器的流程图

由图4所示,当时钟信号clk到来时,D触发器将储存的数据输出至双路选择器$4的两个端口,在A端口将sdata的第4至第0位上的数据依次置入A口的第5至第1位上,将数据0置入A口的第0位上;同理,在B端口将sdata的第5至第1位上的数据依次置入B口的第4至第0位上,将数据0置入B口的第5位上;此处完成数据的左移右移操作,并且由is_r的数据控制双路选择器$4的输出,当is_r=1时,进行数据的右移,双路选择器$4输出B端口上的数据;当is_r=0时,进行数据的左移,双路选择器$4输出A端口上的数据。下一阶段,双路选择器$7的A端置入双路选择器$4输出的数据,在双路选择器$7的B端上输入data,data为并行输入的数据,由外部输入决定,双路选择器$7中load数据由表1中rst决定。当load=1时,双路选择器$7将B端口上的数据输出至D触发器的输入端;当load=0时,双路选择器$7将A端口上的数据输出至D触发器的输入端。完成上述流程即完成一次移位操作。每当时钟信号上升沿到来,双向移位寄存器均完成一次上述过程,不断循环,实现数据的双向移位和并行输入功能。

4 问题分析

双向移位寄存器74194在电路结构设计存在一定缺陷,使得CP=0时,S1S0的变化为CP’提供了触发脉冲,致使其正常的逻辑功能无法实现。即CP=0期间,74194由左移、右移或并行输入状态转换为保持状态时,事实上无法保持原有状态不变7。因此,S1S0的状态变化应发生在CP=1期间,才能保证74194正常的逻辑关系得以实现[9]。则在设计双向移位寄存器时应增加约束项,使得控制信号与时钟信号互不干扰,以保证正常的电路逻辑。

对于双向移位寄存器的性能提升还可以通过优化其电路设计、增加其基本功能来实现。首先,可以通过优化逻辑,尽量减少门电路的数量从而降低其延迟时间。其次,选择较短延迟时间和更高工作频率的高速逻辑门芯片,能显著提高电路的性能。

第三,通过优化布局和布线,不仅可以降低其传输延迟时间,并且能够减小电路中噪声干扰,从而提高电路的可靠性。此外还可以通过识别和简化无用的逻辑门,消除冗余电路、

使用时序优化算法来减少传输延迟时间。在制造工艺层面,采用先进的工艺技术,如使用体积更小的晶体管或更短的导线,可以改善电路的传输性能,减少延迟时间。

双向移位寄存器功能性扩展可以使得其使用更为广泛,例如对于控制信号R可以采用两个控制信号S0、S1对其功能进行替代,保留原有左移右移功能外还可以增加保存数据、异步置零或异步置一操作。异步置零可以实现数据的清除、传输中断的功能。异步置一可以实现电路检测的功能,以快速检查寄存器是否损坏。

5 结束语

综上所述,本文使用verilog语言设计构建了双向移位寄存器的电路,阐述了其工作原理以及电路基本模块,并在基本电路的基础上增加了复位、检测功能,通过波形仿真验证了电路设计的正确性,实现了数据的并行输入、并行输出和数据的左移、右移等功能,还展示了双向移位寄存器的简化流程图,并且对现有的双向移位寄存器74194所存在的问题进行了分析,并且在本设计中尽可能得避免了这些问题,实现了设计优化。双向移位寄存器在实际中应用较为广泛,电路设计以及功耗控制还有待不断优化和提高。

- 郭永贞,许其清,袁梦等. 数字电子技术[M]. 南京:东南大学出版社,2018:372.

- 宋明礼. 双向移位寄存器的创新应用[J]. 内江师范高等专科学校学报,2000,(02):26-28.

- 苏龙,周超,王一. 基于verilog的汽车尾灯设计[J]. 电子制作,2021,(03):6.

- 曲英杰,方卓红. 超大规模集成电路设计[M]. 北京:人民邮电出版社,2015:6-19.

- ASIC and FPGA Verification[M]. Elsevier Inc,2005:3-5.

- 杨鲲,杨彬彬,曾垒. 基于verilog HDL的一种CPLD测试模块设计[J]. 中国设备工程,2022,(18):185.

- 邹虹,王汝言,贺利芳等. 数字电路与逻辑设计[M]. 北京:人民邮电出版社,2017:156-164.

- 陈景波,艾伟清,王伟等. 数字电路与FPGA设计[M]. 南京:南京大学出版社,2020:12-31.

- 林涛,林薇. 对4位双向移位寄存器74194电路仿真的思考[J]. 华北航天工业学院学报,2001,(S1):61-62.

- Joseph C. Computer Arithmetic and verilog HDL Fundamentals[M]. CRC Press,2017:7-9.