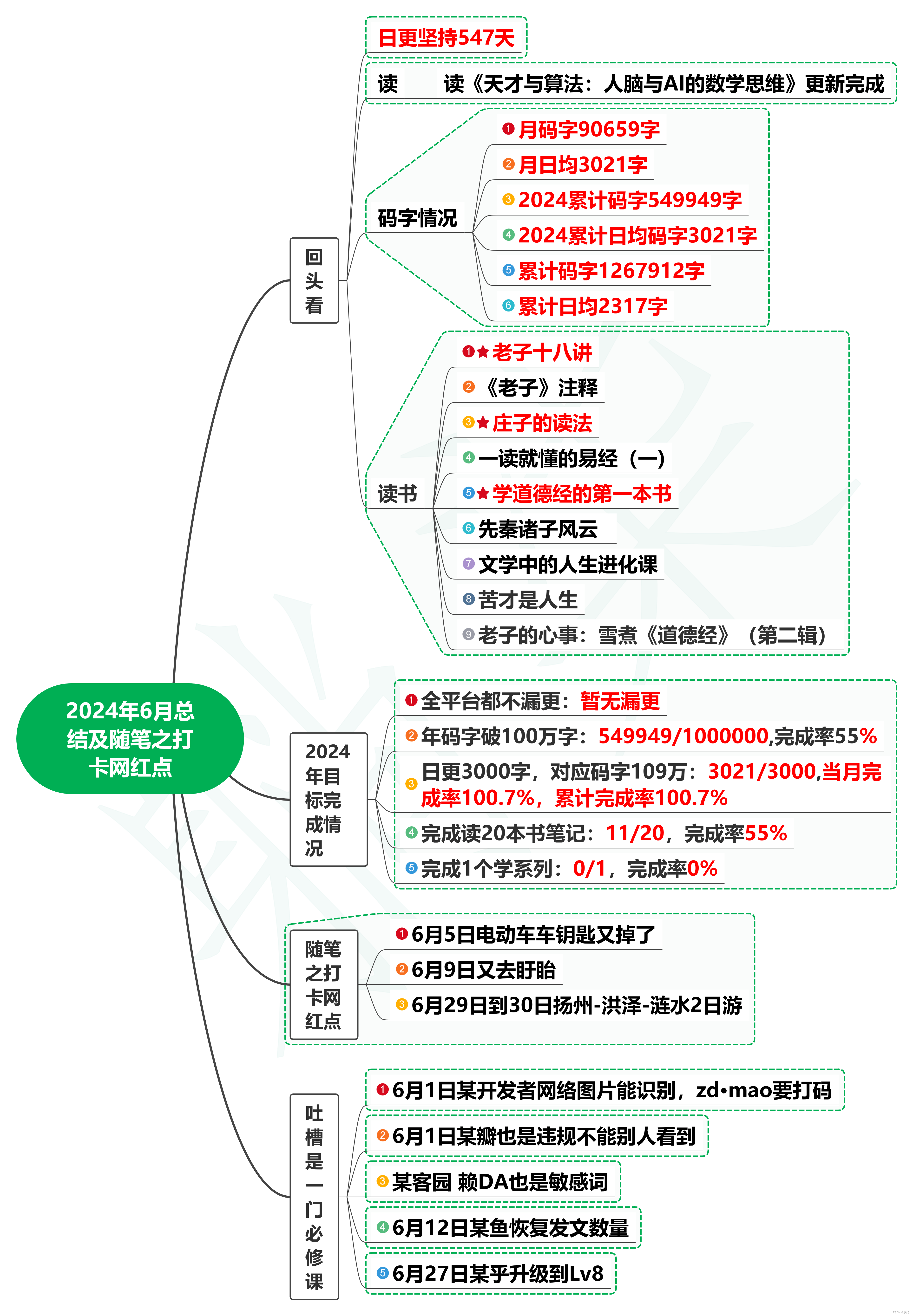

HPCA 2024 Paper CXL论文阅读笔记整理

问题

GPU已成为许多数据密集型应用程序不可或缺的加速器,如科学工作负载、深度学习模型和图分析,这些应用程序对越来越大的内存有着共同的需求。通常,采用统一存储器[12]、[18]、[34]、[67]和多GPU[7]、[48]、[50]来克服GPU的容量墙。

-

统一存储器:主机存储器与GPU设备存储器结合使用。但除了频繁的主机交互以协调内存管理外,从外部内存传输数据是不可避免的,从而导致显著的性能开销[34]。

-

多GPU:将工作集分布在不同的GPU设备存储器上,GPU之间的通信成为瓶颈[48]。

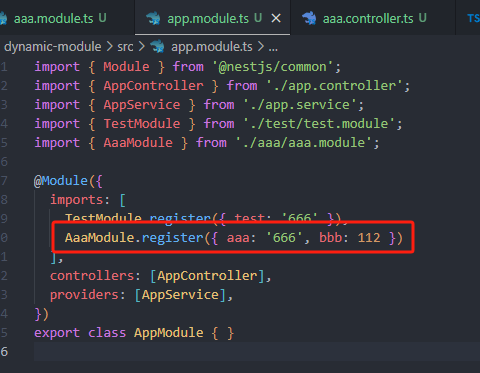

随着传统内存接口连接的内存容量达到极限,异构内存系统在扩展内存池方面获得了吸引力。一些工作[19]、[27]、[28]、[40]、[43]探索了使用计算快速链路(CXL)[1]进行系统内存扩展,还研究了高效使用扩展内存系统的页面放置和分页策略。CXL扩展内存允许使用抽象和通用的加载/存储语法访问不同的内存(例如,DDR或NAND[29]),通过将数据存储在CXL扩展内存中,GPU可以管理无法容纳在其本地GDDR/HBM内存中的数据,同时避免中断或长链接远程访问。

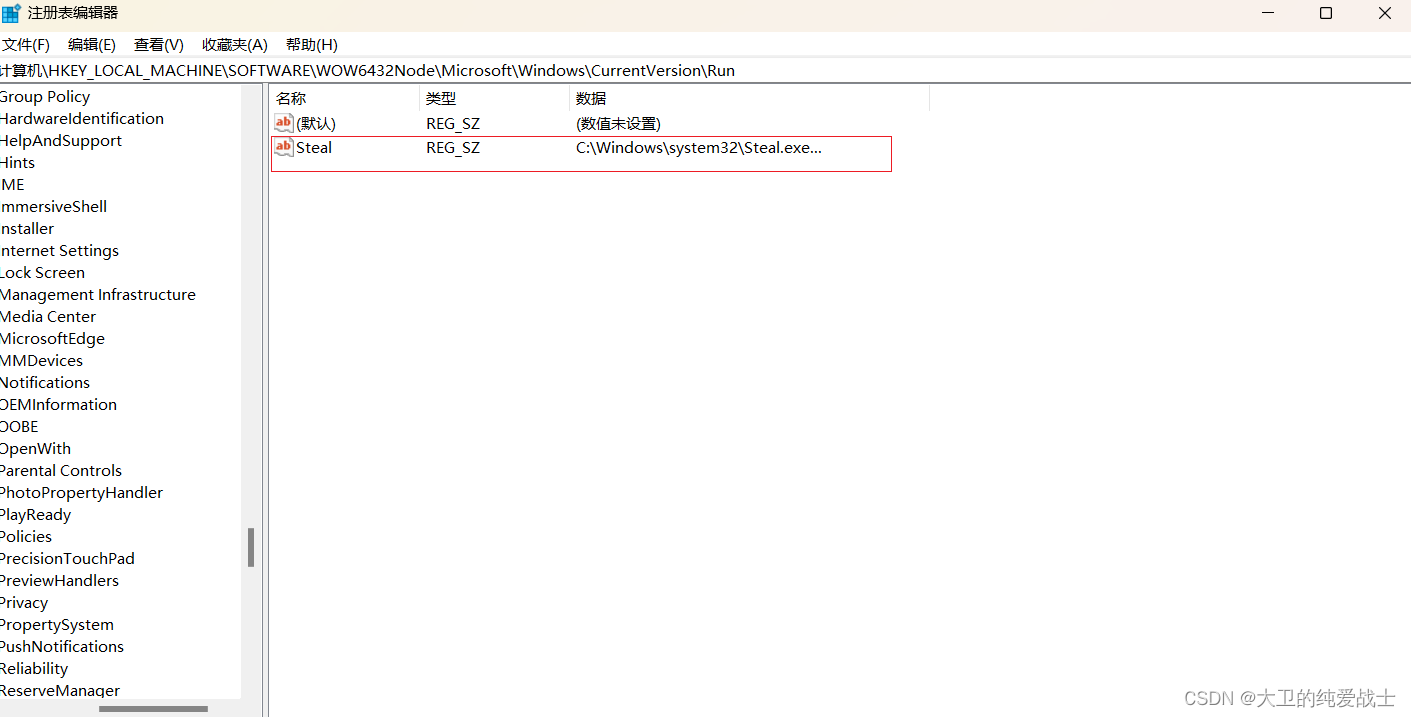

但将关键应用程序卸载到异构内存系统会面临更高的安全漏洞,即针对其数据或计算的攻击。在这样的环境中提供机密计算是必不可少的,机密计算通过引入可信执行环境(TEE)来提供安全保障。TEE将应用程序数据和计算与其他共享应用程序或外部实体隔离,在物理世界中,TEE定义了一个表示信任区域的可信计算库(TCB),通常是GPU芯片。TCB之外的任何组件,包括片外存储器,都被认为是不可信的,使用这些组件需要安全保证。

CXL扩展内存和GPU设备内存之间的不对称带宽对性能和安全提出了新的挑战。传统异构存储器系统需要缓存或页面迁移方案,将频繁访问/待访问的数据移动到更高带宽的存储器来确保高性能。但现有安全方案会带来显著的性能开销,因为从慢速存储器(即CXL扩展存储器)到快速存储器(即GDDR/HBM)的每一次数据移动都会触发与安全相关的操作(例如,加密和身份验证)。例如,在慢速存储器(即CXL扩展存储器)和快速存储器(即GDDR/HBM)之间交换数据需要两个存储器在每个存储器发送/接收数据时执行安全操作;此外,这两个存储器不仅被请求用于数据,而且还被请求用于安全元数据。因此,在异构适应CXL内存扩展的安全GPU中实现高性能的主要挑战是设计高效的安全元数据管理,通过考虑安全需求和动态数据移动来减少与安全相关的流量。而且现有的安全实施的元数据与数据的物理位置有关。

本文方法

本文提出了一种新的安全模型,适用于具有异构存储器的GPU。

-

统一存储器的安全元数据,将安全元数据与数据的物理位置解耦,从而消除了在数据重新定位过程中的重新加密。

-

重组加密计数器块,在具有相同交织粒度的次要计数器之间有效地共享主要计数器,从而在数据重新定位时进一步减少流量。同时压缩了内存中访问频率较低的的计数器块,确保了高效的存储和流量。

-

在CXL到GPU映射中以位掩码格式跟踪脏信息,显著减少元数据访问和写回相关的流量。

根据实验评估,与传统安全模型相比,本文提出的安全模型将GPU吞吐量的几何平均值提高了29.94%(高达190.43%),并将内存子系统中的安全流量平均降低到47.79%(低至17.71%的开销)。

实验

实验环境:GPGPU-sim

总结

针对使用CXL内存扩展GPU内存时,为了实现安全产生的相关流量。本文提出了一种新的安全模型,包括三个技术:(1)统一存储器的安全元数据,将安全元数据与数据的物理位置解耦,消除了在数据重新定位过程中的重新加密。(2)重组加密计数器块,在次要计数器之间共享主要计数器,从而减少流量,同时压缩访问频率较低的的计数器块。(3)在CXL到GPU映射中以位掩码格式跟踪脏信息,显著减少元数据访问和写回相关的流量。