HDL习题

1 阻塞型赋值‘=’与非阻塞型赋值‘<=’

阻塞型赋值

b

=

a

b=a

b=a:适用于纯组合电路

非阻塞型赋值

b

<

=

a

b<=a

b<=a:适用与时序逻辑电路

2 wire线型,assign连续赋值

wire a,b,c;

assign b = a;

assign c = a;

与编程语言不同, a s s i g n assign assign “连续赋值” 描述的是 事物之间的联系,而不是将值从a复制到b的操作。那么多个赋值语句之间不存在像C语言中的先后关系。

- AngGate

assign out = a & b;

- norGate 或非门

assign out = ~(a | b);

- xorGate 异或门 ⊕ \oplus ⊕

assign out = a ^ b;//^按位异或

- xnorGate 同或门 ⊙ \odot ⊙

assign out = ~(a ^ b);

3 vector向量[end:start]

3-1 Vectorgates

module top_module(

input wire[2:0] a,

input wire[2:0] b,

output wire[2:0] out_or_bitwise,

output wire out_or_logical,

output wire[5:0] out_not

);

assign out_or_bitwise = a | b; // 按位相或

assign out_or_logical = a || b; // 各位一次相或

assign out_not[2:0] = ~a; // 按位取反

assign out_not[5:3] = ~b;

endmodule

3-2 向量合并

例如: { 1 ′ b 1 , 1 ′ b 0 , 3 ′ b 101 } = > 5 ′ b 10101 \{1'b1, 1'b0, 3'b101\} => 5'b10101 {1′b1,1′b0,3′b101}=>5′b10101

module top_module (

input [4:0] a, b, c, d, e, f,

output [7:0] w, x, y, z );

assign {w, x, y, z} = {a, b, c, d, e, f, 2'b11};

endmodule

3-3 反转

module top_module(

input [7:0] in,

output [7:0] out

);

// 方式一

generate

genvar i;

for(i = 0;i < 8;i++)begin:conv//generate块的名为conv

assign out[i] = in[7-i];

end

endgenerate

// 方式二

always@(*)begin

for(int i = 0;i < 8;i++)begin

out[i] = in[7-i];

end

end

endmodule

3-4 复制

assign out = {{24{in[7]}}, in};

4 模块

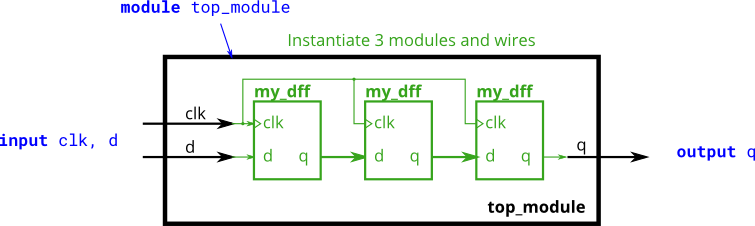

4-1 模块移位

module top_module ( input clk, input d, output q );

wire q1,q2;

my_dff dff1(

.clk(clk),

.d(d),

.q(q1)

);

my_dff dff2(

.clk(clk),

.d(q1),

.q(q2)

);

my_dff dff3(

.clk(clk),

.d(q2),

.q(q)

);

endmodule

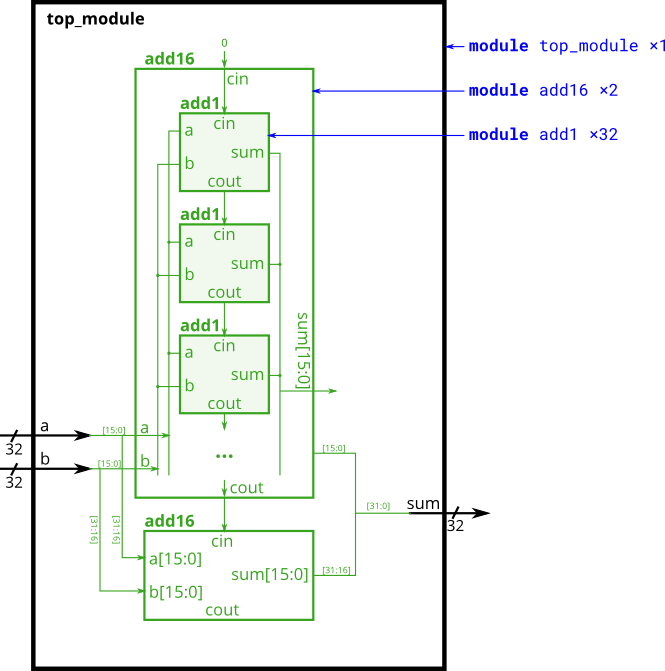

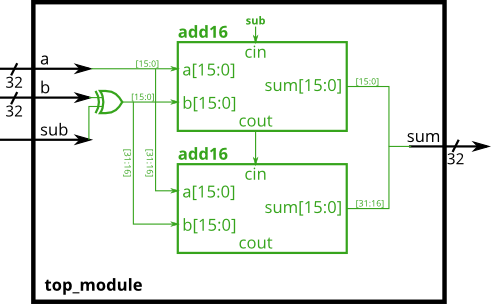

4-2 32位加法器

// 32位加法器由2个16位加法器组成,一个16位加法器由16个半加器组成

module top_module (

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire cout1;

add16 add16_1(

.a(a[15:0]),

.b(b[15:0]),

.cin(1'b0),

.sum(sum[15:0]),

.cout(cout1)

);

add16 add16_2(

.a(a[31:16]),

.b(b[31:16]),

.cin(cout1),

.sum(sum[31:16]),

.cout()

);

endmodule

module add1 (

input a, b, cin,

output sum, cout );

assign {cout,sum} = a + b + cin;

endmodule

其中 assign {cout,sum} = a + b + cin; 例如四位加法器有:

a

d

e

c

=

11

,

b

d

e

c

=

13

,

a

+

b

d

e

c

=

24

a_{dec}=11,b_{dec}=13,a+b_{dec}=24

adec=11,bdec=13,a+bdec=24(

a

b

i

n

=

1011

,

b

b

i

n

=

1101

a_{bin}=1011,b_{bin}=1101

abin=1011,bbin=1101,

(

a

+

b

)

b

i

n

=

(a+b)_{bin}=

(a+b)bin=

0001

0001

0001

1000

1000

1000)

c

i

n

n

−

1

=

c

o

u

t

n

cin_{n-1}=cout_{n}

cinn−1=coutn

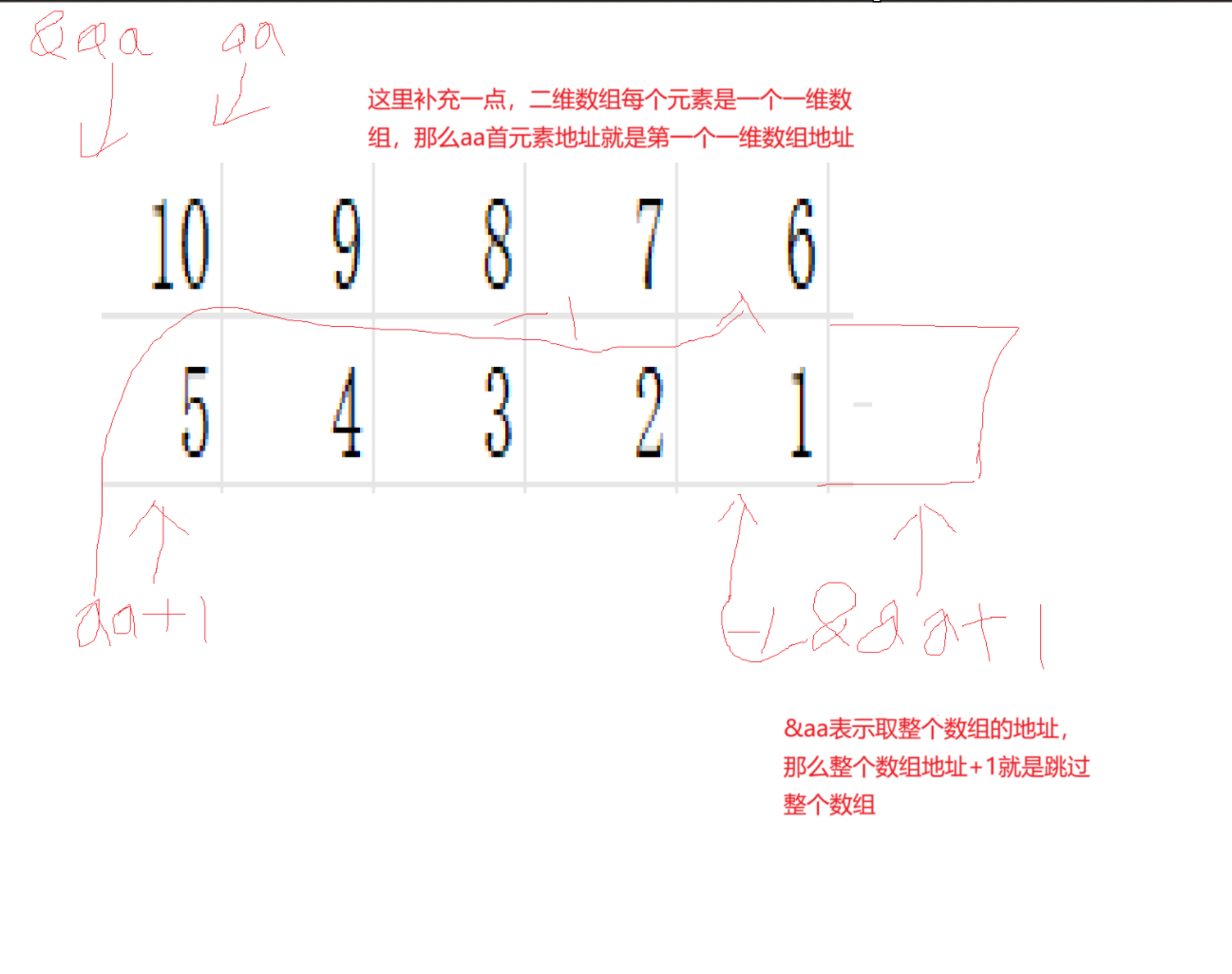

| 位号 | cin | a | b | cout | sum |

|---|---|---|---|---|---|

| 0 | 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 |

| 2 | 1 | 0 | 1 | 1 | 0 |

| 3 | 1 | 1 | 1 | 1 | 1 |

4-3 减法器

module top_module(

input [31:0] a,

input [31:0] b,

input sub,

output [31:0] sum

);

wire cout1;

wire [31:0] b_in;

assign b_in = b ^ {32{sub}}; // 异或

add16 add16_1(

.a(a[15:0]),

.b(b_in[15:0]),

.cin(sub),

.sum(sum[15:0]),

.cout(cout1)

);

add16 add16_2(

.a(a[31:16]),

.b(b_in[31:16]),

.cin(cout1),

.sum(sum[31:16]),

.cout()

);

endmodule