目录

- bug1

- bug2

- bug3

- bug4

微信公众号获取更多FPGA相关源码:

OFDM 802.11a的FPGA实现:发射部分完整工程

经过各位朋友的提醒,这部分内容有些许bug,目前已经更正,后续还会持续更新。获取更新内容,可以进上述链接,进文末的链接二进行下载,或者根据文末的指引,在后台回复,也可获取最新工程的下载链接。

感谢各位朋友的支持,以及给我提出项目中的错误。对于项目中出现了错误,我深表歉意,下面我将逐一说明并更正目前发现的一些错误。

bug1

IFFT后进行加窗处理时,逻辑和计算方式有误,文件路径为:OFDM_802.11a_my\TX\src\IFFT\ifft.v,现将那部分代码更正如下:

//下一个符号第一个数据(CP的第一个样值)将和OFDM符号64个样值中的第一个数据相加且右移1位后再行输出。

assign ifft_dout = ifft_dout_Index == 'd48 & ifft_dout_vld_edge_pluse ?

{$signed(first_iff_dout[15:8]) + $signed(m_axis_data_tdata[23:16])>>>1,

$signed(first_iff_dout[7:0]) + $signed(m_axis_data_tdata[7:0])>>>1} :

{m_axis_data_tdata[23:16],m_axis_data_tdata[7:0]};

//----------------------------------------------------------------------------------//

bug2

路径为OFDM_802.11a_my\TX\src\MCU\tx_mcu.v的代码文件中,有如下一段代码,没有使用到,编译时会报错。这里是在调试时加入的,但是后期上传时未删除,这部分注释掉即可。并且路径为OFDM_802.11a_my\TX\testbench\test_tb.v的仿真测试文件中关于mcu_dout_train_rdy的端口也应删去或者注释掉。

//控制训练序列输出

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

mcu_dout_train_rdy <= 1'b0;

else if(~phy_rst_n)

mcu_dout_train_rdy <= 1'b0;

else

mcu_dout_train_rdy <= 1'b1;

end

bug3

扰码模块,路径为OFDM_802.11a_my\TX\src\Data_Modem\scramler.v的文件,对于shift_reg信号在复位时,应该改赋值为7’b1011101,而不是0,不然在使用路径为OFDM_802.11a_my\TX\testbench\test_tb.v的仿真测试文件进行测试时会导致结果不正确,修改后如下:

always@(posedge clk or negedge rst_n ) begin

if(!rst_n) begin

shift_reg <= 7'b1011101;

scram_dout <= 0;

scram_dout_vld <= 0;

scram_dout_sig_flag <= 0;

scram_dout_rate_con <= 4'b1011;

end

else if( scram_load ) begin

shift_reg <= scram_seed;

scram_dout_vld <= 0;

end

else if( scram_en) begin

if(~scram_din_sig_flag)begin

scram_dout <= shift_reg[6] + shift_reg[3] + scram_din; //s(x) = x^7 + x^4 + 1

scram_dout_vld <= 1;

shift_reg <= {shift_reg[5:0],(shift_reg[6]+shift_reg[3])};

end

else begin

scram_dout <= scram_din;

scram_dout_vld <= 1;

end

scram_dout_sig_flag <= scram_din_sig_flag;

scram_dout_rate_con <= scram_din_rate_con;

end

else if(scram_dout_vld & scram_din_rdy)begin //下游接受完毕,没有新数据进来,vld拉低

scram_dout_vld <= 0;

end

end

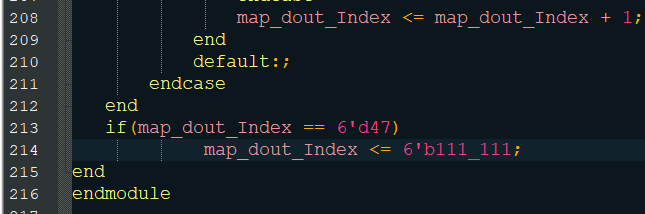

bug4

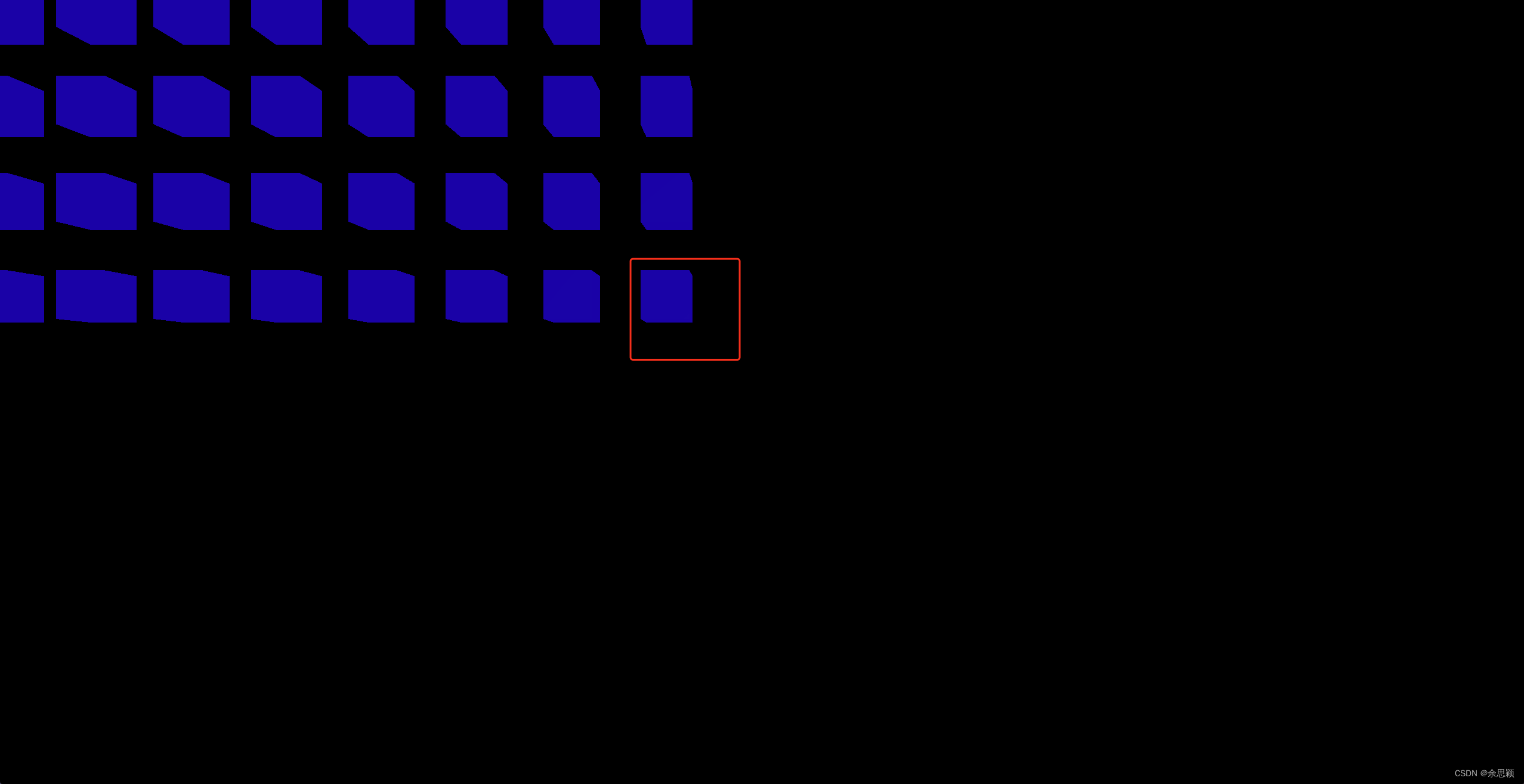

路径为OFDM_802.11a_my\TX\src\Data_Modem\maping.v的文件中,下图所示代码逻辑错误,会导致后期综合出现问题,但是仿真没问题,当时没注意这部分代码这样描述是不可综合的。

需要将其修改如下:

always@(posedge clk or negedge rst_n ) begin

if(!rst_n) begin

map_dout_Re <= 0;

map_dout_Im <= 0;

map_dout_Index <= 6'b111_111;

end

else if(map_dout_Index == 6'd47)

map_dout_Index <= 6'b111_111;

else if( full & ~rd_en) begin

case(map_din_Map_Type)

2'b00: begin //Bpsk

case(map_din_r[0])

1'b0: map_dout_Re <= 8'b1100_0000; // -1

1'b1: map_dout_Re <= 8'b0100_0000; //1

default:map_dout_Re <= 0;

endcase

map_dout_Im <= 8'b00000000;

map_dout_Index <= map_dout_Index + 1;

end

2'b01: begin //Qpsk

case(map_din_r[0])

1'b0: map_dout_Re <= 8'b1101_0011; //-1 * 1/√2

1'b1: map_dout_Re <= 8'b0010_1101; //1 * 1/√2

default:map_dout_Re <= 0;

endcase

case(map_din_r[1])

1'b0: map_dout_Im <= 8'b1101_0011;

1'b1: map_dout_Im <= 8'b0010_1101;

default: map_dout_Im <= 0;

endcase

map_dout_Index <= map_dout_Index + 1;

end

2'b10: begin //16-qam

case(map_din_r[1:0])

2'b00: map_dout_Re <= 8'b1100_0011; //-3 * 1/√10

2'b10: map_dout_Re <= 8'b1110_1100;//-1* 1/√10

2'b11: map_dout_Re <= 8'b0001_0100;//1* 1/√10

2'b01: map_dout_Re <= 8'b0011_1101;//3* 1/√10

default:map_dout_Re <= 0;

endcase

case(map_din_r[3:2])

2'b00: map_dout_Im <= 8'b1100_0011;

2'b10: map_dout_Im <= 8'b1110_1100;

2'b11: map_dout_Im <= 8'b0001_0100;

2'b01: map_dout_Im <= 8'b0011_1101;

default: map_dout_Im <= 0;

endcase

map_dout_Index <= map_dout_Index + 1;

end

2'b11: begin //64-qam

case(map_din_r[2:0])

3'b000: map_dout_Re <= 8'b1011_1011; //-7 * 1/√42

3'b001: map_dout_Re <= 8'b1100_1111; //-5*1/√42

3'b011: map_dout_Re <= 8'b1110_0011; //-3*1/√42

3'b010: map_dout_Re <= 8'b1111_0111; //-1*1/√42

3'b110: map_dout_Re <= 8'b0100_0101; //7*1/√42

3'b111: map_dout_Re <= 8'b0011_0001;//5*1/√42

3'b101: map_dout_Re <= 8'b0001_1101;//3*1/√42

3'b100: map_dout_Re <= 8'b0000_1001;//1*1/√42

default:map_dout_Re <= 0;

endcase

case(map_din_r[5:3])

3'b000: map_dout_Im <= 8'b1011_1011; //-7 * 1/√42

3'b001: map_dout_Im <= 8'b1100_1111; //-5*1/√42

3'b011: map_dout_Im <= 8'b1110_0011; //-3*1/√42

3'b010: map_dout_Im <= 8'b1111_0111; //-1*1/√42

3'b110: map_dout_Im <= 8'b0100_0101; //7*1/√42

3'b111: map_dout_Im <= 8'b0011_0001;//5*1/√42

3'b101: map_dout_Im <= 8'b0001_1101;//3*1/√42

3'b100: map_dout_Im <= 8'b0000_1001;//1*1/√42

default: map_dout_Im <= 0;

endcase

map_dout_Index <= map_dout_Index + 1;

end

default:;

endcase

end

end

再次感谢各位的支持,有这么多错误,真的深表歉意!!!

获取更新内容,可以进上述链接,进文末的链接二进行下载,或者根据文末的指引,在后台回复,也可获取最新工程的下载链接。OFDM 802.11a的FPGA实现:发射部分完整工程