因为PCIE 3.0信号的速率可以达到8Gb/s,而且链路通道走线也可能会很长,这可能会导致高速信号衰减过大,为了补偿channel的衰减需要增加传输信号的高频成分,让高频和低频能量差不多,这就是equalization。因此在PCIE 3.0的Tx和Rx端均使用了均衡设置,以补偿长链路时高速信号的衰减。

一、概述

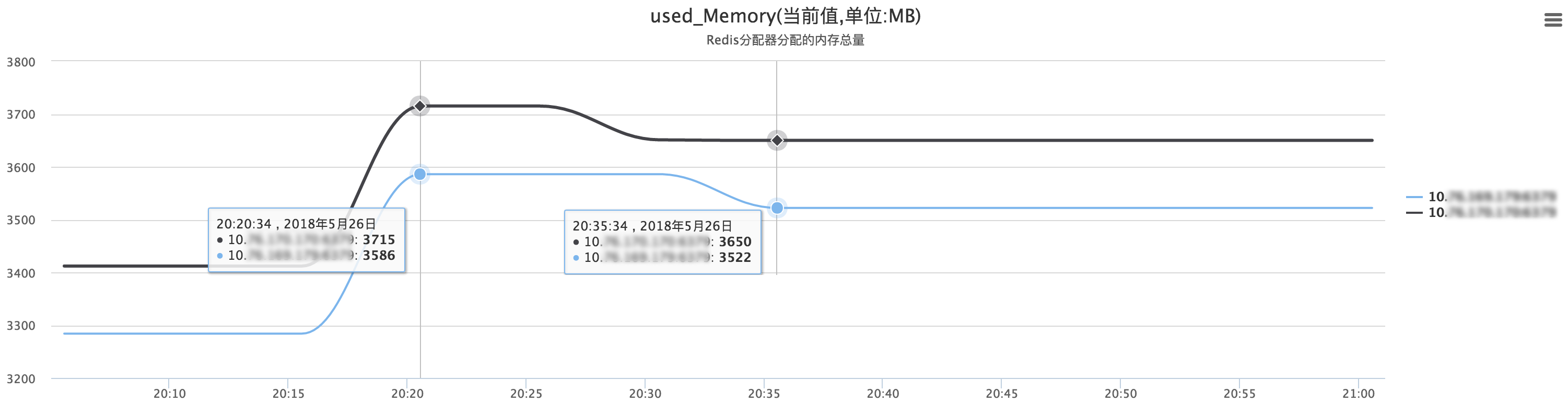

PCB中的信号衰减

参考链接:电路设计相关 第8节

二、动态均衡的实现

软件开发工程师通常不需要关心自适应均衡部分的配置,因为通常自适应均衡由硬件机制完成,详细参考链接:眼图和自适应均衡器

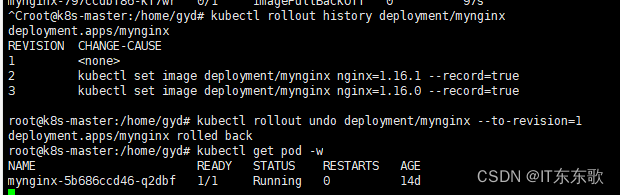

动态均衡在链路训练中作用:均衡器EQ和它在高速外部总线中的应用

参考链接:PCIe3.0动态均衡

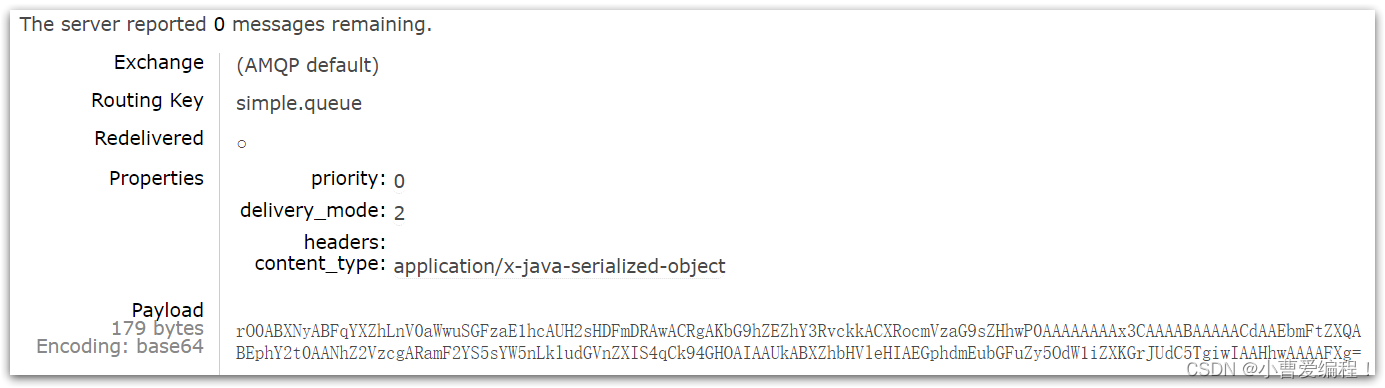

去重(de-emphasis)/预加重(emphasis)

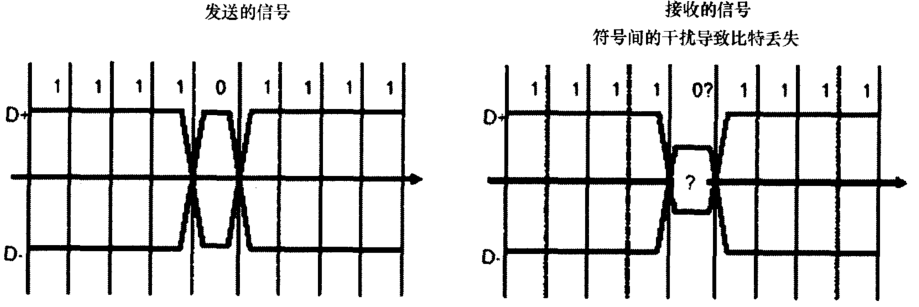

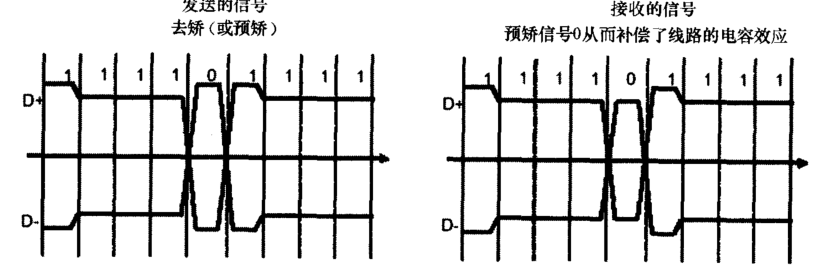

随着发送频率的升高,比特单位间隔降低了,此时发送链路上的电容效应就会很明显,线路电容器将存储电荷,因此当信号保持在恒定的差动电压,即连续发送相同极性的比特使,线路上的电容器将会充电;此时若信号极性突然翻转,由于电容充电电压的减益,输出电压将会减少,导致比特丢失,符号干扰。

一般有两种方案,一种是对相同极性首个比特后所发送的后续比特去矫3.5dB;另一种是对相同极性比特串的首个比特预矫3.5dB

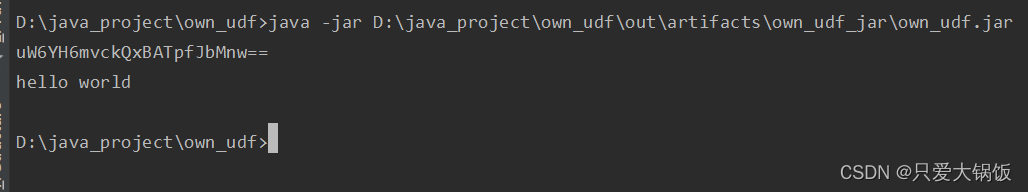

PCIe设备的接收方要求可以检测由于链路线路的影响而比发送值衰减11~13.2dB的差动信号,设计对发送信号进行预矫要求是为了适应某些系统,这些系统具有最差的允许损耗的链路线路。对于低损耗的系统,接收去矫信号的接收器还是有很大的电压余地。

三、接收端的均衡测试

PCIe Gen3/Gen4接收端链路均衡测试(上篇:理论篇)

PCIe Gen3/Gen4接收端链路均衡测试(下篇:实践篇)