目录

- 7.移位操作符

- 8.关系操作符

- 9.相等操作符

- 9.1逻辑等与case等

- 9.2逻辑等与逻辑不等

- 9.3 case等与case不等

- 10.条件操作符

- 11.级联操作符

- 12.复制

微信公众号获取更多FPGA相关源码:

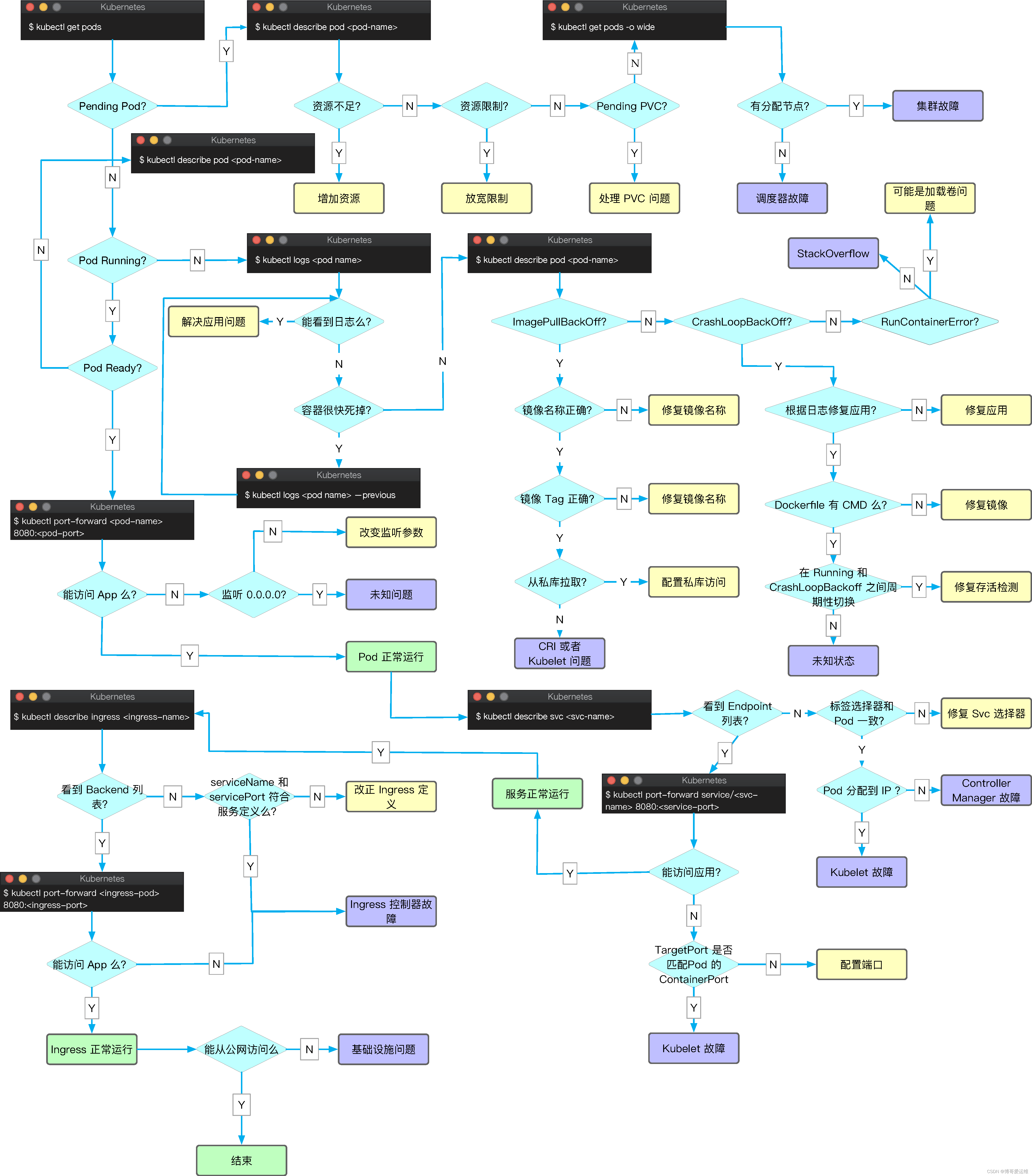

7.移位操作符

| 符号 | 含义 |

|---|---|

| >> | 逻辑右移 |

| << | 逻辑左移 |

- 移位操作符对其左边的操作数进行向左或向右的位移位操作。

- 第二个操作数(移位位数)是无符号数

- 若第二个操作数是x或z则结果为x

- << 将左边的操作数左移右边操作数指定的位数

- >> 将左边的操作数右移右边操作数指定的位数

在赋值语句中,如果右边(RHS)的结果:

- 位宽大于左边,则把最高位截去

- 位宽小于左边,则零扩展

- 建议:表达式左右位数一致

实例:

module shift ();

reg [9: 0] num, num1;

reg [7: 0] rega, regb;

initial rega = 8'b00001100;

initial fork

#10 num <= rega << 5 ; // num = 01_1000_0000

#10 regb <= rega << 5 ; // regb = 1000_0000

#20 num <= rega >> 3; // num = 00_0000_0001

#20 regb <= rega >> 3 ; // regb = 0000_0001

#30 num <= 10'b11_1111_0000;

#40 rega <= num << 2; //rega = 1100_0000

#40 num1 <= num << 2;//num1=11_1100_0000

#50 rega <= num >> 2; //rega = 1111_1100

#50 num1 <= num >> 2;//num1=00_1111_1100

#60 $finish;

join

endmodule

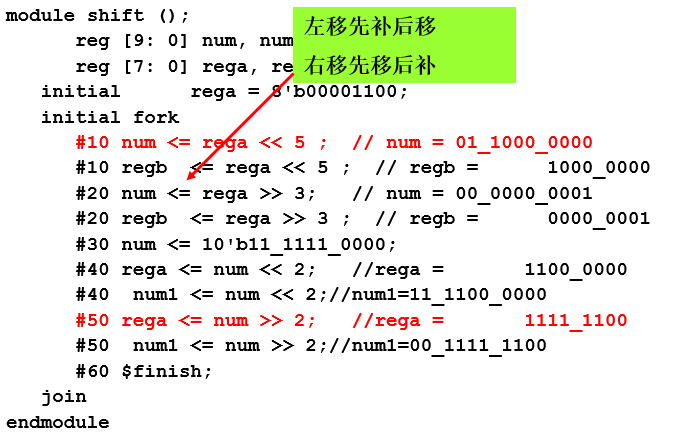

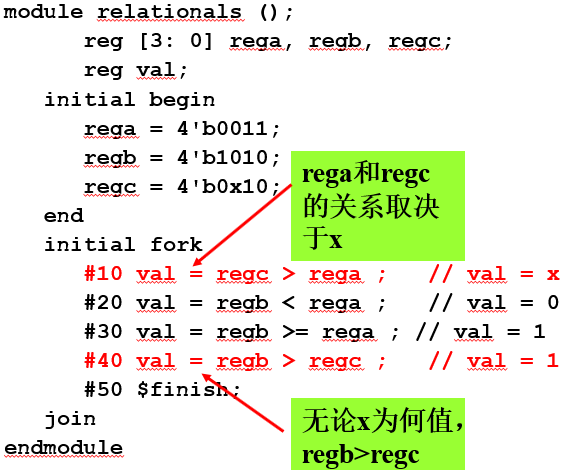

8.关系操作符

| 符号 | 含义 |

|---|---|

| > | 大于 |

| < | 小于 |

| >= | 大于等于 |

| <= | 小于等于 |

关系操作符的结果可以是1’b1、1’b0或1’bx。

实例:

module relationals ();

reg [3: 0] rega, regb, regc;

reg val;

initial begin

rega = 4'b0011;

regb = 4'b1010;

regc = 4'b0x10;

end

initial fork

#10 val = regc > rega ; // val = x

#20 val = regb < rega ; // val = 0

#30 val = regb >= rega ; // val = 1

#40 val = regb > regc ; // val = 1

#50 $finish;

join

endmodule

9.相等操作符

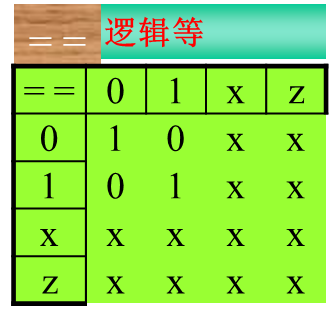

9.1逻辑等与case等

'='赋值操作符,将等式右边表达式的值拷贝到左边。

注意逻辑等与case等的差别:

实例:

a = 2'b1x;

b = 2'b1x;

if (a == b)

$display(" a is equal to b");

else

$display(" a is not equal to b");

- 2‘b1x==2’b0x 值为0,因为不相等

- 2‘b1x==2’b1x 值为x,因为可能不相等,也可能相等

实例:

a = 2'b1x;

b = 2'b1x;

if (a === b)

$display(" a is identical to b");

else

$display(" a is not identical to b");

- 2‘b1x===2’b0x 值为0,因为不相同

- 2‘b1x===2’b1x 值为1,因为相同

**特别注意:**Case等只能用于行为描述,不能用于RTL描述。

9.2逻辑等与逻辑不等

| 符号 | 含义 |

|---|---|

| == | 逻辑等 |

| ! = | 逻辑不等 |

- 其结果是1’b1、1’b0或1’bx。

- 如果左边及右边为确定值并且相等,则结果为1。

- 如果左边及右边为确定值并且不相等,则结果为0。

- 如果左边及右边有值不能确定的位,但值确定的位相等,则结果为x。

- !=的结果与= =相反

值确定是指所有的位为0或1。不确定值是有值为x或z的位。

实例:

module equalities1();

reg [3: 0] rega, regb, regc;

reg val;

initial begin

rega = 4'b0011;

regb = 4'b1010;

regc = 4'b1x10;

end

initial fork

#10 val = rega == regb ; // val = 0

#20 val = rega != regc; // val = 1

#30 val = regb != regc; // val = x

#40 val = regc == regc; // val = x

#50 $finish;

join

endmodule

9.3 case等与case不等

| 符号 | 含义 |

|---|---|

| === | 相同(case等) |

| ! == | 不相同(case不等) |

- 其结果是1’b1、1’b0或1’bx。

- 如果左边及右边的值相同(包括x、z),则结果为1。

- 如果左边及右边的值不相同,则结果为0。

- !==的结果与 === 相反

特别注意:综合工具不支持case等与case不等的写法,只能仿真时使用

实例:

module equalities2();

reg [3: 0] rega, regb, regc;

reg val;

initial begin

rega = 4'b0011;

regb = 4'b1010;

regc = 4'b1x10;

end

initial fork

#10 val = rega === regb ; // val = 0

#20 val = rega !== regc; // val = 1

#30 val = regb === regc; // val = 0

#40 val = regc === regc; // val = 1

#50 $finish;

join

endmodule

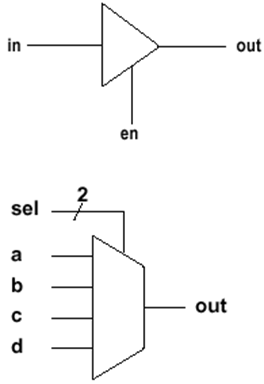

10.条件操作符

| 符号 | 含义 |

|---|---|

| ?: | 条件 |

如果条件值为x或z,则结果可能为x或z。

条件操作符的语法为:

= ? <true_expression>:<false_expression>

其意思是:if condition is TRUE, then LHS=true_expression, else LHS = false_expression

每个条件操作符必须有三个参数,缺少任何一个都会产生错误。

最后一个操作数作为缺省值。

registger = condition ? true_value:false_value;

上式中:

- 若condition为真则register等于true_value;

- 若condition为假则register等于false_value。

- 一个很有意思的地方是,如果条件值不确定,且true_value和false_value不相等,则输出不确定值。

例如:

assign out = (sel == 0) ? a : b;

- 若sel为0则out =a;

- 若sel为1则out = b。

如果sel为x或z:

- 若a = b =0,则out = 0;

- 若a≠b,则out值不确定。

实例:

module likebufif( in, en, out);

input in;

input en;

output out;

assign out = (en == 1) ? in : 'bz;

endmodule

module like4to1( a, b, c, d, sel, out);

input a, b, c, d;

input [1: 0] sel;

output out;

assign out = sel == 2'b00 ? a :

sel == 2'b01 ? b :

sel == 2'b10 ? c : d;

endmodule

11.级联操作符

| 符号 | 含义 |

|---|---|

| {} | 级联 |

可以从不同的矢量中选择位并用它们组成一个新的矢量。

用于位的重组和矢量构造

在级联和复制时,必须指定位数,否则将产生错误。

下面是类似错误的例子:

a[7:0] = {4{'b10}};

b[7:0] = {2{5}};

c[3:0] = {3'b011,'b0};

级联时不限定操作数的数目。在操作符符号{ }中,用逗号将操作数分开。例如:{A, B, C, D}

实例:

module concatenation;

reg [7: 0] rega, regb, regc, regd;

reg [7: 0] new;

initial begin

rega = 8'b0000_0011;

regb = 8'b0000_0100;

regc = 8'b0001_1000;

regd = 8'b1110_0000;

end

initial fork

#10 new = {regc[ 4: 3], regd[ 7: 5],

regb[ 2], rega[ 1: 0]};

// new = 8'b11111111

#20 $finish;

join

endmodule

12.复制

| 符号 | 含义 |

|---|---|

| {{}} | 复制 |

复制一个变量或在{ }中的值,前两个{ 符号之间的正整数指定复制次数。

实例:

module replicate ();

reg [3: 0] rega;

reg [1: 0] regb, regc;

reg [7: 0] bus;

initial begin

rega = 4’b1001;

regb = 2'b11;

regc = 2'b00;

end

initial fork

#10 bus <= {4{ regb}}; // bus = 11111111

// regb is replicated 4 times.

#20 bus <= { {2{ regb}}, {2{ regc}} };

// bus = 11110000. regc and regb are each

// replicated, and the resulting vectors

// are concatenated together

#30 bus <= { {4{ rega[1]}}, rega };

// bus = 00001001. rega is sign-extended

#40 $finish;

join

endmodule

目录

- 7.移位操作符

- 8.关系操作符

- 9.相等操作符

- 9.1逻辑等与case等

- 9.2逻辑等与逻辑不等

- 9.3 case等与case不等

- 10.条件操作符

- 11.级联操作符

- 12.复制

微信公众号获取更多FPGA相关源码: