文章目录

- 一、 SystemVerilog

- 1. SystemVerilog简介

- 2. 基本语法和特性

- 二、实验过程

- hello.v文件

- 引脚分配

- 三、实验效果

- 参考

一、 SystemVerilog

1. SystemVerilog简介

SystemVerilog是一种高级的硬件描述语言(HDL),它不仅继承了Verilog语言的所有特性,还增加了一系列的新特性,使其成为现代电子系统设计和验证的强大工具。以下是对SystemVerilog的更详尽的介绍。

起源与发展: SystemVerilog起源于2002年,由Accellera标准组织开发,并于2005年被IEEE正式采纳为IEEE 1800-2005标准。随着电子系统复杂性的增加,SystemVerilog不断更新,以满足设计者的需求。

设计和验证的重要性: SystemVerilog作为硬件设计和验证的重要工具,它允许设计者以更高的抽象层次来描述和验证复杂的电子系统。在设计阶段,SystemVerilog可以用于创建功能模型和测试平台;在验证阶段,它提供了丰富的特性来构建测试环境和检查设计是否符合预期。

应用领域:

集成电路设计:SystemVerilog用于设计从简单的门电路到复杂的SoC(System on Chip)。

仿真和原型设计:用于快速原型设计和仿真,以验证设计的功能和性能。

形式验证:与形式验证工具结合使用,以数学方式证明设计的属性。

硬件-软件协同设计:支持硬件和软件的并行开发,确保两者的兼容性。

2. 基本语法和特性

数据类型: SystemVerilog引入了多种新的数据类型,包括但不限于:

枚举类型(enum):允许定义一组命名的常量。

结构体(struct):可以创建复杂的数据结构。

联合体(union):允许不同的数据类型共享相同的内存位置。

动态数据类型:如队列(queue)和关联数组(associative arrays)。

面向对象编程: SystemVerilog支持面向对象编程(OOP)的特性,如类(class)和对象(object),以及封装、继承和多态性。

并发建模: SystemVerilog提供了并发建模的机制,如:

进程控制:使用initial和always块来描述并发行为。

并发语句:如fork-join,允许设计者编写并行执行的代码块。

断言(Assertions): SystemVerilog提供了断言功能,用于在设计中检测错误和违反设计意图的行为。断言包括:

立即断言(immediate assertions):在代码执行时立即检查条件。

时序断言(concurrent assertions):在仿真过程中持续检查条件。

随机化: SystemVerilog支持随机化测试,允许自动生成测试向量,提高测试的覆盖率和效率。

封装: SystemVerilog支持模块化设计,通过模块(module)、程序包(package)和类(class)等封装机制,提高代码的重用性和可维护性。

时序: SystemVerilog提供了高级的时序控制语句,如always_ff,用于精确控制时序行为。

系统任务和函数: SystemVerilog扩展了系统任务和函数,使得与仿真环境的交互更加灵活。

其他特性:

属性(Properties):用于定义可以在整个仿真过程中持续检查的时序属性。

接口(Interfaces):用于定义模块之间的通信协议,简化了复杂的连接和通信。

覆盖率分析:支持覆盖率分析,帮助设计者评估测试的完整性。

SystemVerilog的这些特性使其成为现代电子设计自动化(EDA)工具的核心语言之一,广泛应用于从设计到验证的各个阶段。随着技术的发展,SystemVerilog将继续演进,以满足电子系统设计日益增长的复杂性和性能要求。

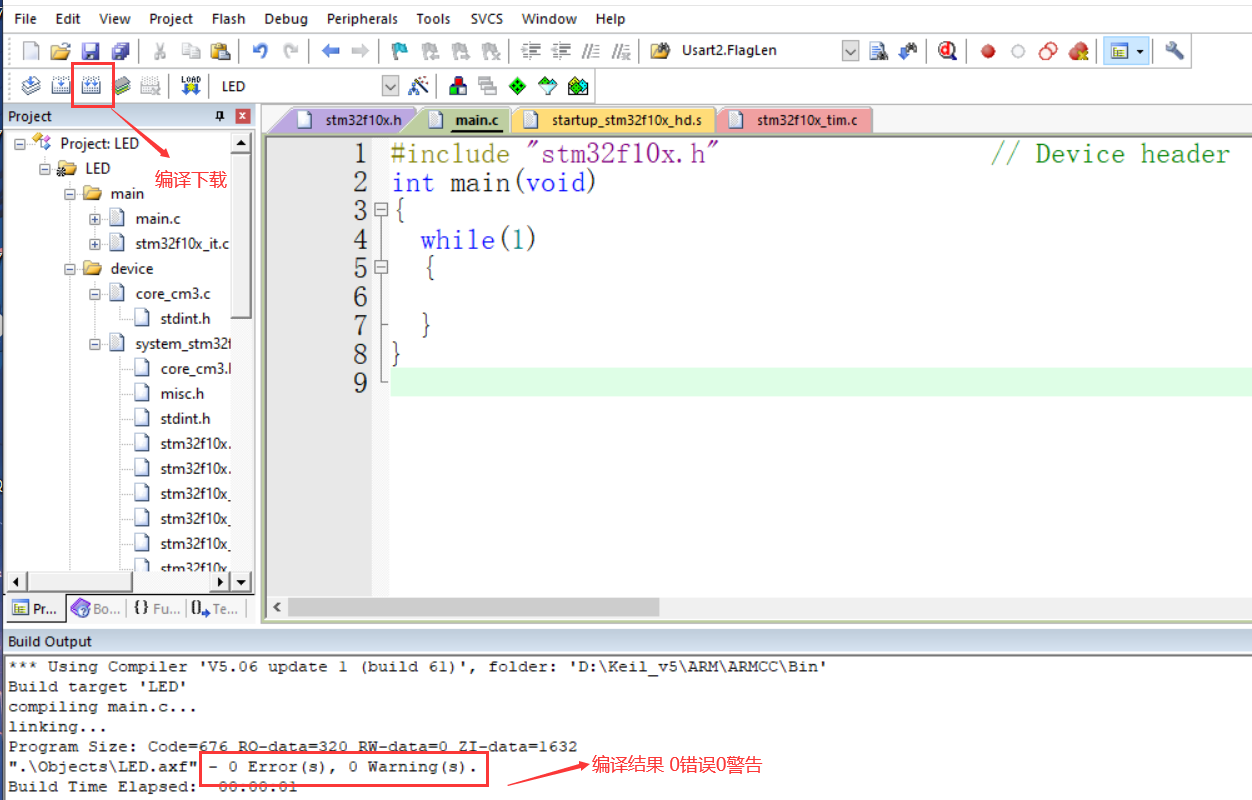

二、实验过程

hello.v文件

module Hello(

input clock,

input reset,

output [7:0] io_led

);

`ifdef RANDOMIZE_REG_INIT

reg [31:0] _RAND_0;

reg [31:0] _RAND_1;

`endif // RANDOMIZE_REG_INIT

reg [31:0] counter; // @[Hello.scala 57:24]

reg [2:0] position; // @[Hello.scala 58:25]

wire [31:0] _counter_T_1 = counter + 32'h1; // @[Hello.scala 61:22]

wire [2:0] _position_T_1 = position + 3'h1; // @[Hello.scala 67:28]

assign io_led = 8'h1 << position; // @[Hello.scala 72:18]

always @(posedge clock) begin

if (reset) begin // @[Hello.scala 57:24]

counter <= 32'h0; // @[Hello.scala 57:24]

end else if (counter == 32'h4c4b40) begin // @[Hello.scala 62:30]

counter <= 32'h0; // @[Hello.scala 63:13]

end else begin

counter <= _counter_T_1; // @[Hello.scala 61:11]

end

if (reset) begin // @[Hello.scala 58:25]

position <= 3'h0; // @[Hello.scala 58:25]

end else if (counter == 32'h4c4b40) begin // @[Hello.scala 62:30]

if (position == 3'h7) begin // @[Hello.scala 64:28]

position <= 3'h0; // @[Hello.scala 65:16]

end else begin

position <= _position_T_1; // @[Hello.scala 67:16]

end

end

end

// Register and memory initialization

`ifdef RANDOMIZE_GARBAGE_ASSIGN

`define RANDOMIZE

`endif

`ifdef RANDOMIZE_INVALID_ASSIGN

`define RANDOMIZE

`endif

`ifdef RANDOMIZE_REG_INIT

`define RANDOMIZE

`endif

`ifdef RANDOMIZE_MEM_INIT

`define RANDOMIZE

`endif

`ifndef RANDOM

`define RANDOM $random

`endif

`ifdef RANDOMIZE_MEM_INIT

integer initvar;

`endif

`ifndef SYNTHESIS

`ifdef FIRRTL_BEFORE_INITIAL

`FIRRTL_BEFORE_INITIAL

`endif

initial begin

`ifdef RANDOMIZE

`ifdef INIT_RANDOM

`INIT_RANDOM

`endif

`ifndef VERILATOR

`ifdef RANDOMIZE_DELAY

#`RANDOMIZE_DELAY begin end

`else

#0.002 begin end

`endif

`endif

`ifdef RANDOMIZE_REG_INIT

_RAND_0 = {1{`RANDOM}};

counter = _RAND_0[31:0];

_RAND_1 = {1{`RANDOM}};

position = _RAND_1[2:0];

`endif // RANDOMIZE_REG_INIT

`endif // RANDOMIZE

end // initial

`ifdef FIRRTL_AFTER_INITIAL

`FIRRTL_AFTER_INITIAL

`endif

`endif // SYNTHESIS

endmodule

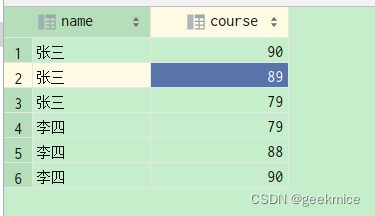

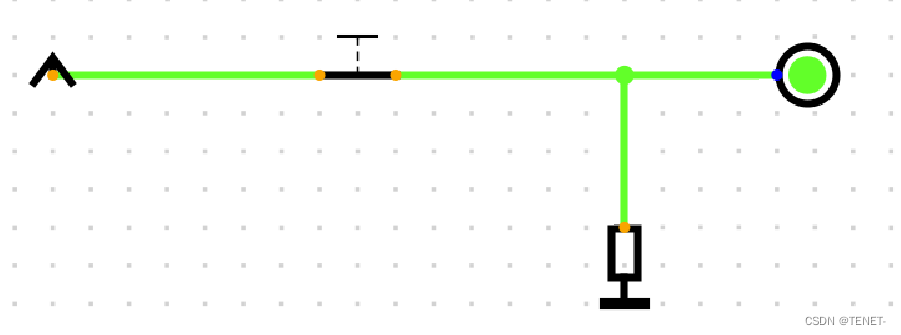

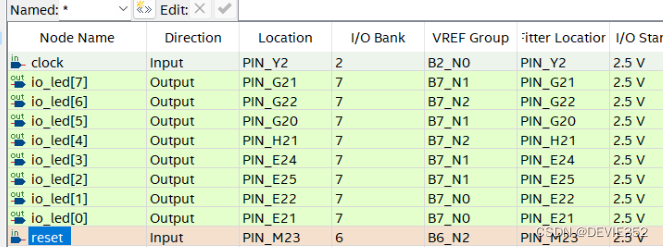

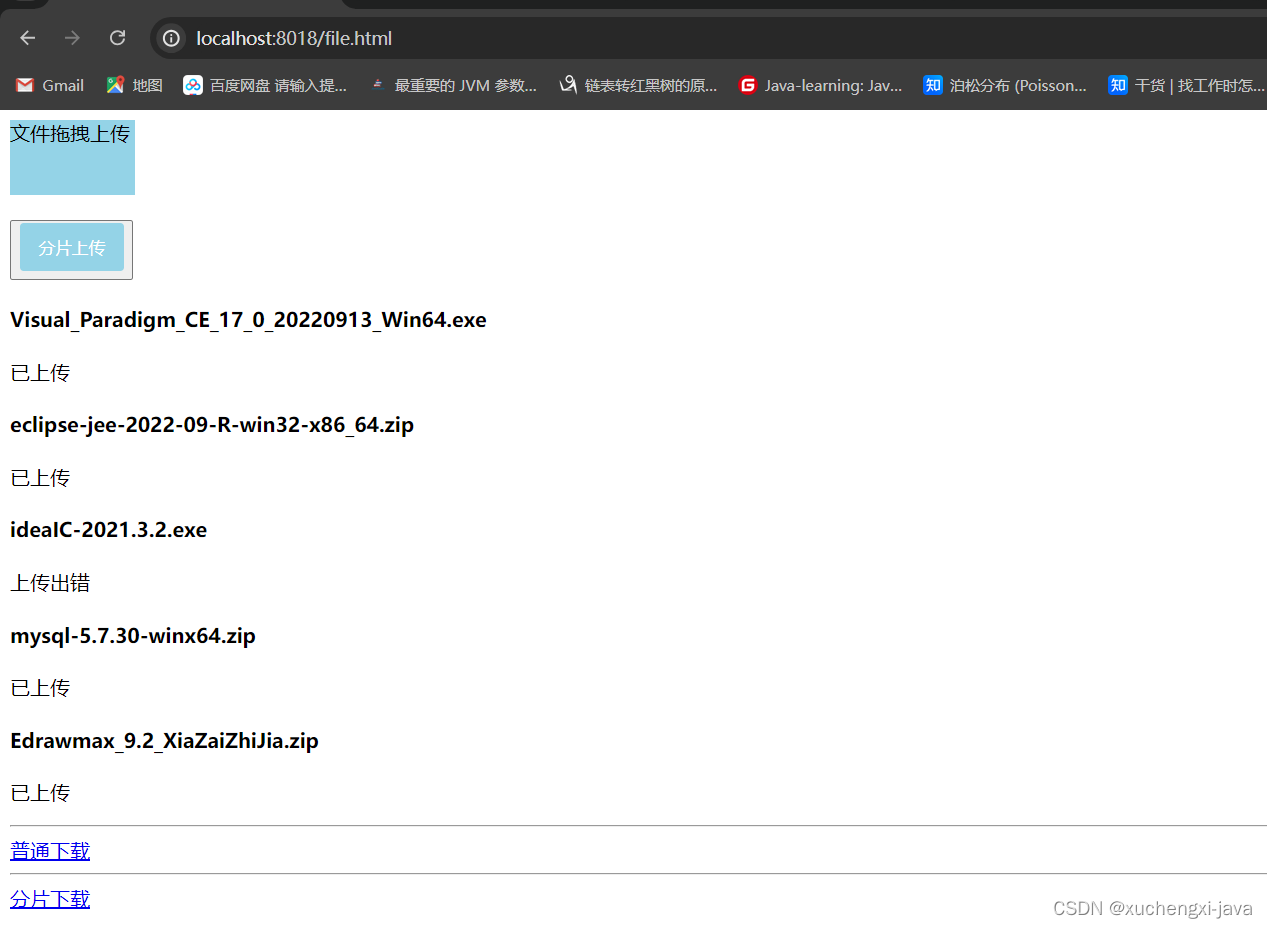

引脚分配

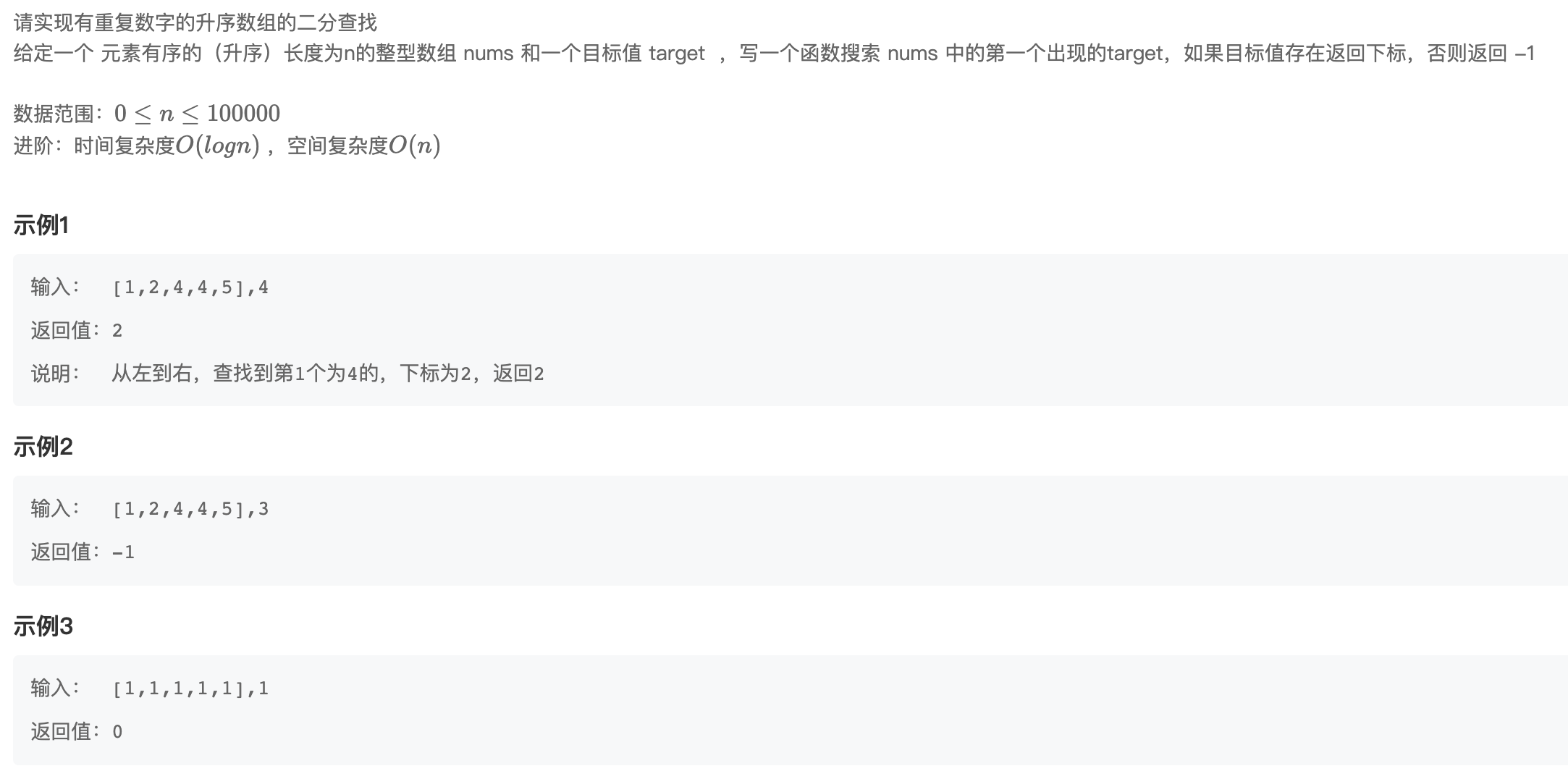

三、实验效果

参考

https://blog.csdn.net/weixin_68811361/article/details/139279336

https://blog.csdn.net/LX567567/article/details/139378799

![[240615] X-CMD 发布 v0.3.11,增加对 elvish 的支持](https://img-blog.csdnimg.cn/direct/3ffac3948b7b4d55b789d40af19a6eb0.gif#pic_center)