随机存取存储器(Random Access Memory,RAM),可以随时把数据写入任一指定地址的存储单元,也可以随时从任一指定地址中读出数据,其读写速度是由时钟频率决定的,主要用来存放程序及程序执行过程中产生的中间数据、运算结果等。

Xilinx 7系列器件内部的BRAM全部是真双端口RAM(True Dual-Port ram,TDP),这两个端口都可以独立地对ZYNQ PL部分的BRAM进行读/写。

也可以被配置成伪双端口RAM(Simple Dual-Port ram,SDP),有两个端口,但是其中一个只能读,另一个只能写。

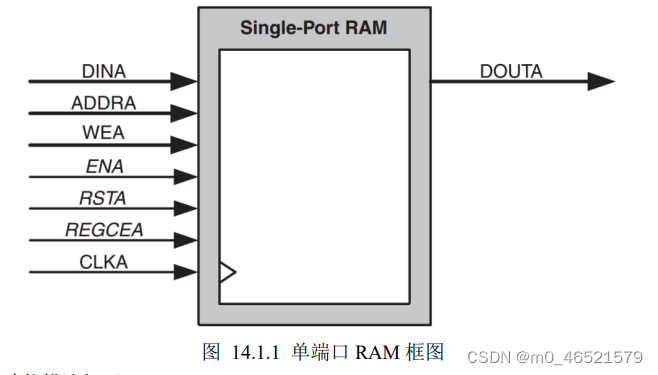

或者单端口RAM,只有一个端口,读/写只能通过这一个端口来进行。

单端口RAM只有一组数据总线、地址总线、时钟信号以及其他控制信号;双端口RAM具有两组数据总线、地址总线、时钟信号以及其他控制信号。

| 名称 | 备注 | |

|---|---|---|

| 1 | DINA | RAM端口A写数据信号 |

| 2 | ADDRA | RAM端口A读写地址信号,对于单端口RAM来说,读地址和写地址共用该地址线 |

| 3 | WEA | RAM端口A写使能信号,高电平表示向RAM中写入数据,低电平表示从RAM中读出数据 |

| 4 | ENA | 端口A的使能信号,可选 |

| 5 | RSTA | RAM端口A复位信号,可选 |

| 6 | REGCEA | RAM端口A输出寄存器使能信号,当REGCEA为高电平时,DOUTA保持最后一次输出的数据,可选 |

| 7 | CLKA | 端口A的时钟信号 |

| 8 | DOUTA | 端口A读出的数据 |