时钟影响ADC性能除了抖动,还有占空比。

在高速AD采样中,时钟占空比是非常重要的一个参数。时钟信号的上升沿控制ADC的采样,而下降沿控制着信号的保持,在一个周期内才可以完成量化输出,所以必须保持时钟的占空比为50%,如果时钟不是50%的话,就会影响采样保持电路中的电荷转换精度。这样就会降低模数转换器的性能。然而即使信号源的占空比是50%,但是时钟所经过的路径上存在的非理想因素,包括驱动器结构或尺寸不对称以及PVT变化等各方面的影响,还是会导致时钟的占空比发生变化。由于这些原因的存在,一般的ADC中都存在一个占空比稳定器电路,来把可能偏离标准50%占空比的时钟调节为50%占空比。

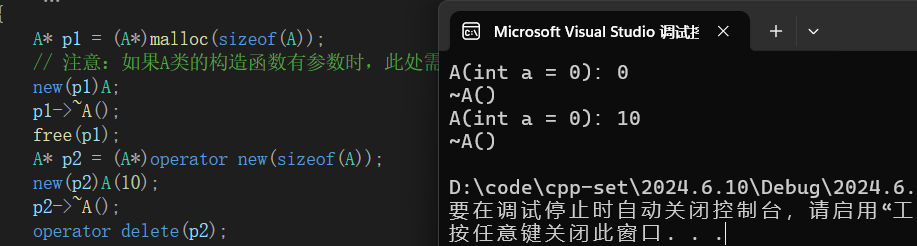

如下图一是ADC采样量化编码的一个过程,采样保持电路受时钟控制,时钟的占空比如果存在问题就会让采样过程存在误差,也就是会影响噪底和非线性特性。

图一 ADC采样量化编码过程:

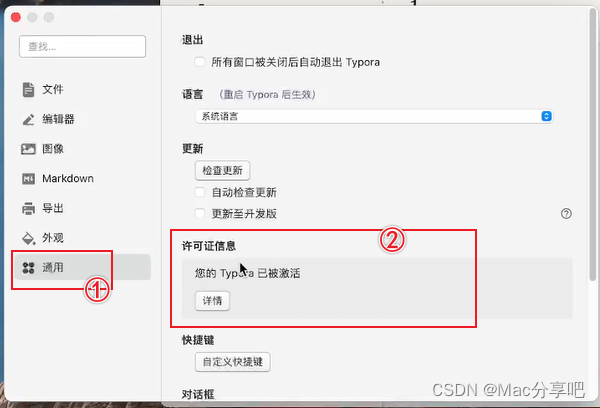

典型的高速ADC利用两个时钟边沿产生不同的内部定时信号,因此,这些ADC可能对时钟占空比很敏感。通常,为保持ADC的动态性能,时钟占空比容差应为±5%。AD9236内置一个占空比稳定器(DCS),可对非采样边沿(或下降沿)进行重新定时,并提供标称占空比为50%的内部时钟信号。因此,时钟输入占空比范围非常广,且不会影响AD9236的性能。当DCS处于开启状态时,在很宽的占空比范围内,30%至70%的占空比下,噪声和失真性能几乎是平坦的,如图二所示,对SFDR的改善尤为明显,也就是说对INL影响比较大。

占空比稳定器使用延迟锁定环(DLL)来创建非采样边缘。因此,采样频率的任何变化都需要大约100个时钟周期,以允许DLL获取并锁定到新的速率。

图二 AD9236时钟占空比与SFDR和SNR之间的关系:

图三 AD9236时钟占空比稳定器位置:

图四 LTC2208 时钟占空比与SFDR和SNR之间的关系:

图四的LTC2208在占空比比较大的情况下,启用DCS会对SNR有明显改善。

图五 LTC2208时钟占空比功能:

TI ADC16V130芯片的占空比稳定器,其具有低附加相位噪声特性。

图六 ADC16V130时钟占空比稳定功能:

图七 时钟占空比锁定电路:

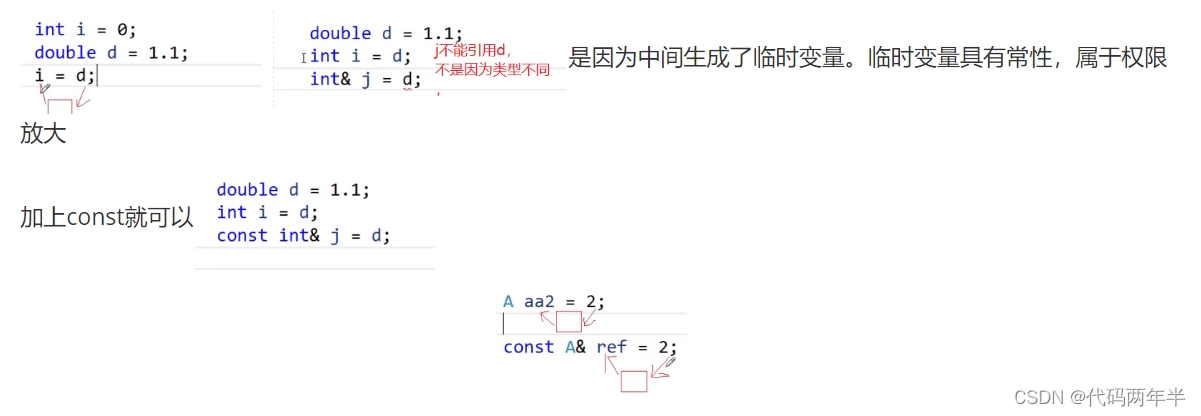

图八 延迟锁环结构:

延迟锁相环在PLL的基础上,使用电压控制延迟线代替了VCO,如图八所示。输入时钟与CK4之间的相位差使用一个鉴相器来检测,从而产生成比例的控制电压,调节每一级的延时。

![【已解决】FileNotFoundError: [Errno 3] No such file or directory: ‘xxx‘](https://img-blog.csdnimg.cn/direct/6782c1b287b449b6b9ef1fb273ac7e34.png)