阻塞和非阻塞是FPGA硬件编程中需要了解的一个概念,绝大部分时候,因为非阻塞的方式更加符合时序逻辑设计的思想,有利于时钟和信号的同步,更加有利于时序收敛,所以除非特殊情况,尽量采用非阻塞方式。

1,非阻塞代码

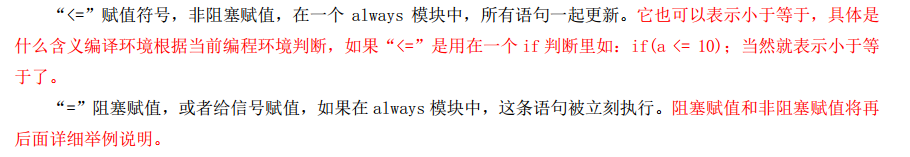

非阻塞赋值,A和B是同时被赋值的,具体是说在时钟的上升沿来的时刻,A和B (或调换A和B)同时被置1。

always @(posedge clk)

begin

A <= 1'b1;

B <= 1'b1;

end

module unblock

(

input clk_i, input rst_n_i, output [4:0]result_o, output [3:0]A, output [3:0]B

);

reg [3:0]A;

reg [3:0]B;

reg [4:0]result_o;

always @(posedge clk_i )

begin

if(!rst_n_i)

begin

A <= 4'd0;

B <= 4'd0;

result_o = 5'd0;

end

else

begin

A <= 4'd2;

B <= B + 1'b1;

result_o <= A + B + 1'b1;

end

end

endmodule仿真

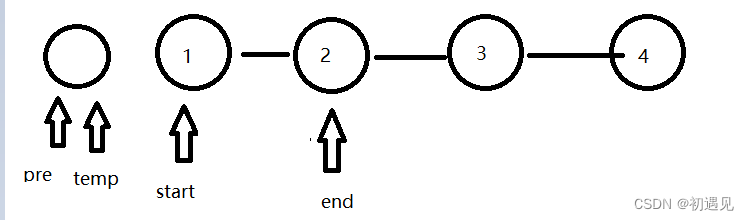

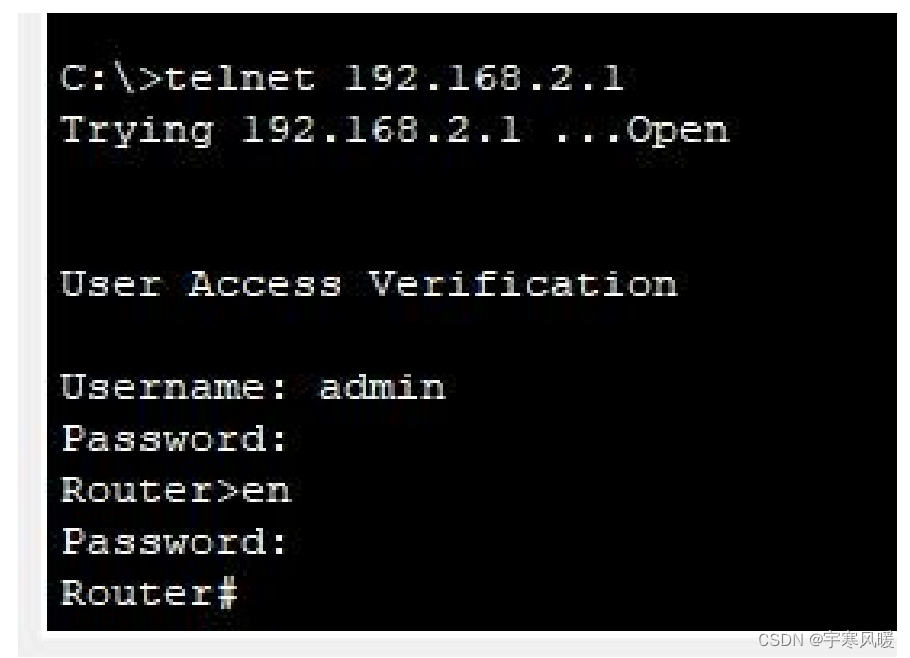

第一个周期上升沿后: A 输出 2 这是个常量; B 输出 1

![python的line[:-1]和line[-1]](https://img-blog.csdnimg.cn/direct/0cd795e076f745f4b34a63462fbf9da9.png)