文章目录

- 1.行波进位加法器

- 2.超前进位加法器

1.行波进位加法器

行波进位加法器就是将全加器串联起来,将低位的进位输出作为高位的进位输入。

由全加器公式可知:

S = A ⊕ B ⊕ C i n C o u t = A B + B C i n + A C i n S=A\oplus B\oplus C_{in}\\ C_{out}= AB+BC_{in}+AC_{in} S=A⊕B⊕CinCout=AB+BCin+ACin

我们可以发现,单级的全加器产生和(将Cin视作已知量)需要1个三输入异或门,即1级电路;产生进位需要两级门电路,即AB/BCIN/ACIN之间的与门以及三项之间的或门。如果将全加器串联起来,后级全加器的进位输入需要前级全加器计算出进位之后才能进行计算,因此串联的全加器越多,其产生进位以及和的链路越长,延迟越大。

4bit行波进位加法器verilog如下:

module twave_carry #(

parameter width = 4

)(

input [width-1:0] A,

input [width-1:0] B,

output [width-1:0] S,

input C_i,

output C_o

);

wire [width:0] C;

genvar i;

generate

for (i=0; i<width; i=i+1)begin

full_adder myadder(

.A (A[i]),

.B (B[i]),

.C_i (C[i]),

.S (S[i]),

.C_o (C[i+1])

);

end

endgenerate

assign C[0] = C_i;

assign C_o = C[width];

endmodule

module full_adder(

input A,

input B,

input C_i,

output S,

output C_o

);

assign S = A ^ B ^ C_i;

assign C_o = A & B | C_i&(A^B);

endmodule

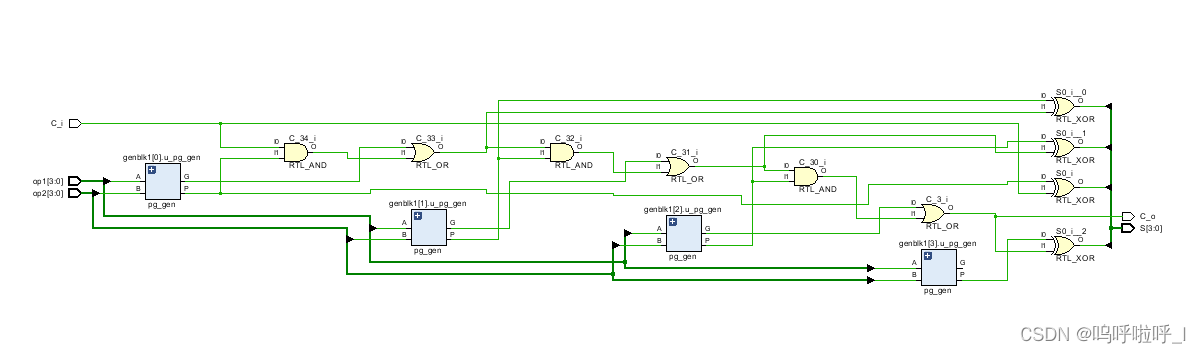

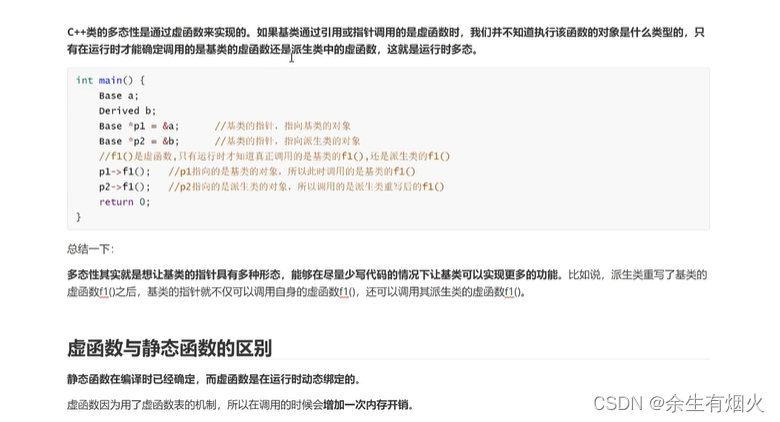

其RTL电路如下图:

将myadder展开:

2.超前进位加法器

超前进位加法器的本质就是并行计算各个进位,无需通过进位传递计算,缩短关键路径。

我们定义生成项G和传输项P:

{ P k = A k ⊕ B k , k = 0 , … , N − 1 G k = A k B k k = 0 , … , N − 1 \left\{\begin{array}{ll}P_{k}=A_{k} \oplus B_{k}, & \mathrm{k}=0, \ldots, \mathrm{N}-1 \\ G_{k}=A_{k} B_{k} & \mathrm{k}=0, \ldots, \mathrm{N}-1\end{array}\right. {Pk=Ak⊕Bk,Gk=AkBkk=0,…,N−1k=0,…,N−1

则和与进位对应的关系表达式为:

{ S k = P k ⊕ C k , k = 1 , … , N C k = G k − 1 + C k − 1 P k − 1 k = 1 , … , N C N = C out C 0 = C in \left\{\begin{array}{ll}S_{k}=P_{k} \oplus C_{k}, & \mathrm{k}=1, \ldots, \mathrm{N} \\ C_{k}=G_{k-1}+C_{k-1} P_{k-1} & \mathrm{k}=1, \ldots, \mathrm{N} \\ C_{N}=C_{\text {out }} & \\ C_{0}=C_{\text {in }} & \end{array}\right. ⎩⎪⎪⎨⎪⎪⎧Sk=Pk⊕Ck,Ck=Gk−1+Ck−1Pk−1CN=Cout C0=Cin k=1,…,Nk=1,…,N

我们将各个进位展开:

{ C 1 = G 0 + C 0 P 0 C 2 = G 1 + C 1 P 1 = G 1 + G 0 P 1 + C 0 P 1 P 0 C 3 = G 2 + C 2 P 2 = G 2 + G 1 P 2 + G 0 P 2 P 1 + C 0 P 2 P 1 P 0 C 4 = G 3 + C 3 P 3 = G 3 + G 2 P 3 + G 1 P 3 P 2 + G 0 P 3 P 2 P 1 + C 0 P 3 P 2 P 1 P 0 \left\{\begin{array}{l}C_{1}=G_{0}+C_{0} P_{0} \\ C_{2}=G_{1}+C_{1} P_{1}=G_{1}+G_{0} P_{1}+C_{0} P_{1} P_{0} \\ C_{3}=G_{2}+C_{2} P_{2}=G_{2}+G_{1} P_{2}+G_{0} P_{2} P_{1}+C_{0} P_{2} P_{1} P_{0} \\ C_{4}=G_{3}+C_{3} P_{3}=G_{3}+G_{2} P_{3}+G_{1} P_{3} P_{2}+G_{0} P_{3} P_{2} P_{1}+C_{0} P_{3} P_{2} P_{1} P_{0}\end{array}\right. ⎩⎪⎪⎨⎪⎪⎧C1=G0+C0P0C2=G1+C1P1=G1+G0P1+C0P1P0C3=G2+C2P2=G2+G1P2+G0P2P1+C0P2P1P0C4=G3+C3P3=G3+G2P3+G1P3P2+G0P3P2P1+C0P3P2P1P0

在上述公式中,以C4举例,比如对于G0P3P2P1这一项,G0、P3、P2、P1四个是并行结构,并且他们四个都是只有一级门电路(与门/或门),因此对于C4来说其一共有三级门电路,从低层次往高层次看分别是G或P中的与门/或门、G与P的相与(与门)、各项(G3、G2P3、…、G0P3P2P1P0)的或门。其结构如下:

而

S k = P k ⊕ C k S_{k}=P_{k} \oplus C_{k} Sk=Pk⊕Ck

则产生和的门电路级数比Ck的门电路多一级(Pk和Ck的异或门,Pk自己内部的异或门和Ck内部的三级门电路视作是并行结构),即4级。

无论加法器位宽是多少,其产生和的级数均为4级,产生进位的级数均为3级。

其verilog如下:

module carry_ahead #( width=4 ) (

input [width-1:0] op1,

input [width-1:0] op2,

input C_i,

output [width-1:0] S,

output C_o

);

wire [width-1:0] G;

wire [width-1:0] P;

wire [width:0] C;

genvar i;

for( i=0; i<width; i=i+1) begin

pg_gen u_pg_gen(

.A( op1[i]),

.B( op2[i]),

.G( G[i] ),

.P( P[i] )

);

end

assign C[0] = C_i;

assign C[1] = G[0] || ( C[0] & P[0] );

assign C[2] = G[1] || ( (G[0] || ( C[0] & P[0]) ) & P[1] );

assign C[3] = G[2] || ( (G[1] || ( (G[0] || (C[0] & P[0]) ) & P[1])) & P[2] );

assign C[4] = G[3] || ( (G[2] || ( (G[1] || ( (G[0] || (C[0] & P[0]) ) & P[1])) & P[2] )) & P[3]);

assign C_o = C[width-1];

genvar k;

for( k=0; k<width; k=k+1) begin

assign S[k] = P[k] ^ C[k];

end

endmodule

module pg_gen(

input A,

input B,

output G,

output P

);

assign G = A & B;

assign P = A ^ B;

endmodule

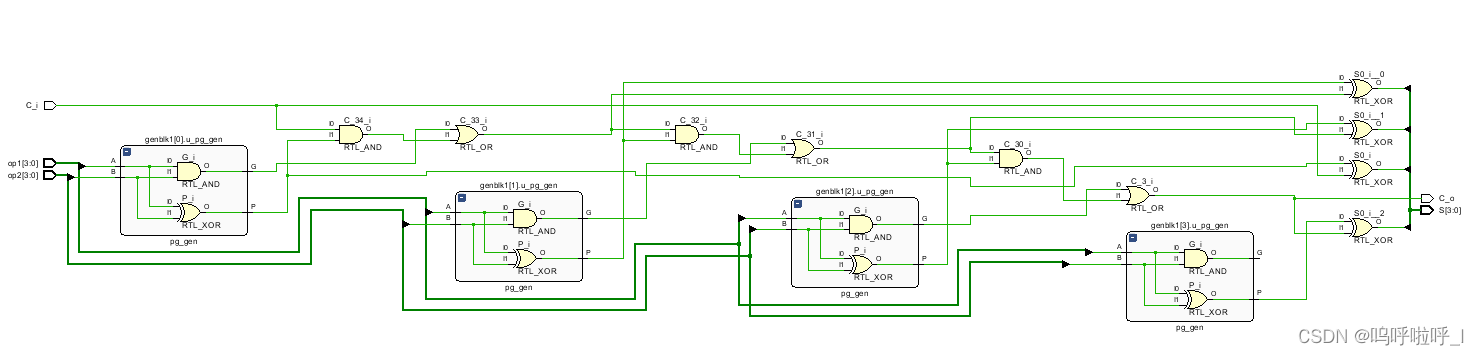

RTL电路结果如下图: