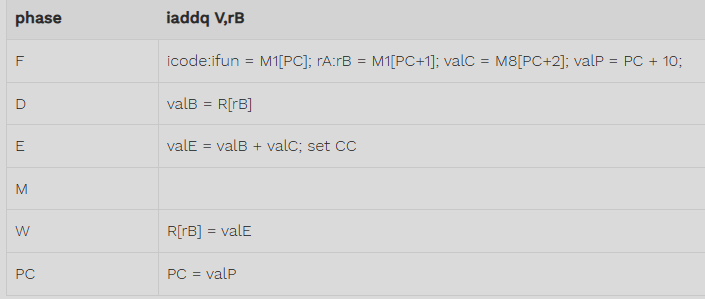

练习题4.3 p.254

\sim\seq\seq-full.hcl文件内已经说的很清楚了哪些不能更改,哪些是题目要求更改的控制逻辑块.

依据家庭作业4.51的答案,在seq-full.hcl文件内更改对应的HCL描述即可 以下答案注释了#changed的就是更改部分

#/* $begin seq-all-hcl */

####################################################################

# HCL Description of Control for Single Cycle Y86-64 Processor SEQ #

# Copyright (C) Randal E. Bryant, David R. O'Hallaron, 2010 #

####################################################################

## Your task is to implement the iaddq instruction

## The file contains a declaration of the icodes

## for iaddq (IIADDQ)

## Your job is to add the rest of the logic to make it work

####################################################################

# C Include's. Don't alter these #

####################################################################

quote '#include <stdio.h>'

quote '#include "isa.h"'

quote '#include "sim.h"'

quote 'int sim_main(int argc, char *argv[]);'

quote 'word_t gen_pc(){return 0;}'

quote 'int main(int argc, char *argv[])'

quote ' {plusmode=0;return sim_main(argc,argv);}'

####################################################################

# Declarations. Do not change/remove/delete any of these #

####################################################################

##### Symbolic representation of Y86-64 Instruction Codes #############

wordsig INOP 'I_NOP'

wordsig IHALT 'I_HALT'

wordsig IRRMOVQ 'I_RRMOVQ'

wordsig IIRMOVQ 'I_IRMOVQ'

wordsig IRMMOVQ 'I_RMMOVQ'

wordsig IMRMOVQ 'I_MRMOVQ'

wordsig IOPQ 'I_ALU'

wordsig IJXX 'I_JMP'

wordsig ICALL 'I_CALL'

wordsig IRET 'I_RET'

wordsig IPUSHQ 'I_PUSHQ'

wordsig IPOPQ 'I_POPQ'

# Instruction code for iaddq instruction

wordsig IIADDQ 'I_IADDQ'

##### Symbolic represenations of Y86-64 function codes #####

wordsig FNONE 'F_NONE' # Default function code

##### Symbolic representation of Y86-64 Registers referenced explicitly #####

wordsig RRSP 'REG_RSP' # Stack Pointer

wordsig RNONE 'REG_NONE' # Special value indicating "no register"

##### ALU Functions referenced explicitly #####

wordsig ALUADD 'A_ADD' # ALU should add its arguments

##### Possible instruction status values #####

wordsig SAOK 'STAT_AOK' # Normal execution

wordsig SADR 'STAT_ADR' # Invalid memory address

wordsig SINS 'STAT_INS' # Invalid instruction

wordsig SHLT 'STAT_HLT' # Halt instruction encountered

##### Signals that can be referenced by control logic ####################

##### Fetch stage inputs #####

wordsig pc 'pc' # Program counter

##### Fetch stage computations #####

wordsig imem_icode 'imem_icode' # icode field from instruction memory

wordsig imem_ifun 'imem_ifun' # ifun field from instruction memory

wordsig icode 'icode' # Instruction control code

wordsig ifun 'ifun' # Instruction function

wordsig rA 'ra' # rA field from instruction

wordsig rB 'rb' # rB field from instruction

wordsig valC 'valc' # Constant from instruction

wordsig valP 'valp' # Address of following instruction

boolsig imem_error 'imem_error' # Error signal from instruction memory

boolsig instr_valid 'instr_valid' # Is fetched instruction valid?

##### Decode stage computations #####

wordsig valA 'vala' # Value from register A port

wordsig valB 'valb' # Value from register B port

##### Execute stage computations #####

wordsig valE 'vale' # Value computed by ALU

boolsig Cnd 'cond' # Branch test

##### Memory stage computations #####

wordsig valM 'valm' # Value read from memory

boolsig dmem_error 'dmem_error' # Error signal from data memory

####################################################################

# Control Signal Definitions. #

####################################################################

################ Fetch Stage ###################################

# Determine instruction code

word icode = [

imem_error: INOP;

1: imem_icode; # Default: get from instruction memory

];

# Determine instruction function

word ifun = [

imem_error: FNONE;

1: imem_ifun; # Default: get from instruction memory

];

bool instr_valid = icode in

{ INOP, IHALT, IRRMOVQ, IIRMOVQ, IRMMOVQ, IMRMOVQ,

IOPQ, IJXX, ICALL, IRET, IPUSHQ, IPOPQ, IIADDQ};#changed

# Does fetched instruction require a regid byte?

bool need_regids =

icode in { IRRMOVQ, IOPQ, IPUSHQ, IPOPQ,

IIRMOVQ, IRMMOVQ, IMRMOVQ , IIADDQ};#changed

# Does fetched instruction require a constant word?

bool need_valC =

icode in { IIRMOVQ, IRMMOVQ, IMRMOVQ, IJXX, ICALL , IIADDQ}};#changed

################ Decode Stage ###################################

## What register should be used as the A source?

word srcA = [

icode in { IRRMOVQ, IRMMOVQ, IOPQ, IPUSHQ } : rA;

icode in { IPOPQ, IRET } : RRSP;

1 : RNONE; # Don't need register

];

## What register should be used as the B source?

word srcB = [

icode in { IOPQ, IRMMOVQ, IMRMOVQ, IIADDQ } : rB;#changed

icode in { IPUSHQ, IPOPQ, ICALL, IRET } : RRSP;

1 : RNONE; # Don't need register

];

## What register should be used as the E destination?

word dstE = [

icode in { IRRMOVQ } && Cnd : rB;

icode in { IIRMOVQ, IOPQ, IIADDQ} : rB;#changed

icode in { IPUSHQ, IPOPQ, ICALL, IRET } : RRSP;

1 : RNONE; # Don't write any register

];

## What register should be used as the M destination?

word dstM = [

icode in { IMRMOVQ, IPOPQ } : rA;

1 : RNONE; # Don't write any register

];

################ Execute Stage ###################################

## Select input A to ALU

word aluA = [

icode in { IRRMOVQ, IOPQ } : valA;

icode in { IIRMOVQ, IRMMOVQ, IMRMOVQ , IIADDQ} : valC;#changed

icode in { ICALL, IPUSHQ } : -8;

icode in { IRET, IPOPQ } : 8;

# Other instructions don't need ALU

];

## Select input B to ALU

word aluB = [

icode in { IRMMOVQ, IMRMOVQ, IOPQ, ICALL,

IPUSHQ, IRET, IPOPQ , IIADDQ} : valB;#changed

icode in { IRRMOVQ, IIRMOVQ } : 0;

# Other instructions don't need ALU

];

## Set the ALU function

word alufun = [

icode == IOPQ : ifun;

1 : ALUADD;

];

## Should the condition codes be updated?

bool set_cc = icode in { IOPQ , IIADDQ};#changed

################ Memory Stage ###################################

## Set read control signal

bool mem_read = icode in { IMRMOVQ, IPOPQ, IRET };

## Set write control signal

bool mem_write = icode in { IRMMOVQ, IPUSHQ, ICALL };

## Select memory address

word mem_addr = [

icode in { IRMMOVQ, IPUSHQ, ICALL, IMRMOVQ } : valE;

icode in { IPOPQ, IRET } : valA;

# Other instructions don't need address

];

## Select memory input data

word mem_data = [

# Value from register

icode in { IRMMOVQ, IPUSHQ } : valA;

# Return PC

icode == ICALL : valP;

# Default: Don't write anything

];

## Determine instruction status

word Stat = [

imem_error || dmem_error : SADR;

!instr_valid: SINS;

icode == IHALT : SHLT;

1 : SAOK;

];

################ Program Counter Update ############################

## What address should instruction be fetched at

word new_pc = [

# Call. Use instruction constant

icode == ICALL : valC;

# Taken branch. Use instruction constant

icode == IJXX && Cnd : valC;

# Completion of RET instruction. Use value from stack

icode == IRET : valM;

# Default: Use incremented PC

1 : valP;

];

#/* $end seq-all-hcl */