AXI UART 16550 IP核实现了PC16550D UART的硬件和软件功能,该UART可以在16450和16550 UART模式下工作。

一、 功能

AXI UART 16550 IP核执行从AXI主设备接收的字符的并行到串行转换,以及从调制解调器或串行外设接收的字符的串行到并行转换。它支持发送和接收8位、7位、6位或5位的字符,以及2位、1.5位或1位的停止位,还支持奇校验、偶校验或无校验。AXI UART 16550 IP核可以独立地发送和接收数据。

AXI UART 16550 IP核具有内部寄存器,用于监视其在配置状态下的状态。该IP核可以发出接收器、发送器和调制解调器控制中断。这些中断可以被屏蔽和设置优先级,并且可以通过读取内部寄存器来识别。该IP核还包含一个16位的可编程波特率生成器,以及独立的、长度为16个字符的发送和接收FIFOs。这些FIFOs可以通过软件进行启用或禁用。

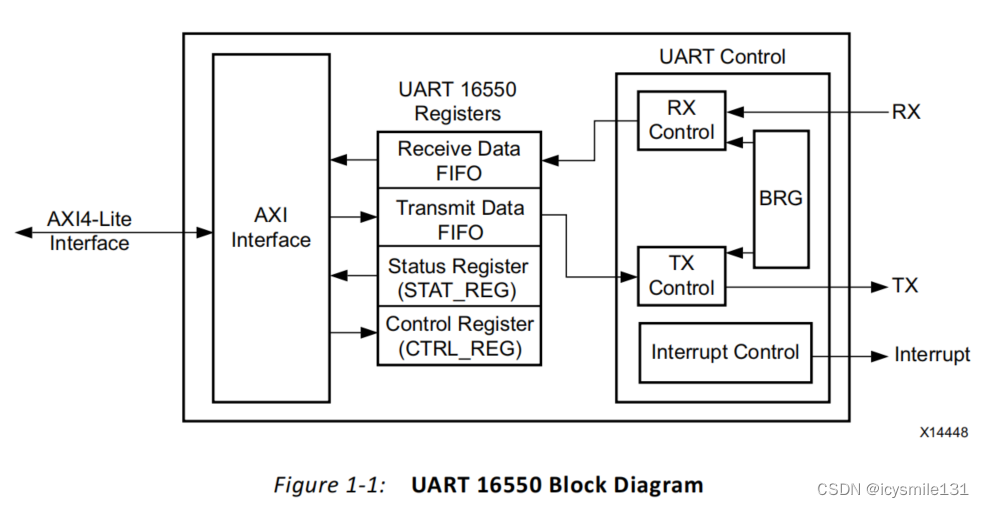

AXI UART 16550 IP核的顶层框图在图1-1中展示。

AXI UART 16550 IP核由几个关键部分组成,共同实现UART(通用异步收发传输器)的基本功能,并允许通过AXI4-Lite接口与外部系统进行通信。以下是对各个部分的详细解释:

- AXI接口(AXI Interface): 实现AXI4-Lite从设备接口,用于寄存器访问和数据传输。

- UART控制(UART Control):包括以下几个模块

①接收控制(RX Control)

根据生成的波特率对接收到的数据进行采样,并将其写入接收数据FIFO。FIFO用于缓存接 收到的数据,直到它们被主处理器读取。

②发送控制(TX Control)

从发送数据FIFO中读取数据,并通过UART TX接口发送出去。发送数据FIFO用于存储等

待发送的数据。

③波特率生成器(BRG, Baud Rate Generator)

生成各种由用户编程设定的波特率。波特率是UART通信中的一个重要参数,它决定了数 据位的传输速率。

3. 中断控制(Interrupt Control):AXI UART 16550 IP核提供了独立的中断使能和中断标识

寄存器。当中断被使能时,以下情况会生成一个电平敏感的中断:

① 接收器线路状态(Receiver line status)

- 溢出错误(Overrun error):当主设备没有读取接收缓冲区,而下一个字符被转移到接收缓冲区寄存器时,会产生中断。在FIFO模式下,只有当FIFO已满,并且下一个字符完全接收在移位寄存器中时,才会产生溢出中断。

- 奇偶校验错误(Parity error):当接收到的字符具有无效的奇偶校验位时,会产生此中断。

- 帧错误(Framing error):如果接收到的字符具有无效的停止位,则会产生此中断。这些中断在读取相关寄存器时被清除。

② 接收数据可用(Received data available):当接收FIFO中有新数据可读,且接收FIFO达到 触发级别时,会产生接收数据可用中断。这个中断在接收FIFO中的数据量低于触发级别时被 清除。

③ 字符超时(Character timeout):当在最近四个字符时间内没有从接收FIFO中移除或输入字 符,并且在这段时间内FIFO中至少有一个字符时,会产生字符超时中断。考虑超时的字符时 间(起始位 + 8个数据位 + 1个奇偶校验位 + 2个停止位)对于所有配置都是恒定的。这个中 断通过读取接收缓冲区寄存器来清除。

④ 发送器保持寄存器为空(Transmitter holding register empty):当字符从发送器保持寄存器 转移到发送器移位寄存器时,会产生此中断。在FIFO模式下,当发送FIFO为空时,会产生 此中断。这个中断可以通过读取中断标识寄存器(IIR)或写入发送器保持寄存器来清除。

⑤ 调制解调器状态(Modem status)

在串行通信中,调制解调器通常用于在计算机和其他设备(如电话线)之间转换数字信号和 模拟信号。当调制解调器遇到特定的状态变化时,它会生成一个中断信号,以通知主机系统 这些状态的变化。

Clear to Send (CTS):当调制解调器准备好接收来自另一端的数据时,它会发送一个CTS信 号。这是用来通知对方,发送端现在可以开始发送数据了。

Data Set Ready (DSR):当调制解调器准备好与对方通信时,它会发送一个DSR信号。这通

常意味着调制解调器已经成功连接到另一端,并准备好进行数据交换。

Ring Indicator (RI): 当有呼叫到来时(例如,在电话线上),调制解调器会发送一个RI信 号。这是用来通知计算机或相关设备有呼叫或消息到达。

Data Carrier Detect (DCD):当调制解调器检测到数据载波(即,它检测到来自另一端的信 号)时,它会发送一个DCD信号。这通常表示物理连接已经建立,并且可能有数据在传输中。

中断的清除:

当主机系统(通常是计算机的某个接口控制器或处理器)检测到上述任一状态变化的中断 时,它会读取“调制解调器状态寄存器”以获取更详细的信息。读取这个寄存器通常会清除中 断,告诉系统已经注意到了这个状态变化,并已经处理了相关的中断服务程序(ISR)。

二、 特性

AXI UART 16550 IP核的的主要特性如下:

- AXI4-Lite接口: 用于访问寄存器和进行数据传输。

- 与标准16450和16550 UART的硬件和软件寄存器兼容:该UART的设计考虑了与常见的16450和16550 UART的兼容性,这意味着许多现有的软件驱动和硬件设计可以很容易地与之集成。

- 默认IP核配置:UART在启动时默认为9600波特率、8位数据长度、1个停止位和无校验位。这些设置是串行通信中常见的默认配置。

- 支持所有标准串行接口协议:

- 字符长度:5、6、7或8位

- 校验位:奇校验、偶校验或无校验

- 停止位:1、1.5或2个

- 内部波特率生成器和独立的接收器时钟输入

- 调制解调器控制功能

- 按优先级的发送、接收、线路状态和调制解调器控制中断

- 错误起始位检测和恢复功能,以处理在接收数据时的起始位错误。线路中断检测和生成,用于检测线路上的长时间空闲状态

- 内部循环回测试功能,允许发送的数据在内部被接收,以进行诊断和测试

- 16个字符的发送和接收FIFO(先进先出)缓冲区,这有助于减少CPU的干预频率,提高通信效率。