基于AXI4-Lite接口可以访问MDIO(Management Data Input/Output)接口,而MDIO接口连接MAC外部的PHY芯片,用户可通过AXI4-Lite接口实现对PHY芯片的配置。

1 MDIO接口简介

开放系统互连模型OSI的最低两层分别是数据链路层和物理层,数据链路层的主要功能包括数据帧的构建、数据差错检查、发送控制和向网络层提供标准的数据接口等;物理层定义了数据发送与接收所需要的电与光信号、线路状态、时钟基准、数据编码和电路等,支持向数据链路层设备提供标准接口。以太网的PHY(物理层)提供传输介质并与MAC层进行连接,将数据转换为光或电信号,而MAC需要配置PHY器件寄存器信息,以保证PHY器件按照使用需求收发数据。

MAC对PHY器件工作状态的确定和对PHY器件的控制是使用MDIO接口读/写 PHY器件的寄存器来完成的。PHY器件的寄存器的地址空间为5位,地址从0到31最多可以定义32个寄存器。IEEE802.3定义了地址为0~15这16个寄存器的功能,地址为16~31的寄存器留给芯片制造商自由定义。PHY器件的状态反映在寄存器内,MAC通过MDIO总线不断读取PHY器件的状态寄存器以得知PHY器件当前的状态,如连接速度、双工能力等。

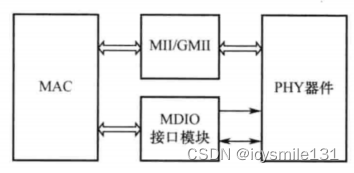

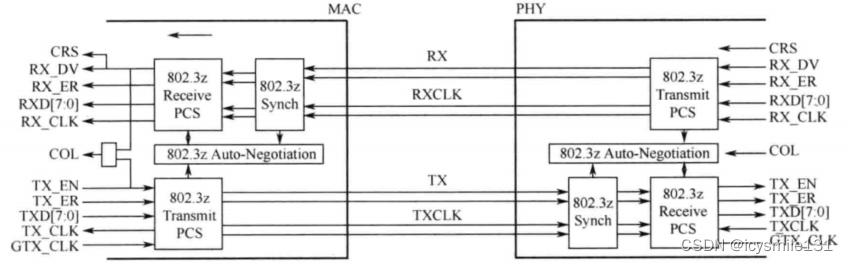

MAC对PHY器件设定的控制管理内容包括:工作速率,10/100/1000Mbps固定速率或自动协商速率;传输介质,光纤或铜线连接物理层设备;工作模式,光纤连接的TBI模式,铜线连接的MII、GMII等模式。MDIO接口正是用于传输MAC对PHY器件控制管理信息的模块,其应用环境如图1所示。

图1 MDIO接口的应用环境

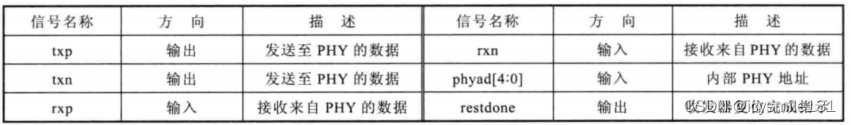

2 MDIO接口信号定义

MDIO接口的应用协议由IEEE802.3标准定义,接口信号包括管理数据时钟(MDC)和MDIO管理数据。

(1)管理数据时钟(MDC)

MDC由MAC驱动,作为MDIO信号线上的时序参考输出到PHY器件。协议定义了MDC的最高工作频率不超过2.5MHz。

(2)MDIO 管理数据

MDIO管理数据是MAC与PHY器件之间的双向串行数据,它被用于传输两者间的状态信息和控制信息。其中,控制信息由MAC产生并与MDC同步,以供PHY器件采样;状态信息由PHY器件驱动,以供MAC读取。

(3)数据帧定义

MDIO接口上的信息是以数据帧的形式进行传输的,MDIO接口数据帧格式如表1所示。

表1 MDIO 接口数据帧格式

● PRE 为帧同步码,MAC向PHY器件发送32个连续的“1”用于器件的同步通信(需要注意的是,该域不是必需的,部分PHY器件的MDIO操作没有PRE)。

● ST 为帧开始标志,MAC输出“01”通知PHY器件帧传输开始。

● OP为帧操作码,“01”表示该帧为1次写操作请求,“10”表示该帧为1次读操作请求。

● PHYAD为PHY器件地址,5bit宽,即一个MDIO总线最多可以外加32(25)个PHY器件。每个PHY器件都把自己的地址与PHYAD进行比较,若匹配则响应后续操作,若不匹配则忽略后续操作。

● REGAD为PHY器件寄存器地址,5bit宽,用于选择PHY器件内部的32个寄存器中的某一个寄存器的地址。

● TA 为状态转换域,2比特。读操作时,第1比特由MDIO模块送出的高阻态来进行设置,第2比特由PHY芯片置为“0”,即“Z0”。写操作时,MDIO信号由MDIO模块控制,输出“10”。

● DATA 为帧寄存器数据域,16比特。读操作时为PHY器件送到MDIO模块的串行数据,写操作时为MDIO模块送到PHY器件的串行数据。

● IDLE为帧结束后的空闲状态,此时是高阻态。由于主从双方共享双向总线,所以一方在控制帧发送完成以后,需迅速将信号置于高阻态,便于其他方占用。

3 TEMAC核中的MDIO控制

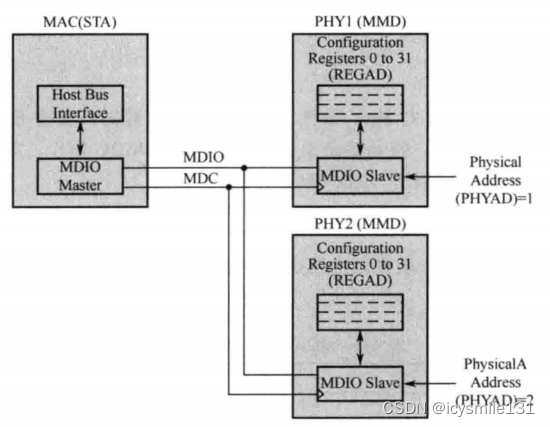

TEMAC核的MDIO总线系统为主从结构,如图2所示。TEMAC核作为主机, PHY器件作为从设备,主机通过MDIO总线发出修改寄存器配置和访问状态寄存器的请求,从设备必须对主机的请求做出响应。

图2 MDIO总线系统示例

(1)MDIO 接口的读/写时序

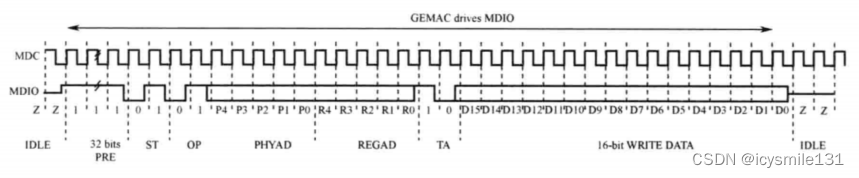

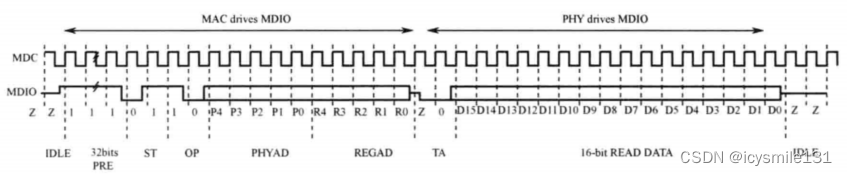

读/写过程由MDIO管理数据帧实现,且由工作在主模式的MDIO初始化,所有工作在从模式的MDIO只要被选中就必须做出应答。MDIO详细说明请参考IEEE802.3标准。如图3所示为MDIO写时序,是MAC核驱动MDIO的过程,操作码OP为“01”,通过匹配PHYAD选中PHY器件,并将16比特的数据域(WRITE DATA)写入PHY器件中匹配REGAD的寄存器。MDIO读时序如图4所示,分为MAC驱动MDIO和PHY驱动MDIO两个阶段,操作码OP为“10”,PHYAD匹配的PHY器件将被REGAD选中的寄存器信息返回给 MDIO模块。

图3 MDIO写时序

图4 MDIO读时序

(2)基于 MDIO 的PHY配置与控制

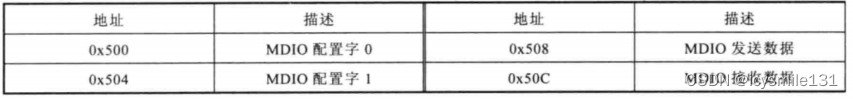

通过管理接口访问MDIO接口是寄存器映射过程,进而实现对PHY寄存器的配置。 MDIO配置寄存器地址如表2所示,各寄存器的比特位详细定义请参考UG800。

表2 MDIO配置寄存器地址

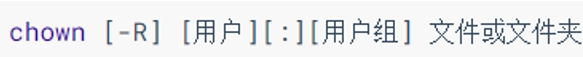

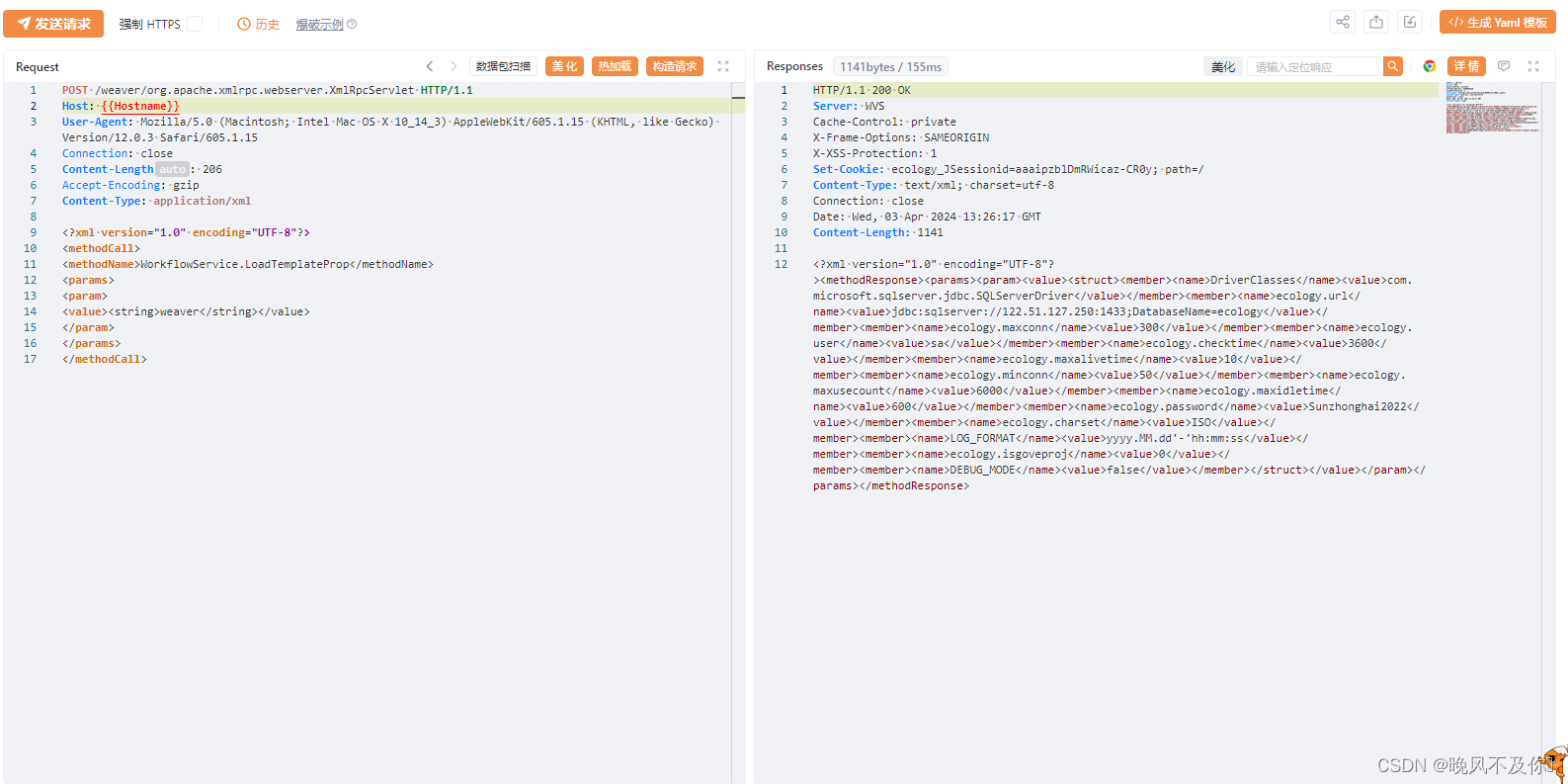

通过AXI4-Lite接口实现1次MDIO写操作:首先将要写入的数据置于MDIO写数据寄存器(WRITEDATA)中,写操作初始化由AXI4-Lite接口设定MDIO配置字1(MDIO Configuration Word1)寄存器实现,OP置为“01”,将要访问的PHY器件地址及其寄存器地址分别写入PHYAD和REGAD。MDIO配置字1寄存器中的第7比特为MDIO READY信号,用于表示MDIO读/写操作是否可用。当写操作配置完成时,MDIO READY信号会被置于无效状态,且MDIOREADY在这次写操作完成后才结束无效状态。

通过AXI4-Lite接口实现1次MDIO读操作:同样由AXI4-Lite接口设定MDIO的配置字1寄存器实现初始化,OP置为“10”,将要访问的PHY器件地址及其寄存器地址分别写入PHYAD和REGAD。当读操作配置完成时,MDIO READY信号会被置于无效状态,直到这次读操作完成;当MDIO READY再次有效时,表示请求读取的数据在MDIO的READ DATA寄存器中,可以被AXI4-Lite接口读出。

4 MII接口分析

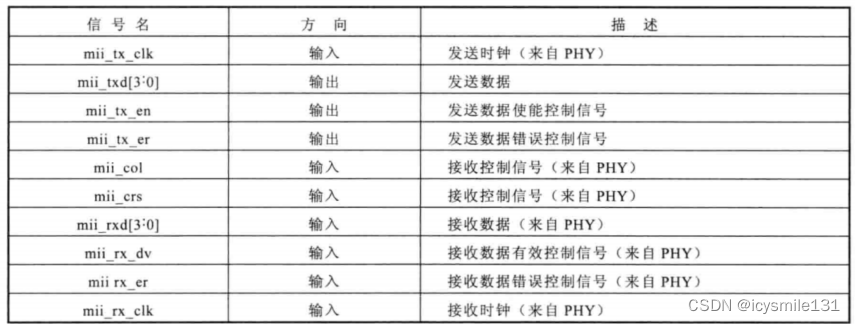

MII即媒体独立接口,也叫介质无关接口,它是IEEE-802.3定义的以太网行业标准。它包括一个数据接口和管理接口:数据接口支持10/100Mbps数据速率,包括16个信号,分为2个独立的发送和接收通道,收发通道都有自己的数据、时钟和控制信号,数据位宽为4比特:管理接口是一个双信号接口,一个是时钟信号,另一个是数据信号。通过管理接口,上层能监视和控制PHY器件。MII接口速率为10Mbps时,时钟频率为2.5MHz:MII接口速率为100Mbps时,时钟频率为25MHz。TEMAC核的MII接口信号简要说明如表3所示。

表3 MII 接口信号简要说明

MII接口使用灵活,但其由2根时钟信号线和14根数据状态信号线组成,接口信号线过多;以MII接口作为交换机接口,将造成引脚数目较多,给芯片和PCB设计带来了一定的难度。通过信号复用、调整数据宽度,设计出了简化版的MII,将MII的16根数据线减少为8根,即RMII接口,数据位宽为2比特。由于TEMAC并不支持RMII,所以这里不再赘述。

5 GMII/RGMII接口分析

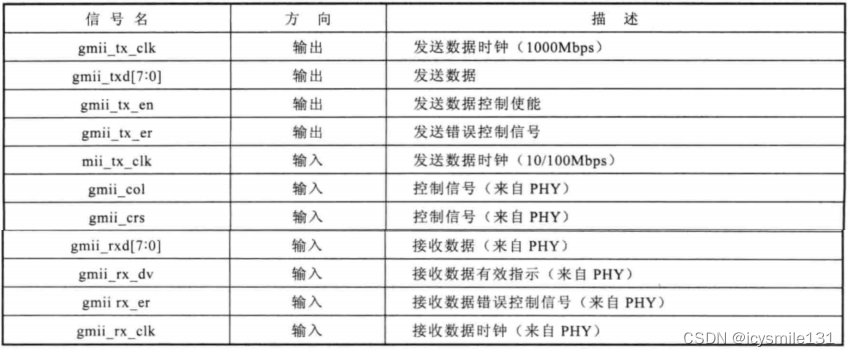

千兆媒体独立接口GMII是对MII的扩展,接口位宽为8比特,支持1000Mbps传输速率(工作时钟为125MHz),同时兼容MII 的10/100Mbps模式。TEMAC核的GMII接口信号简要说明如表4所示。

表4 GMII 接口信号简要说明

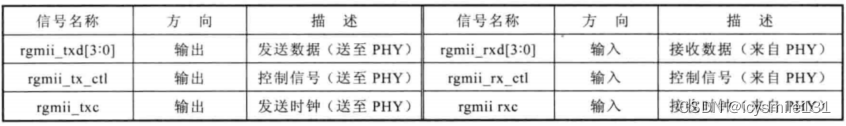

RGMII 接口是简化的GMII接口,支持10/100/1000Mbps的传输速率。TX/RX数据宽度从8位变为4位,时钟频率仍为125MHz,为了保持1000Mbps的传输速率不变,在参考时钟的上升沿发送GMII接口中的TXD[3:0]/RXD[3:0],在参考时钟的下降沿发送 GMII 接口中的TXD[7:4]/RXD[7:4]。由于RGMII使用了双倍速率触发器,并将接口信号线数量从24根减少到14根,比GMII减少了近一半的引脚数,所以PCB设计者更加青睐使用RGMII。TEMAC核的RGMII接口信号简要说明如表5所示。

表5 RGMII 接口信号简要说明

6 SGMII/1000Base-X接口分析

串行吉比特媒体独立接口(Serial GMII, SGMII)和1000BASE-X都是串行接口,SGMII接口将并行的GMII/MII转换为串行信号,支持10/100/1000Mbps。SGMII收发端各采用一对差分信号线,时钟频率为625MHz,采用时钟双沿采样。基于节省引脚数量的考虑, SGMII接口受到了PCB设计者的青睐。1000Base-X即光纤千兆以太网,X表示单模或多模光纤。基于SGMII接口的互连系统如图5所示。

图5 基于SGMII接口的互连系统

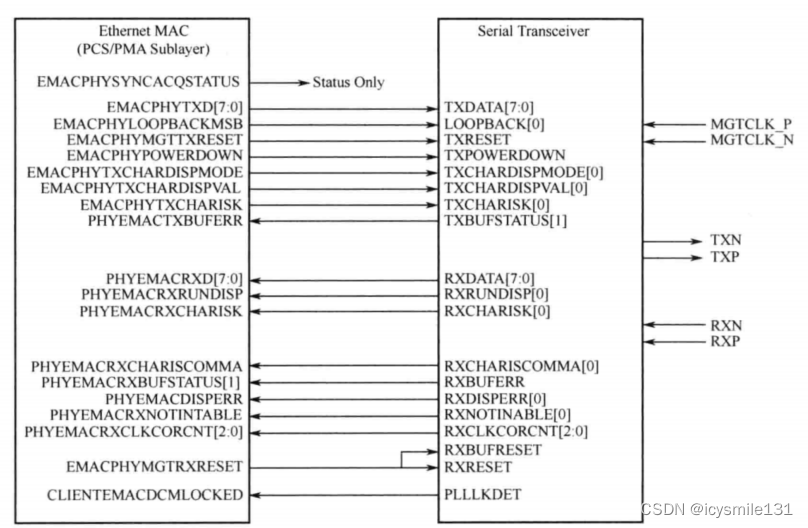

当以太网MAC的物理接口配置为1000BASE-XPCS/PMA或SGMII时,PCS/PMA子层模块将内部并行接口(MII、GMII或RGMII)转换为串行接口(1000BASE-X或 SGMII),串行接口通过串行收发器与外部的光收发器进行通信。当TEMAC配置为1000BASE-X PCS/PMA模式时,与串行收发器的连接如图6所示。

图6 TEMAC配置为1000BASE-XPCS/PMA模式时的连接示意

TEMAC核的SGMII/1000BASE-X接口信号简要说明如表6所示。

表6 SGMII/1000BASE-X接口信号简要描述