Verlog-流水灯-FPGA

引言:

随着电子技术的飞速发展,现场可编程门阵列(FPGA)已成为电子设计自动化(EDA)领域中不可或缺的组件。FPGA以其高度的灵活性和可定制性,广泛应用于通信、图像处理、工业控制等多个领域。为了更好地理解和掌握FPGA的设计和应用,本实验将通过一个简单而经典的项目——流水灯设计——来引入Verilog硬件描述语言的使用。

希望你在本次学习过后,能够有一定的收获!!!

冲啊!!!! ٩(͡๏̯͡๏)۶ ٩(͡๏̯͡๏)۶ ٩(͡๏̯͡๏)۶

文章目录

- Verlog-流水灯-FPGA

- 一、任务介绍

- 二、知识基础

- 1、FPGA知识

- 2、Verilog知识

- 三、实验内容

- 1、实验代码

- 2、实验原理

- 3、实验器材

- 4、引脚配置图

- 四、实验效果

- 五、总结

一、任务介绍

- 熟悉FPGA的开发流程

- 练习并且巩固有关于verilog代码的相关内容

- 使用Verilog语言编写程序实现FPGA的流水灯效果

二、知识基础

1、FPGA知识

FPGA概述: 现场可编程门阵列(Field Programmable Gate Array,简称FPGA)是一种集成了大量可配置逻辑块(CLBs)的半导体设备。这些逻辑块可以通过加载不同的配置文件(通常称为位流文件)来重新定义其功能,从而实现不同的数字电路设计。FPGA的这种可重构特性使其在快速原型开发、复杂数字系统设计和验证等领域非常受欢迎。

FPGA特点:

- 灵活性: FPGA的设计可以随时更改,这使得它们非常适合于原型设计和快速迭代开发。

- 并行性: 由于FPGA内部的逻辑块可以独立编程和并行运行,因此它们可以同时执行多个操作。

- 低功耗: FPGA通常比专用集成电路(ASIC)更加节能。

- 成本效益: 对于小批量生产或需要定制化功能的产品,FPGA提供了一种成本效益高的解决方案。

FPGA设计流程:

- 概念设计: 确定项目需求和FPGA将执行的功能。

- 逻辑设计: 使用硬件描述语言(如Verilog或VHDL)编写代码,描述所需的逻辑功能。

- 仿真测试: 在计算机上模拟设计的逻辑,确保其按预期工作。

- 综合: 将HDL代码转换成FPGA可以理解的门级表示。

- 布局与布线: 将逻辑映射到FPGA的具体物理位置,并连接各个逻辑块。

- 位流生成: 生成配置文件,用于初始化FPGA。

- 下载与测试: 将位流文件下载到FPGA上,并进行实际测试。

FPGA在电子设计中的应用:

- 通信系统: FPGA被用于实现复杂的通信协议和信号处理。

- 视频处理: 在视频监控、图像压缩和显示技术中,FPGA能够处理高速数据流。

- 工业控制: FPGA用于实现定制化的控制算法和接口。

- 医疗设备: 在医疗成像和诊断设备中,FPGA可以提供必要的处理能力。

- 航空航天: 在航空航天领域,FPGA用于导航、遥感和飞行控制系统。

通过掌握FPGA的基础知识,将能够更好地理解流水灯实验的硬件背景,并为后续的实验步骤打下坚实的基础。

2、Verilog知识

Verilog概述: Verilog是一种用于电子系统设计的硬件描述语言(HDL),它允许设计师以文本形式描述复杂的数字逻辑。Verilog语言由Gateway Design Automation公司于1983年开发,并于1989年成为IEEE标准(IEEE 1364-1989),随后经过多次修订,以适应不断变化的设计需求。

Verilog特点:

- 结构化设计: Verilog支持模块化和层次化的设计方法,使得大型设计可以被分解为更小、更易于管理的部分。

- 并发性: Verilog使用并发语句来描述系统中同时发生的事件,这与数字电路的工作原理相吻合。

- 可读性: Verilog的语法类似于C语言,使得有编程背景的工程师更容易上手。

- 仿真能力: Verilog提供了强大的仿真工具,可以在实际硬件实现之前对设计进行测试和验证。

Verilog语言基础:

- 模块(Module): Verilog设计的基本单位,每个模块可以包含输入、输出和内部逻辑。

- 数据类型: 包括线网(wire)、寄存器(reg)、参数(parameter)等,用于定义信号和存储数据。

- 操作符: 提供了位操作符、算术操作符、逻辑操作符等,用于构建逻辑表达式。

- 控制流: 使用

if-else、case、for、while等语句来描述条件和循环逻辑。

Verilog在FPGA设计中的应用:

- 行为描述: 用于描述模块的功能,不涉及具体的逻辑门或电路实现。

- 数据流描述: 侧重于信号之间的数学关系,常用于描述组合逻辑。

- 结构描述: 描述电路的物理实现,包括逻辑门、触发器等的连接方式。

Verilog设计流程:

- 需求分析: 明确设计目标和性能要求。

- 设计编写: 使用Verilog语言编写模块的代码。

- 功能仿真: 对设计进行仿真,验证其逻辑功能是否正确。

- 综合: 将Verilog代码转换成适用于FPGA的门级描述。

- 时序仿真: 检查设计的时序特性,确保满足FPGA的时钟要求。

- 布局布线: 在FPGA上安排逻辑和互连,优化性能和面积。

- 下载测试: 将设计下载到FPGA开发板上,进行实际测试和验证。

三、实验内容

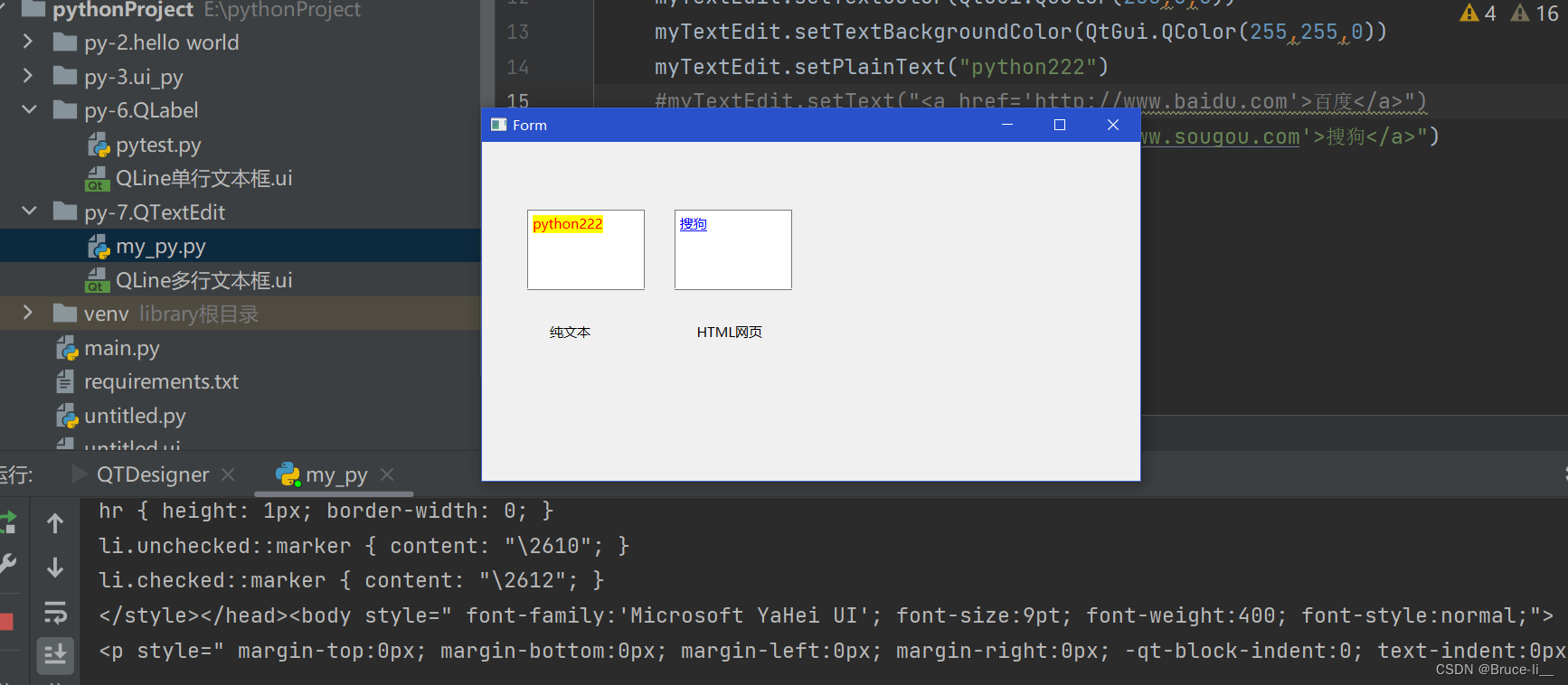

1、实验代码

module led (

input clk,

input rst_n,

output reg[7:0] led

);

parameter TIME_1s = 25_000_000;

reg [30-1:0] cnt_1s ;

wire add_cnt_1s , end_cnt_1s ;

always @(posedge clk or negedge rst_n)

if (!rst_n)

cnt_1s <= 30'b0;

else if (add_cnt_1s )

if (end_cnt_1s )

cnt_1s <=30'b0;

else

cnt_1s <= cnt_1s +1'd1;

else

cnt_1s <= cnt_1s ;

assign add_cnt_1s = 1'b1;

assign end_cnt_1s = add_cnt_1s && (TIME_1s-1 == cnt_1s );

always @(posedge clk or negedge rst_n)

if(!rst_n)

led <= 8'b0000_0001;

else if(end_cnt_1s)

led <= {led[6:0],led[7]};

else

led <= led;

endmodule

2、实验原理

设计目标: 本实验的目标是创建一个简单的流水灯效果,即通过FPGA控制一组LED灯依次点亮,从而产生动态的视觉效果。

设计思路:

- 时钟信号(clk): 提供整个设计的脉冲源,所有的逻辑变化都依赖于时钟信号的上升沿。

- 复位信号(rst_n): 用于初始化和同步系统状态,当复位信号为低时,系统将重置到初始状态。

- LED输出(led): 表示8个LED灯的状态,每一位对应一个LED灯,1表示点亮,0表示熄灭。

核心逻辑:

- 1秒计数器: 使用一个30位的寄存器

cnt_1s来实现1秒的计数。由于FPGA的时钟频率通常远高于1秒的倒数,因此需要通过计数来实现1秒的延迟。 - 计数控制信号:

add_cnt_1s和end_cnt_1s是控制cnt_1s寄存器的关键信号。add_cnt_1s始终为1,表示始终在时钟上升沿增加计数;end_cnt_1s在计数达到TIME_1s - 1时为1,表示1秒时间已到。

实现步骤:

- 初始化: 当复位信号

rst_n为低时,cnt_1s寄存器清零,所有LED灯熄灭。 - 计数: 在每个时钟上升沿,如果复位信号为高,则

cnt_1s寄存器增加1。 - 1秒判断: 当

cnt_1s寄存器的值在时钟上升沿达到TIME_1s - 1时,表示1秒时间已到,此时end_cnt_1s为1。 - LED状态更新: 每当1秒时间到,将最左边的LED状态(

led[7])移动到最右边(led[0]),其余LED状态向左移动一位,从而实现流水灯效果。

代码解析:

- 使用

always块来描述在时钟上升沿或复位信号下降沿时的行为。 if (!rst_n)判断复位信号,如果是复位状态,则重置cnt_1s和led。if (add_cnt_1s)和if (end_cnt_1s)用于控制计数器和LED状态的更新。assign语句用于生成控制信号,add_cnt_1s直接赋值为1,而end_cnt_1s在计数达到预设的1秒时间时为1。

通过上述原理和实现步骤,可以清晰地理解流水灯FPGA设计的核心逻辑和工作流程。

3、实验器材

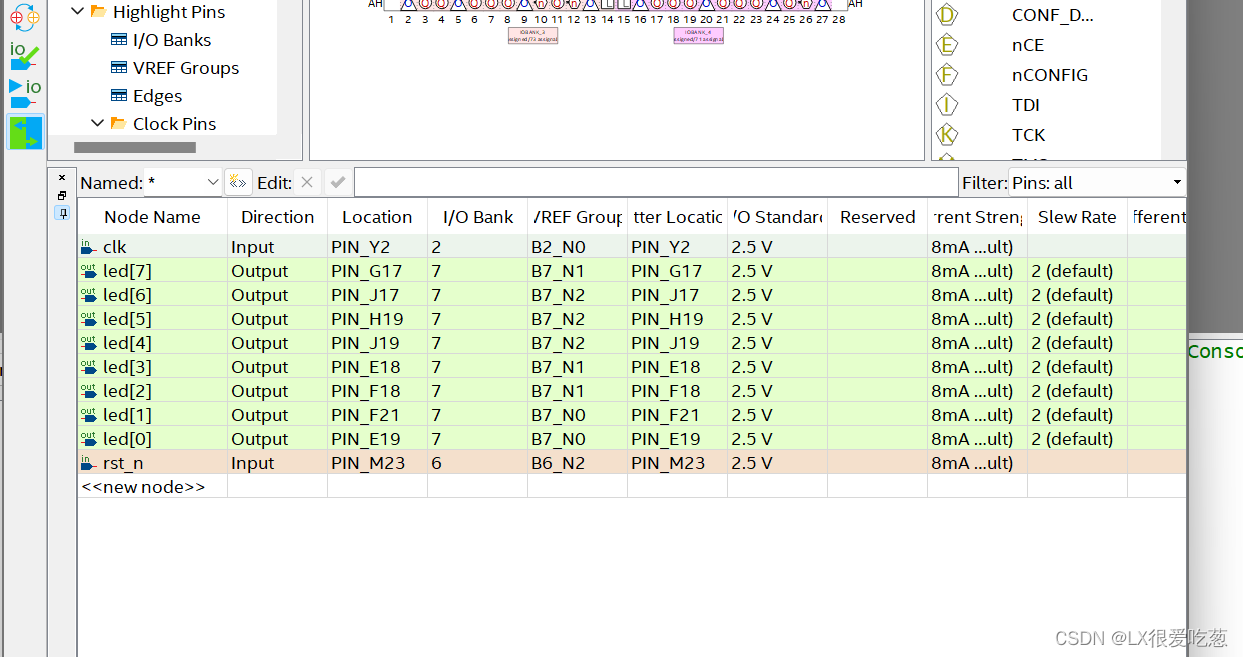

4、引脚配置图

四、实验效果

v-lsd

五、总结

实验目的回顾: 本次实验的核心目的在于通过实践操作,熟悉FPGA的开发流程,并通过编写Verilog代码来实现FPGA的流水灯效果,以此来练习和巩固Verilog编程的相关知识。

实验过程概述:

- 理论学习: 首先需要了解FPGA的基本概念、特点以及设计流程,同时掌握Verilog语言的基础语法和编程技巧。

- 环境搭建: 配置FPGA开发环境,包括安装相应的软件工具和硬件设备。

- 设计实现: 根据实验原理,使用Verilog语言编写流水灯模块的代码,并在开发环境中进行功能仿真。

- 硬件测试: 将编译后的位流文件下载到FPGA开发板上,进行实际的硬件测试,观察LED灯的流水效果。

实验关键点:

- 时钟和复位信号的处理: 理解时钟信号在数字设计中的重要性,以及如何使用复位信号来初始化和同步系统状态。

- 计数器的设计: 学习如何利用计数器产生定时信号,以实现LED灯的顺序点亮。

- 状态寄存器的更新: 掌握如何在Verilog中通过状态寄存器来控制LED灯的状态变化,实现流水灯效果。

实验成果: 通过本次实验,应能够:

- 熟练掌握FPGA的设计流程和开发环境的搭建。

- 深入理解Verilog语言的编程方法,包括模块定义、数据类型、操作符和控制流语句。

- 学会使用Verilog进行基本的数字逻辑设计,如计数器和移位寄存器。

- 能够独立完成从设计、仿真到硬件测试的整个FPGA设计过程。

实验成果: 通过本次实验,应能够:

- 熟练掌握FPGA的设计流程和开发环境的搭建。

- 深入理解Verilog语言的编程方法,包括模块定义、数据类型、操作符和控制流语句。

- 学会使用Verilog进行基本的数字逻辑设计,如计数器和移位寄存器。

- 能够独立完成从设计、仿真到硬件测试的整个FPGA设计过程。

未来展望: 流水灯实验是FPGA设计的一个基础入门项目。未来,可以在此基础上探索更复杂的设计,如加入传感器输入、实现更复杂的逻辑控制、或者设计具有特定功能的数字系统。

![[GESP样题 四级] 填幻方和幸运数](https://img-blog.csdnimg.cn/direct/0f8daa2849034bf89f43c6b2bdff7327.png)