吃瓜群众:机哥,存储是什么玩意,我买手机、电脑的时候导购员都说买内存大的,三星的好,品牌大,问题少,我也只有看哪个内存大就买那个。

机哥:额,这个嘛,说来话长,慢慢说,那我先问你一个问题,你记得上周三中午吃的什么菜么?

吃瓜群众:额,这个记不住了

看吧,如果没记笔记的习惯,上周三吃了什么基本上很少人记得起来,此时需要有一个存储的东西,把这部分内容记录下,电子部分可以理解为存储设备。

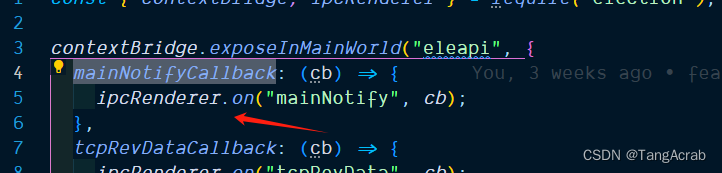

我们先来看看手机上的存储,下图是华为P40pro的硬件配置,可以看到运行内存是8GB,机身存储是128GB,就是常说的8+128的配置,两个都是存储有什么区别呢。

其实第一个就是常说的DDR,就是电脑里面的内存条,这个决定着你跑一些大型应用的时候会不会卡死,比如吃鸡,比如机哥的画硬件软件工具等等。

第二个就是FLASH,也就是相当于电脑里面的硬盘,这个就是决定你可以装多少文件,可以存储拍多少照片,可以下载多少不连续剧,可以下载多少个APP等等。

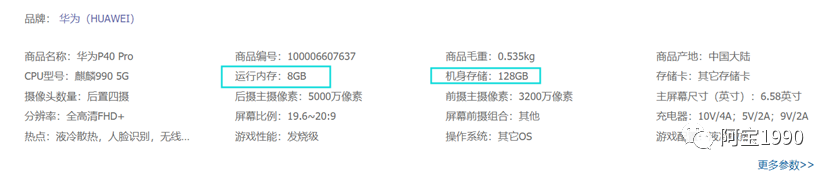

1、存储的分类

人类存储数据的需求可谓历史悠久,存储器的形态历年来也发生了翻天覆地的变化:早期的软盘现早已不见踪影, 光学存储的DVD/CD也渐行渐远, 越来越多的电脑已不再配备光驱,传统的电脑硬盘使用的磁盘作为大量数据存储的首选方案现也已受到SSD的威胁。

众多形态的存储方式按照其原理可大致分为光学存储、半导体存储和磁性存储。半导体存储是存储领域的应用领域最广市场规模最大的存储器件:

按照停电后数据是否可继续保存在器件内,半导体存储器可分为掉电易失和掉电非易失器件;

易失存储器在过去的几十年里没有特别大的变化,依然是以静态随机存取存储器(SRAM) 、动态随机存取存储器(DRAM)为主;

非易失存储器从早期的不可擦除PROM, 到后来的光可擦除EPROM、电可擦除EEPROM, 到现在的主流的Flash, 技术在不断的更新、进步。现在RAM领域还出现了铁电存储器(FRANM)、相变存储器(PRAM) 、磁存储器(MRAM)和阻变存储器(RRAM)等非易失静态存储器,因此市场认为掉电易失器件就是RAM,这种观点是不准确的。

其实这里可以简单理解一下,手机每次关机后重新打开,此时软件需要重新启动吧,此时的启动软件就需要放在FLASH里面,因为掉电后依旧可以保存程序,这样才可以启动,但是你的吃鸡游戏可以不用立马启动,这个界面是可以不起来的,所以那部分的数据是保存在DDR中,一旦掉电了,这部分数据是没有的,需要你重新进入这个游戏才行。

2、存储的发展历程

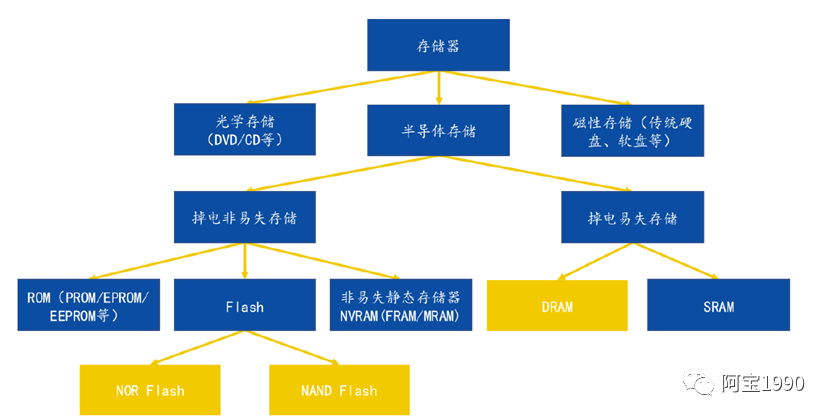

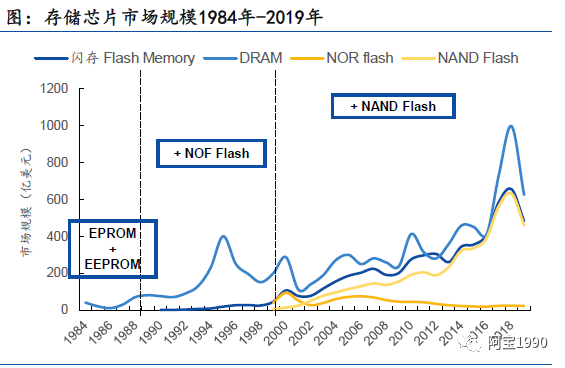

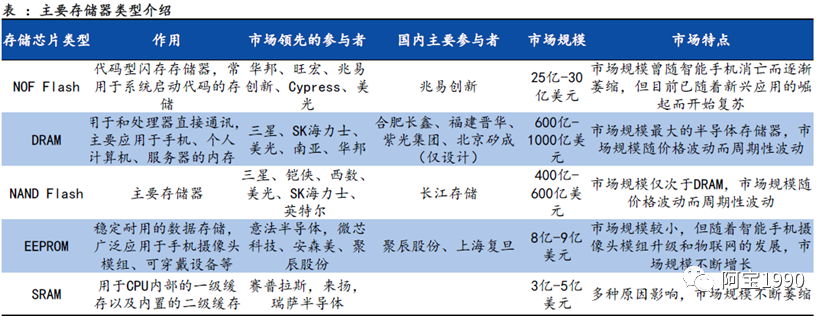

1、存储主要以DRAM、NAND FLASH、NOR FLASH为主。

众多半导体存储器中, 市场规模最大的是DRAM和NAND Flash, 市场规模均在数百亿美元, 其中DRAM 2018年的市场规模已达到1000亿美元。除此之外, 存储芯片市场空间较大的还有NOR Flash, 其市场规模曾一度随着功能手机的消亡而逐渐降低, 但近年来随着新兴市场的崛起, NOR Flash的市场空间也已逐渐恢复。

存储行业兴起于1960s,是半导体行业重要的分支领域,其市场规模由开始的几十亿美元逐渐增长到现在的近1000亿美元, 约占整个半导体行业的25%。DRAM和闪存(FlashMemory) 为存储芯片行业中占比最高的两个分支,销售总额占据了整个存储芯片行业90%以上的市场份额。

存储行业的发展历程大致可分为3个阶段。1990年以前,DRAM为存储芯片市场上主要的产品,且伴随少量的EPROM和EEPROM。1990年至2000年, N OF Flash开始逐步占据一定比例的市场份额。2000年以后,NAND Flash开始爆发式增长, 其市场规模直逼DRAM,而NOF Flash的市场规模于2006年达到顶峰后开始逐渐下滑,但于近两年又开始有微小上升趋势。

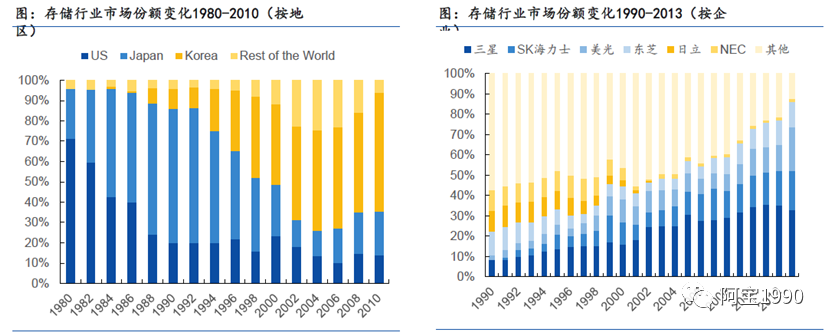

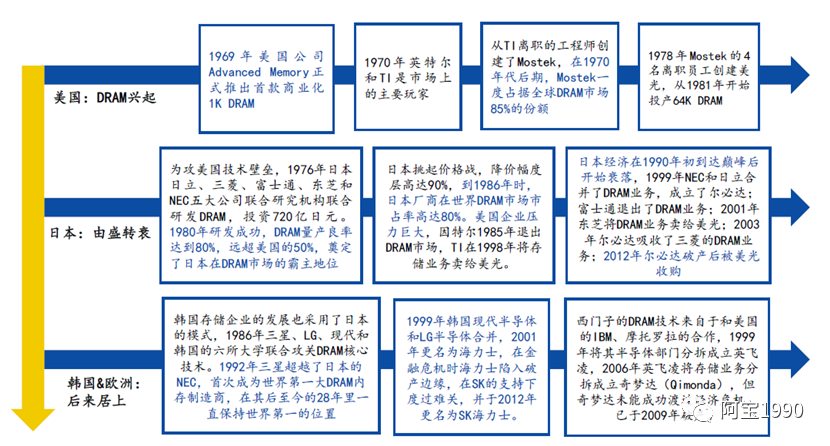

2、存储产业在从美国到日本,日本到韩国的转移。

通过下图可以看到,存储行业的主要玩家伴随历史发展发生了显著的变化,霸主地位由一开始的美国企业(1969-1984年)逐步转移到日本(1985-1996年),最后再转移到韩国企业(1996-现在)。

目前存储行业的主要玩家包括韩国的三星、SK海力士;日本的东芝、铠侠、日立、NEC;美国的美光、英特尔、西部数据等。

3、NAND FLASH发展介绍

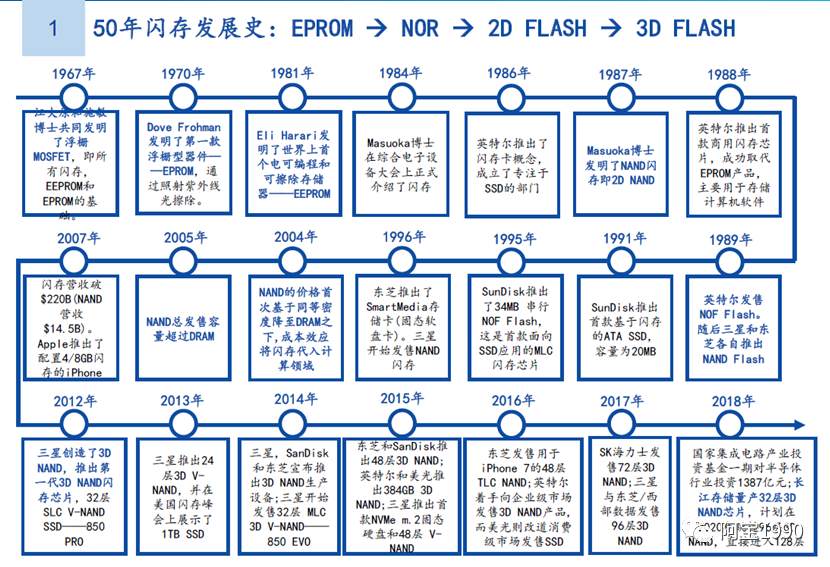

经过50年的发展,闪存从EPROM 到NOR 到2D FLASH,再到现在的3D FLASH发展路径。

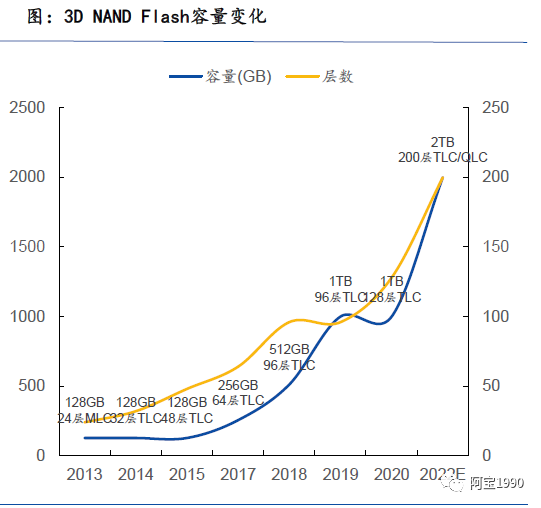

经过50年的闪存芯片发展,闪存容量增势迅猛,20世纪以前,主流的NOF FLASH存储容量普遍在100MB以下,到2004年,闪存存储容量进入GB时代,从2004年的发展到2011年的128GB,2013年的3D NAND Flash 技术的实践使闪存容量进一步提升,由128GB发展到现在的2TB。

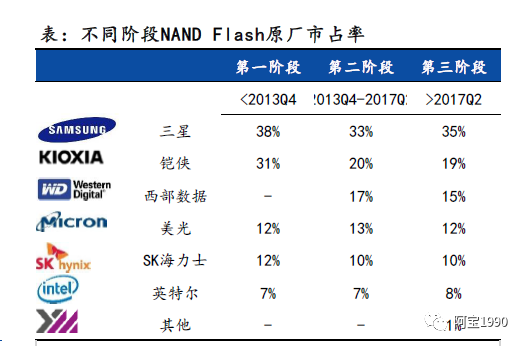

NAND FLASH 原厂颗粒的竞争格局可以大致分为三个阶段:

在2013年Q4以前,三星、铠侠、镁光、海力士和英特尔为5家最大的NAND Flash原厂厂家,几乎占据了全部NAND Flash颗粒市场。

在2013年Q4到2017年Q3之间,西部数据作为另一大NAND flash原厂厂家加入竞争并占据显著的市场份额,铠侠的市占率由此下降了约10%,三星下降了5%。

2017年Q3以后,包括长江存储以内的其余厂商逐渐占据一定的市场份额,打破几乎被前6家大厂垄断的市场格局。

4、DRAM 的发展介绍

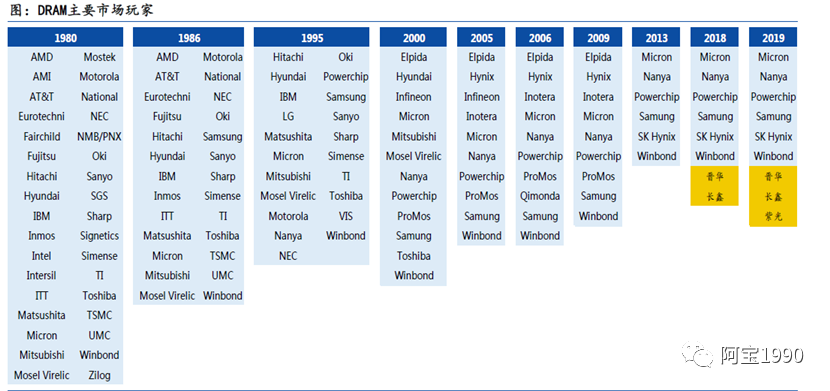

自美国Advanced Memory 推出首款1K DRAM至今已经超过50年,积累创造了1万亿美元的产值,DRAM市场格局变化风气云涌,从1980年代的百家齐放,到2000年的战国纷争,再到现在的寡头垄断,全球的DRAM市场的玩家在不断变化。

目前DRAM芯片的市场格局是三星、SK海力士和镁光统治,三大巨头市场占有率合计超过95%,而三星一家公司市占率就已经逼近50%,寡头垄断的格局使得中国企业对于DRAM芯片议价能力很低,也使得DRAM芯片成为我国受外部制约最严重的基础产品之一。

3、国内重要存储厂家介绍

这两年由于美帝的制裁,存储已经成为众多企业的卡脖子产品,经历过17年内涨价和交期无限长的痛苦日子,越来越多的企业参与存储的研发,加快推出新的产品。国内存储玩家有聚辰股份、长江存储、兆易创新、合肥长鑫、紫光集团等等,下面针对有特点的企业进行简单介绍。

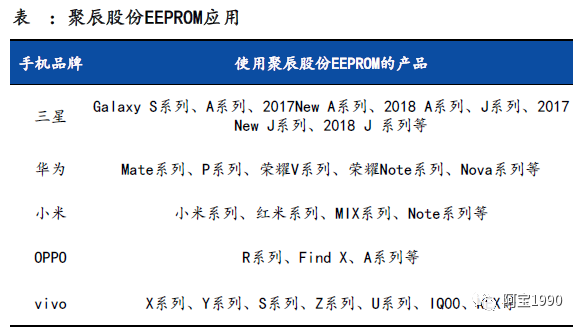

1、聚辰股份EEPROM 市占率最高的国内企业

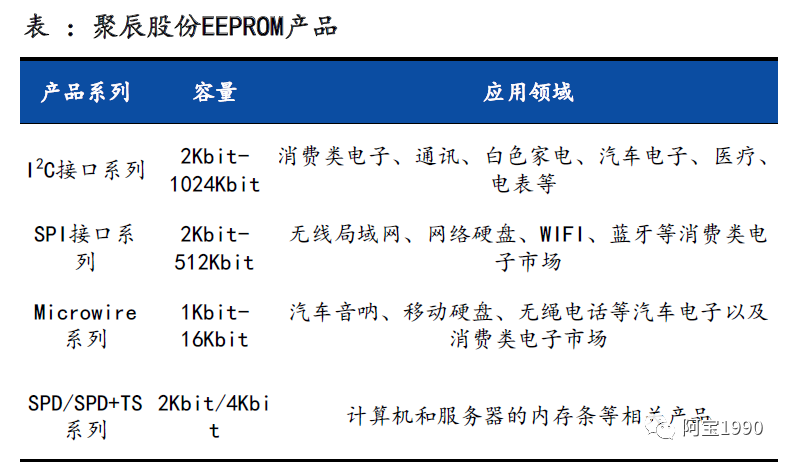

聚辰股份目前拥有EEPROM、音圈马达驱动芯片和智能卡芯片三条产品线, 2019年EEPROM收入占比为88.14 %,为公司核心业务。聚辰股份在 EEPROM 芯片领城市占率全球第三,是手机摄像头 EEPROM 领城占比超过 4 成,客户范围基本涵盖国内一线手机厂商,在此细分领域内是毫无争议的龙头企业。

公司在2018年公司基于1.01u ㎡EEPROM存储单元的容量128KBit 的产品实现量产,此外,公司将不断加码研发投入,开发新型EEPROM产品,提升公司的份额竞争力。

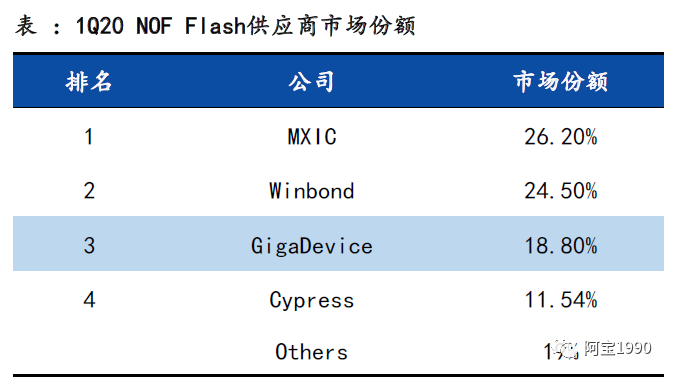

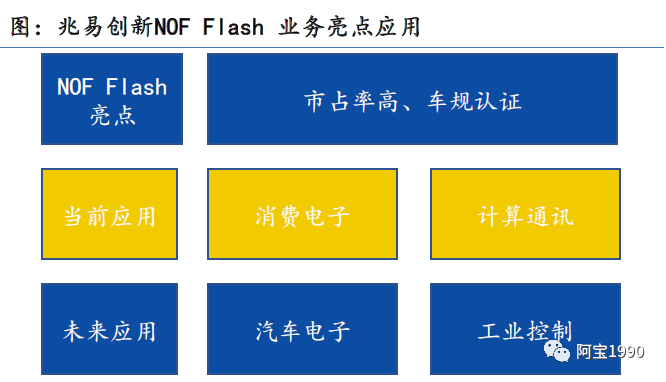

2、兆易创新国内NOR Flash龙头厂商

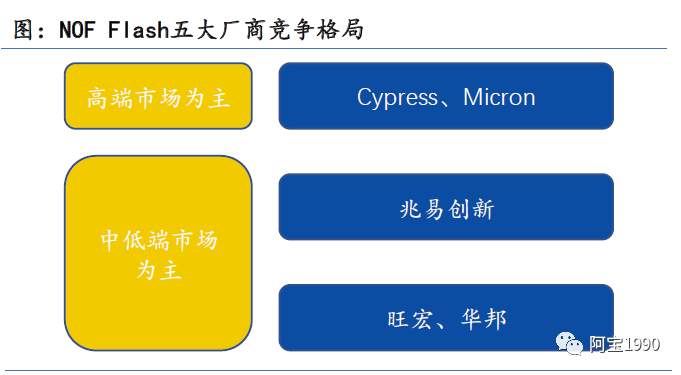

兆易创新是一家致力于各类存储器、控制器及周边产品的设计研发的全球化芯片设计公司。公司立足于最初的NOF Flash 不断研发,陆续推出NAND Flash 和MCU 。其中NOF Flash 收入占比超过 70 %。兆易创新的SPI NOF Flash 在中国市场上占有率为第一,同时也是全球排名前三的供应商之一, 2O20Q1 兆易创新 NOF Flash 市场份额已达18.8 % ,累计出货量超130亿颗,年出货量超28亿颗。

NOF Flash 根据容量可分为高容量(1Gb 及以上)、中(128Mb一1Gb )容量和低容量(128Mb以下)兆易创新主要供应中低容量的NOF Flash 产品,其市占率仍在伴随着美光和 Cypress 在低端 NOF Flash 市场的退出、公司技术能力的进步而持续提升。随着市场空间与市场份额的同步提升,公司的 NOF Flash销量未来仍有较大的提升空间。

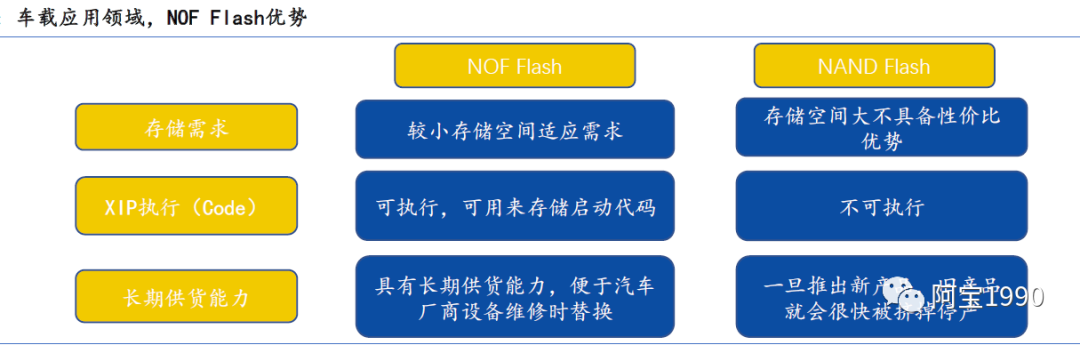

2019 年,兆易创新 GD25 全系列 SPI NOR Flash 产品通过 AECQ100 认证,是目前唯一的全国产化车规闪存产品,可为汽车前装市场以及需要车规级产品的特定应用提供高性能高可靠性性的闪存解决方案。 2020年,公司推出国内首款 2Gb大容量高性能 SPI NOR Flash 产品,主要面向需要大容量存储、高可靠性与超高速数据吞吐量的工业、车载、 Al 以及 SG 等相关应用领域。

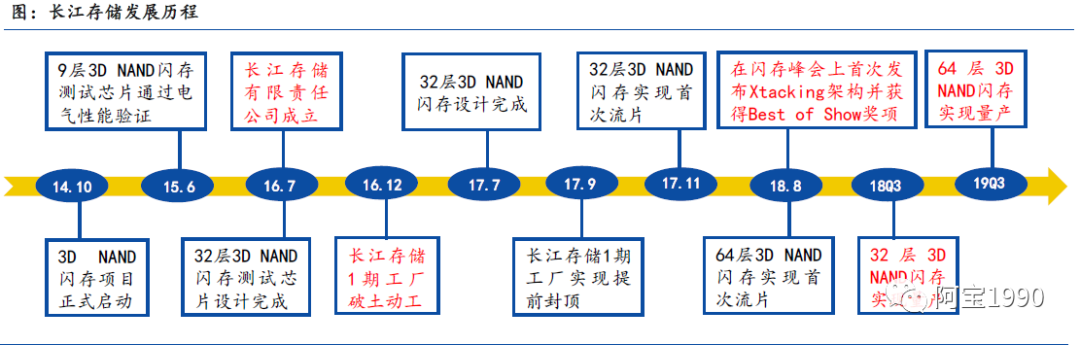

3、长江存储 3D NAND flash

长江存储成立于2016年7月,总部位于武汉,是一家专注于3D NAND闪存芯片设计、生产和销售的IDM存储企业,是紫光集团旗下重要的存储芯片厂商。截至目前长江存储已在武汉、上海、北京等地设有研发中心,全球共有员工5000 余人,其中研发工程师约2000人。公司于2016年底开工建设,并于2018 年底实现32层 3D NAND 的量产。公司首创XtackIng 技术,并使用该技术顺利研发出64层3D NAND ,并于2019年下半年量产256Gb ( 32GB ) TLC 3D NAND 。

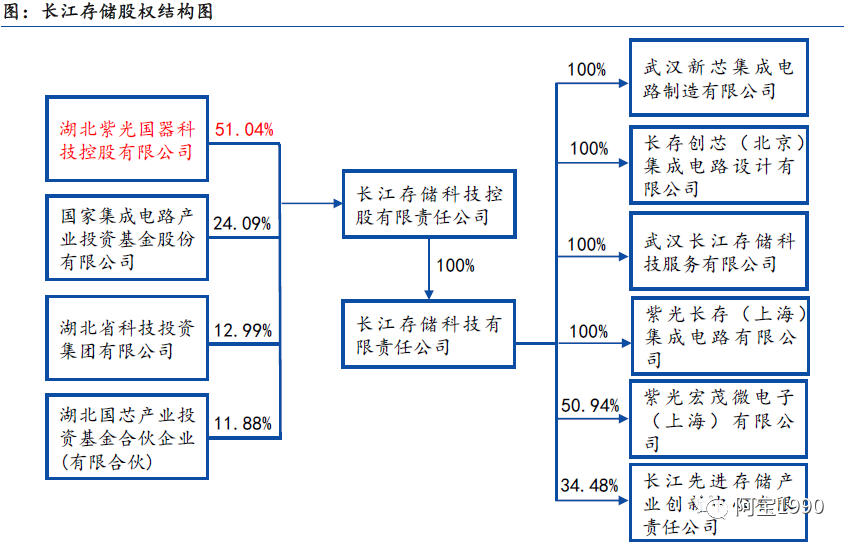

长江存储由湖北紫光国器科技、国家集成电路基金、湖北科技投资和湖北国芯产业投资基金共同控股,其中湖北紫光国器科技为最大股东,占比51.04%。

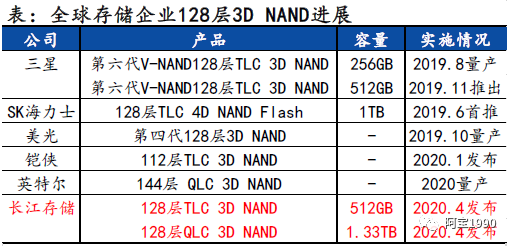

长江存储专注3D NAND闪存业务,于2020年4月10日推出第三代产品128层 3D NAND 存储芯片,直接跳过96层,加速赶超国外厂商先进技术,128层 3D NAND缩小与海外厂商差距至1年。未来,128层QLC版本将率先应用于消费级SSD,并逐步进入企业级服务器、数据中心等领域,以满足未来5G、AI时代多元化数据存储需求。

4、合肥长鑫 国内领先的DRAM制造商

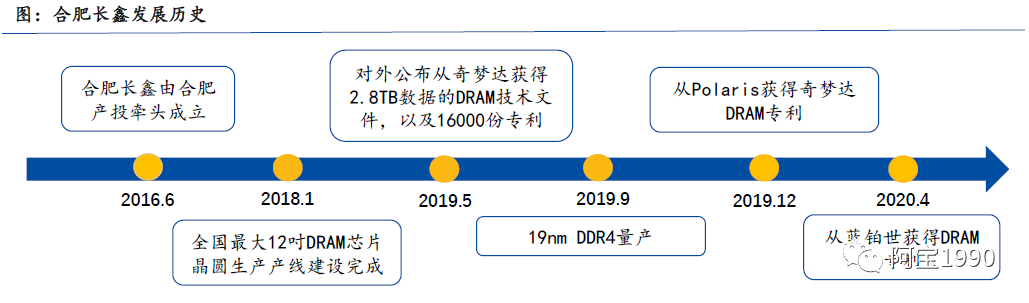

国内目前仅有一家DRAM制造商,合肥长鑫。合肥长鑫由合肥产投在2016年牵头成立,主攻DRAM方向。2017年,兆易创新与合肥产投签署协议,预算180 亿在合肥开展19nm 12 英寸DRAM 项目,兆易创新初始投资36亿,并约定公司在未来收购合肥产投在该项目中的权益,同时约定,合肥长鑫优先为兆易创新代工利基产品(由兆易设计)项目依托的是合肥长鑫旗下春力集成。

长鑫通过合作与协议的方式获取专利避免福建晋华的悲剧。2019 年 5 月,合肥长鑫对外公布,其DRAM 技术来源于奇梦达,通过合作获得了一千多万份与 DRAM 相关的技术文件(约2.8TB 数据) , 以及16000份专利。此后合肥长鑫又与 Polaris Innovations Ltd、蓝铂世签 iT 协议,获得 DRAM 芯片技术文件和专利许可。

5、北京君正 收购矽成重点进入车载DRAM领域

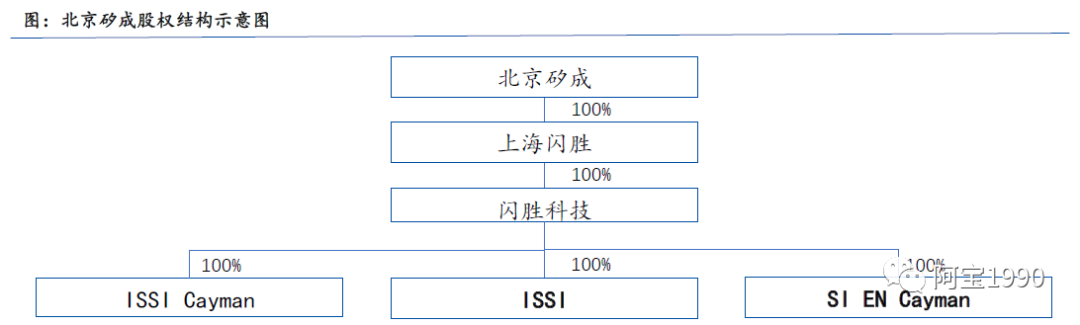

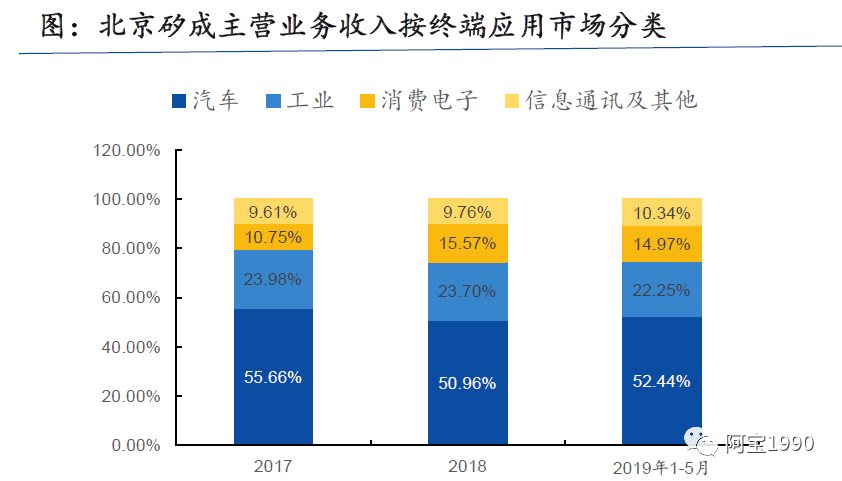

做车载领域,基本上都知道ISSI 这个厂家,无论是NAND FLASH还是DDR 都非常出名,在整个车载领域大名鼎鼎。好消息是现在已经完完全全是一家中国企业控股的企业了。2019年,北京君正公告拟以发行股份,支付现金方式合计72亿元收购北京矽成100%股权结构,并通过证券会审核。下图是整个股权示意图。

与全球存储行业龙头三星电子、美光科技等IDM厂商主要定位于通用型领域不同,ISSI的集成电路芯片产品主要定位于汽车电子、工业及通讯等专用型产品领域,有较高的毛利率以及较稳定的市场需求。随着龙头IDM厂商逐渐增大其在更先进的通用型存储芯片制程工艺的投入,在传统产品和工业级产品的产能上逐渐削减,并逐步放弃了一些小规模的市场。

北京矽成以 Fabless 模式运营,专注于集成电路产品的研发设计,凭借多年的研发积累,其芯片产品性能在极端环境下的可靠性和稳定性均处于行业领先水平,使得其产品在整机客户及汽车客户的产品中更具有市场竞争力,针对车用级客户及工业级客户的高传输速度、高容 量存储芯片可以保持良好的出货量。

4、存储的简单介绍

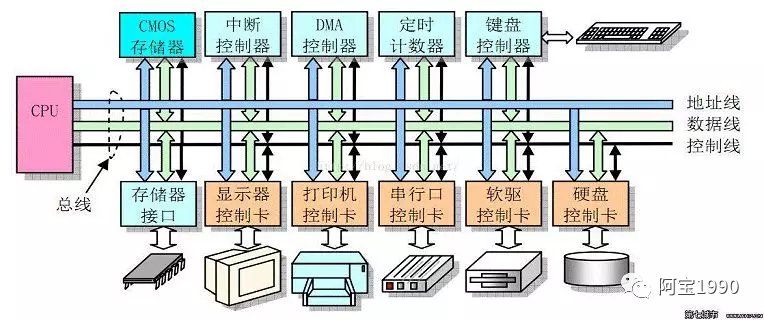

1)内存又称主存,是 CPU 能直接寻址的存储空间,由半导体器件制成

2)内存的特点是存取速率快

内存的作用

1)暂时存放 cpu 的运算数据

2)硬盘等外部存储器交换的数据

3)保障 cpu 计算的稳定性和高性能

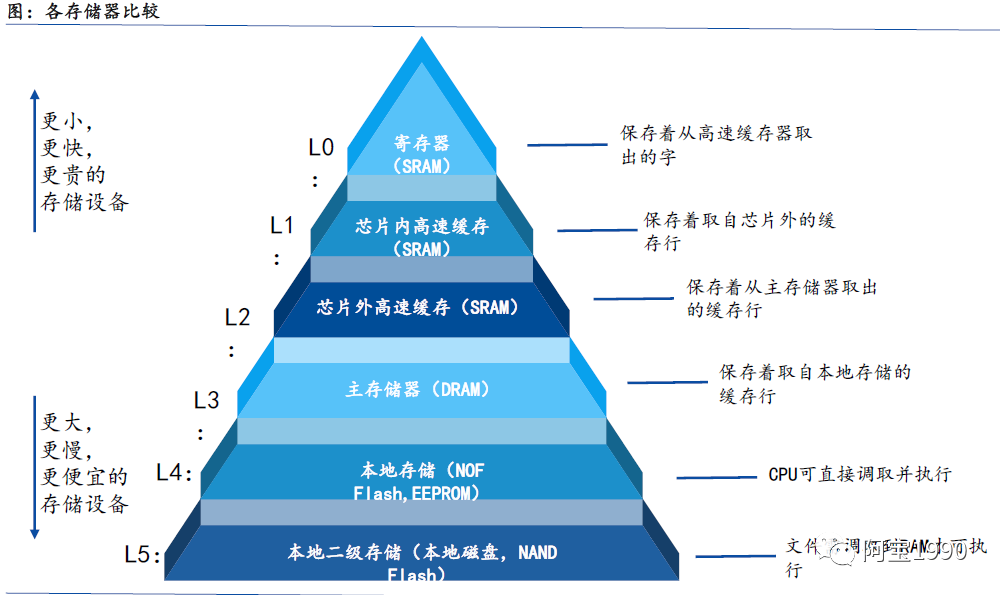

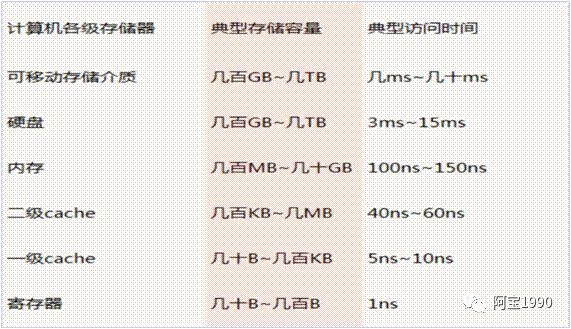

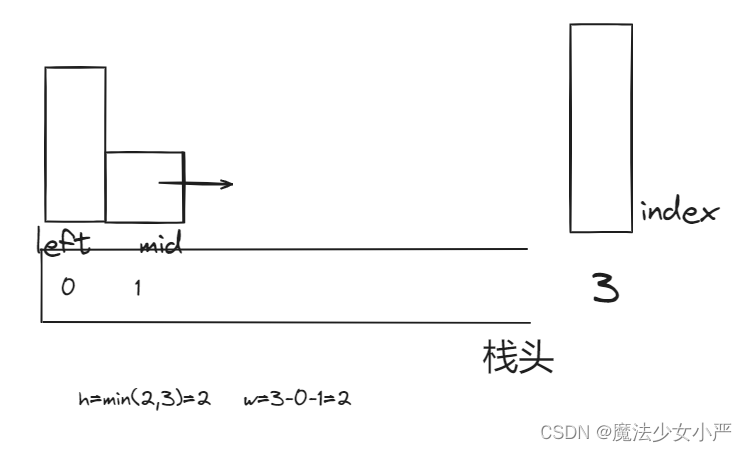

上图非常清楚的看到不用的存储的大小不同,而且速度不同,越上面的存储器容量越小,比如L1和L2 cache这部分容量非常小,但是速度非常快,而且价格比较贵。

往下面的DDR、NOR、NAND、硬盘等等,你会发现容量越来越大,但是通讯速率会更慢,你从一个硬盘里面拷贝资料一般达到50MB/S就谢天谢地了,但是DDR可以达到2133MHZ的速率。同等容量下,越往下面的存储设备的价格也就越便宜。

科普时间到,假设家里室内烟头不小心把垃圾桶着火了,第一时间首先的灭火就是书桌上水杯里的水,然后如果还没有灭到,就是厨房里面盆子里面的水,其次才是家里的水龙头放水,最后是消防局的救援车的水。

虽然消防车的水更多更大,但是远水解不了近火,不可能打一个119电话,我家里的垃圾桶着火了,等消防局的过来,估计家里都烧成空架子了,所以这个时候就需要速度最快的解决方案,虽然杯子里面的水效率最快,此时有80%概率灭掉这个烟头产生的火,如果还不行,此时再用厨房里面盆子的水,虽然这两个装的水不多,但是效率最快。

如果火势非常大,此时就应该是自来水管的水或者消防通道里面的水来解救了,如果这两个都还解救不了,应该就是消防叔叔的消防车的高压水枪的水了。有这这个概念我们再来看看L1和L2 cache的内容。

芯片内部高速缓存介绍:

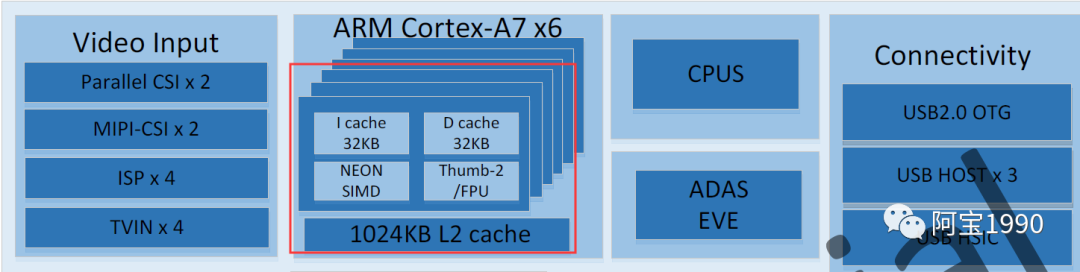

上图是全志T7的芯片内部手册图,可以从很多芯片手册上面看到有I cache和D cache 和L2 cache。这个就是上图中的L1和L2 cache 芯片内部高速缓存。

Cache,是存储器子系统的组成部分,存放着程序经常使用的指令和数据,这就是Cache的传统定义。从广义的角度上看,Cache是快设备为了缓解访问慢设备延时的预留的Buffer,从而可以在掩盖访问延时的同时,尽可能地提高数据传输率。

高速缓冲存储器Cache是位于CPU与内存之间的临时存储器,它的容量比内存小但交换速度快。在Cache中的数据是内存中的一小部分,但这一小部分是短时间内CPU即将访问的,当CPU调用大量数据时,就可避开内存直接从Cache中调用,从而加快读取速度。由此可见,在CPU中加入Cache是一种高效的解决方案,这样整个内存储器(Cache+内存)就变成了既有Cache的高速度,又有内存的大容量的存储系统了。Cache对CPU的性能影响很大,主要是因为CPU的数据交换顺序和CPU与Cache间的带宽引起的。

高速缓存的工作原理

1. 读取顺序

CPU要读取一个数据时,首先从Cache中查找,如果找到就立即读取并送给CPU处理;如果没有找到,就用相对慢的速度从内存中读取并送给CPU处理,同时把这个数据所在的数据块调入Cache中,可以使得以后对整块数据的读取都从Cache中进行,不必再调用内存。

正是这样的读取机制使CPU读取Cache的命中率非常高(大多数CPU可达90%左右),也就是说CPU下一次要读取的数据90%都在Cache中,只有大约10%需要从内存读取。这大大节省了CPU直接读取内存的时间,也使CPU读取数据时基本无需等待。总的来说,CPU读取数据的顺序是先Cache后内存。

2. 缓存分类

前面是把Cache作为一个整体来考虑的,现在要分类分析了。Intel从Pentium开始将Cache分开,通常分为一级高速缓存L1和二级高速缓存L2。

在以往的观念中,L1 Cache是集成在CPU中的,被称为片内Cache。在L1中还分数据Cache(I-Cache)和指令Cache(D-Cache)。它们分别用来存放数据和执行这些数据的指令,而且两个Cache可以同时被CPU访问,减少了竞相争用Cache所造成的冲突,提高了处理器效能。

在P4处理器中使用了一种先进的一级指令Cache——动态跟踪缓存。它直接和执行单元及动态跟踪引擎相连,通过动态跟踪引擎可以很快地找到所执行的指令,并且将指令的顺序存储在追踪缓存里,这样就减少了主执行循环的解码周期,提高了处理器的运算效率。

以前的L2 Cache没集成在CPU中,而在主板上或与CPU集成在同一块电路板上,因此也被称为片外Cache。但从PⅢ开始,由于工艺的提高L2 Cache被集成在CPU内核中,以相同于主频的速度工作,结束了L2 Cache与CPU大差距分频的历史,使L2 Cache与L1 Cache在性能上平等,得到更高的传输速度。L2Cache只存储数据,因此不分数据Cache和指令Cache。在CPU核心不变化的情况下,增加L2 Cache的容量能使性能提升,同一核心的CPU高低端之分往往也是在L2 Cache上做手脚,可见L2 Cache的重要性。现在CPU的L1 Cache与L2 Cache惟一区别在于读取顺序。

3. 读取命中率

CPU在Cache中找到有用的数据被称为命中,当Cache中没有CPU所需的数据时(这时称为未命中),CPU才访问内存。从理论上讲,在一颗拥有2级Cache的CPU中,读取L1 Cache的命中率为80%。也就是说CPU从L1 Cache中找到的有用数据占数据总量的80%,剩下的20%从L2 Cache读取。由于不能准确预测将要执行的数据,读取L2的命中率也在80%左右(从L2读到有用的数据占总数据的16%)。那么还有的数据就不得不从内存调用,但这已经是一个相当小的比例了。在一些高端领域的CPU(像Intel的Itanium)中,我们常听到L3 Cache,它是为读取L2 Cache后未命中的数据设计的—种Cache,在拥有L3 Cache的CPU中,只有约5%的数据需要从内存中调用,这进一步提高了CPU的效率。

为了保证CPU访问时有较高的命中率,Cache中的内容应该按一定的算法替换。一种较常用的算法是“最近最少使用算法”(LRU算法),它是将最近一段时间内最少被访问过的行淘汰出局。因此需要为每行设置一个计数器,LRU算法是把命中行的计数器清零,其他各行计数器加1。当需要替换时淘汰行计数器计数值最大的数据行出局。这是一种高效、科学的算法,其计数器清零过程可以把一些频繁调用后再不需要的数据淘汰出Cache,提高Cache的利用率。

这期先把片内的高速缓存先讲解了,后面几期是E2PROM、NOR FLASH、NAND FLASH、EMMC、DDR的内容。

下面主要介绍的是掉电后依旧能保存程序的器件,FLASH,在我们实际设计的产品中会经常遇到的无非是这几类存储,E2PROM、NOR FLASH、NAND FLASH、EMMC等这几大类,今天机哥就针对这几类在车载上分别有什么应用,注意事项。

5、EEPROM 低功耗、高擦写次数的首选方案

EEPROM 的全称是“电可擦除可编程只读存储器”,可以在电脑上或专用设备上擦除已有信息,重新编程,一般用在即插即用。在一些所需存储容量不大,并且需要频繁更新的场合, EEPROM 相比较于Flash ,由于其百万次的擦写次数和更快速的写入,成为更佳选择。

近年来,EEPROM 除了越来越多的集成到 SOC 芯片中,也可搭配 AMOLED、指纹、触控、摄像头、蓝牙、无线等芯片形成模组。EEPROM 以其通用性,稳定耐用的数据存储,各种小容量规格,能满足摄像头模组、可穿戴设备等对参数存储的要求。

也许你会说,机哥哪里有这么多擦写次数要求的使用场景哦,不会达到百万次啊。机哥给你说说一个场景,车载液晶仪表的总里程数,目前汽车的里程基本上是都是通过液晶仪表仪表的EEPROM里面进行存储,每隔一定的时间,总的里程数就会增加,这个数据就会发生变化,就会往EEPROM里面写入,想想假如1分钟写一次,那么10年就要写5256000次,当然这里不会这么夸张,车辆10年都一直不停歇,同时EEPROM的存储大小也是要写很多次后再进行覆盖擦除,不是每写一次就直接覆盖掉了,这样EEPROM的寿命是无法满足车辆的寿命周期的。

还有就是在娱乐中控导航中,有一些掉电要保持的数据,比较常见的功能就是掉电记忆,比如用户上次的收音节目是哪个频道,这样更用户更好的体验效果,此时就需要使用到一颗EEPROM,每次去保持这个数据,因为每次用户最后关机的状态是不同的,比如这次在听MP3的某首歌,下次再听FM收音某个频道,此时都需要去刷写EEPROM,而且为了防止突然掉电,很多ter1的做法都是固定的时间去存储一下这个用户数据个性化数据进入EEPROM,哪怕是突然掉电,它依旧存储了突然掉电前最近的一次用户操作。

因为EEPROM的容量有限,所以决定了该器件的用途主要是用来存储一些参数,而且是存储一些需要经常擦写的数据。无法存储启动程序等等,因为目前的ARM架构的boot程序都无法放置在EEPROM中。

6、NOR FLASH & NAND FLASH 最佳搭档

吃瓜群众:什么样的搭档才是最佳搭档?

机哥:这样说吧,吃过槟榔的朋友都知道,槟榔的最佳搭档就是香烟,俗话说的好,槟榔加烟,法力无边。

机哥在做机顶盒的时候,很多项目都是NOR FLASH +NAND FLASH的配置,刚开始我也不懂,为什么要这样做,很多情况下都是客户基于高级安全的需求,到底什么样的安全需求要这样一个配置,使用NAND FLASH的存储容量完全够满足程序的要求,无需要NOR FLASH的存在的理由啊,经过深入的理解后我知道了其中的缘由,我先把原因说了,后面我们慢慢说说FLASH的内部架构。

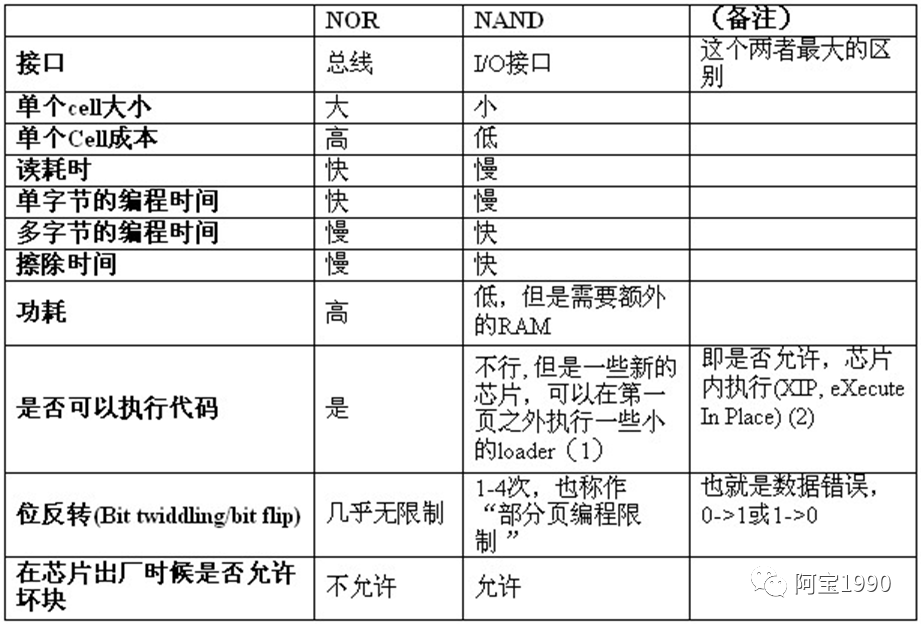

1.nor的成本相对高,具体读写数据时候,不容易出错。总体上,比较适合应用于存储少量的代码。

2.Nand flash相对成本低。使用中数据读写容易出错,所以一般都需要有对应的软件或者硬件的数据校验算法,统称为ECC。由于相对来说,容量大,价格便宜,因此适合用来存储大量的数据。其在嵌入式系统中的作用,相当于PC上的硬盘,用于存储大量数据。

所以,机顶盒常见的应用组合就是,用小容量的Nor Flash存储启动代码,比如uboot,系统启动后,初始化对应的硬件,包括SDRAM等,然后将Nand Flash上的Linux 内核读取到内存中,做好该做的事情后,就跳转到SDRAM中去执行内核了,然后内核解压(如果是压缩内核的话,否则就直接运行了)后,开始运行,在Linux内核启动最后,去Nand Flash上,挂载根文件,比如jffs2,yaffs2等,挂载完成,运行初始化脚本,启动consle交互,才运行你通过console和内核交互。至此完成整个系统启动过程。而Nor Flash存放的是Uboot,Nand Flash存放的是Linux的内核镜像和根文件系统,以及余下的空间分成一个数据区。

1、NAND FLASH的基本介绍

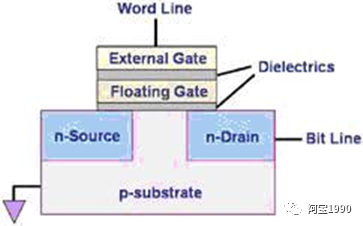

上图是FLASH的存储原理,采用Floating Gate存储数据的技术,存储电荷的多少,取决于图中的外部门(external gate)所被施加的电压,其控制了是向存储单元中冲入电荷还是使其释放电荷。数据的表示,以所存储的电荷的电压是否超过一个特定的阈值Vth来表示。

其实这里就很简单,就是通过一个存储的电荷是否超过阈值Vth来判定高低电平。想想法律怎么判断是否具有完全行为民事行为人,年龄是一个很重要的标志,判断你是否满了18岁。

看到这里,吃瓜群众会问,机哥,这里的存储是不是只有0和1呢,那我们从淘宝上看到有一些TF卡写 SLC、MLC、TLC是什么意思和差别呢。

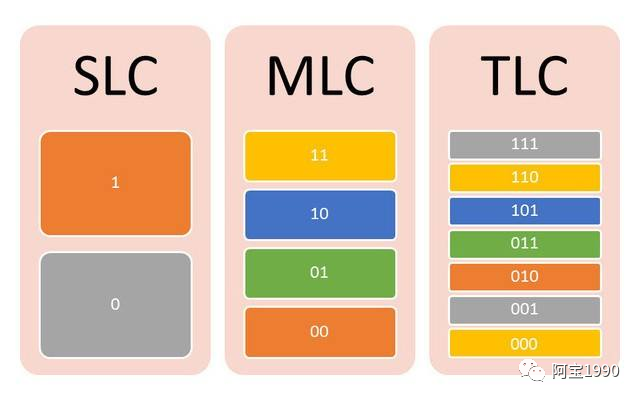

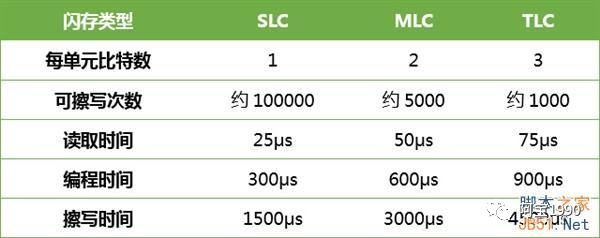

Nand Flash按照内部存储数据单元的电压的不同层次,也就是单个内存单元中,是存储1位数据,还是多位数据,可以分为SLC、MLC、TLC。

1. SLC,Single Level Cell:

单个存储单元,只存储一位数据,表示成1或0.

就是上面介绍的,对于数据的表示,单个存储单元中内部所存储电荷的电压,和某个特定的阈值电压Vth,相比,如果大于此Vth值,就是表示1,反之,小于Vth,就表示0.

对于nand Flash的数据的写入1,就是控制External Gate去充电,使得存储的电荷够多,超过阈值Vth,就表示1了。而对于写入0,就是将其放电,电荷减少到小于Vth,就表示0了。

2. MLC,Multi Level Cell:

与SLC相对应,就是单个存储单元,可以存储多个位,比如2位,4位等。其实现机制,说起来比较简单,就是,通过控制内部电荷的多少,分成多个阈值,通过控制里面的电荷多少,而达到我们所需要的存储成不同的数据。

比如,假设输入电压是Vin=4V(实际没有这样的电压,此处只是为了举例方便),那么,可以设计出2的2次方=4个阈值,1/4的Vin=1V,2/4的Vin=2V,3/4的Vin=3V,Vin=4V,分别表示2位数据00,01,10,11,对于写入数据,就是充电,通过控制内部的电荷的多少,对应表示不同的数据。

对于读取,则是通过对应的内部的电流(与Vth成反比),然后通过一系列解码电路完成读取,解析出所存储的数据。这些具体的物理实现,都是有足够精确的设备和技术,才能实现精确的数据写入和读出的。

同理TLC也是一样的道理,只是单个存储单元可以存储3位数据的,称作2的3次方=8 Level Cell。

这个其实可以这样简单理解一下,SLC好比把你的学费给你分为两笔,一笔是18岁以前,一笔是18岁以后,每次都是10W元,那么你可以拿到20WRMB,MLC就分的更精细一些,小学、初中、高中、大学四个阶段来划分,每个阶段依旧是10WRMB,那么你可以拿到40WRMB。想想你自己就是一个存储器件,拿到的钱越多,代表存储的数据也就更多。当然一个人的表现差距不大,如果是一个班级,一个学校,那么总的汇总差距就大了去了。

那既然这样,为什么还要造SLC的FLASH呢,TLC存储容量大这么多,其实你想想FLASH的擦写寿命也就是在于无法充满电的风险,因为放电其实很容易,如果你等级划分的越多,越容易导致某个层级电压无法精细化满足,寿命也就没有那么久,而且读取的时间也会变长。

2、NAND FLASH的物理架构层分析

在讲解NAND FLASH的架构之前,我们先来看看图书馆。大家都去过图书馆吧,去图书馆找书一般是怎么找,先去不同的楼层,因为不同的楼层的书籍大概范围是不同的,哲学,化学、人文、小说都分布在不同的楼层,然后在根据书架上的分类,有的还是按年代,有的是按国籍进行的分类,然后再书架上找对应的书。

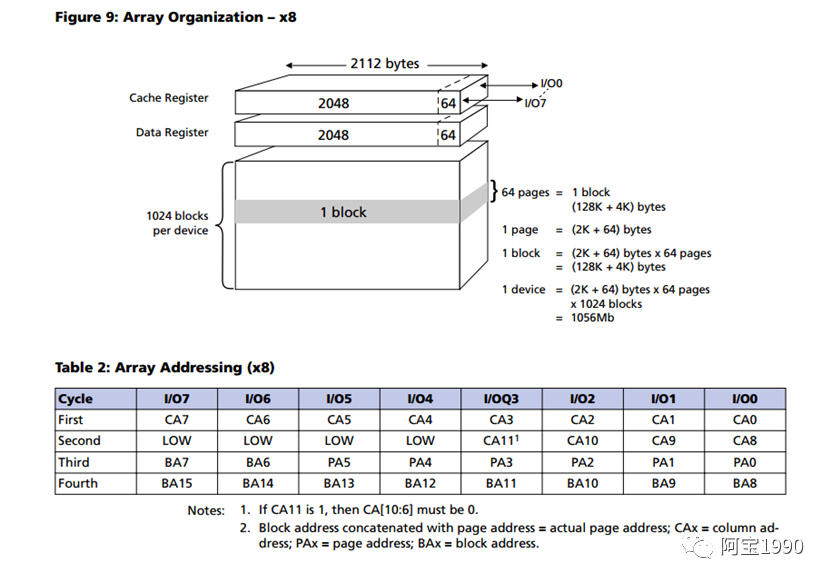

上图是我们公司常用的镁光 NAND FLASH MT29F1G08ABAEAH4:E的datasheet中的描述。

我们结合上面图书馆的书进行一下有趣而且比较容易理解的解释:

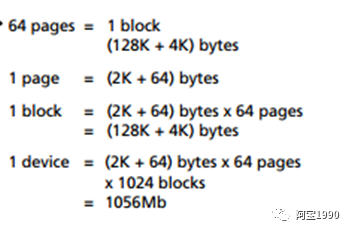

一个FLASH可以理解为一个图书馆,我们看图书馆的藏书有多少(假定都藏书都是红楼梦和西游记,代表数据的0和1),藏书越多多就代表这个FLASH的容量也大,每一本书代表着一个Byte数据的容量大小。

1.一个nand flash由很多个块(Block)组成,这里的block对应的图书馆就是有多少层楼,你想想层数越多,藏书肯定也就越多,这里的镁光NAND FLASH有1024个Block,意味着这个图书馆有1024层,四川话来说:楼层确实有点高,帽儿都望掉了。

2.每个块里面又包含了很多页(page)。这里就相当于图书馆一个楼层有多少个房间,这里的镁光Flash 一个block有64 页,也就是一个楼层有64个房间。

3.每一页的数据大小就相当于有多少一个房间里面有多少本书,这里看到镁光的规格书写的是1page=(2K+64)byte。

大家都去过图书馆看到过小书架吧,在3个大的书架前面会有一个小书架,用来放置一些找不到归还位置的书,等工作人员进行后续整理归还。

每一个页,对应还有一块区域,叫做空闲区域(spare area)/冗余区域(redundant area),而Linux系统中,一般叫做OOB(Out Of Band),这个区域,是最初基于Nand Flash的硬件特性:数据在读写时候相对容易错误,所以为了保证数据的正确性,必须要有对应的检测和纠错机制,此机制被叫做EDC(Error Detection Code)/ECC(Error Code Correction,或者Error Checking and Correcting),所以设计了多余的区域,用于放置数据的校验值。

这里的多余的数据是ECC数据,专门NAND FLASH是用做来校验正常数据的,因为FLASH的特性决定了数据容易造成翻转,本来这个位置写进去的是1,External Gate不小心进行了放电,此时读出来的是0了,此时就需要有纠正措施,后面有机会专门来介绍这个ECC校验的原理。

硬件一般支持的是512字节数据,对应有16字节用来存放校验产生的ECC数值,而这512字节一般叫做一个扇区。对于2K+64字节大小的页来说,按照512字节分,分别叫做A,B,C,D区,而后面的64字节的oob区域,按照16字节一个区,分别叫做E,F,G,H区,对应存放A,B,C,D数据区的ECC的值。所以规格书中经常会看到以下的信息,就知道后面的是OOB区域。

这里就用图书馆的理解就是,每一个房间有4个大书架,每个大书架有512本书就会后面放一个小书架,小书架可以放置16本登记本(这个本子用来登记这512本书的,防止书出现错误),这样算下来一个房间有2048本有用的书,同时有64个登记本。

在一个块内,对每一个页进行编程的话,必须是顺序的,而不能是随机的。比如,一个块中有128个页,那么你只能先对page0编程,再对page1编程,。。。。,而不能随机的,比如先对page3,再page1,page2.,page0,page4,.。。。

3、NAND FLASH的一些读写特点

刚刚说了,咱们这个图书馆有1024层楼,每层楼有64个房间,每个房间有2048本有用的书,还有64本用来记账校验的书。

这个图书馆的的馆长是一个老头,记性不太好,如果你要借第950层中第2个房间中的第10本书,馆长肯定不记得是红楼梦(代表数据0)还是西游记了(代表数据1)。

此时馆长就会给你这样操作,你直接把950层的第2个房间的书全部打包都借给你,你自己拿回去看第10本是什么书,虽然你很不情愿,但是没有办法,要知道这个房间里面的第几本书是什么,就必须全部房间里面的书都借出来。

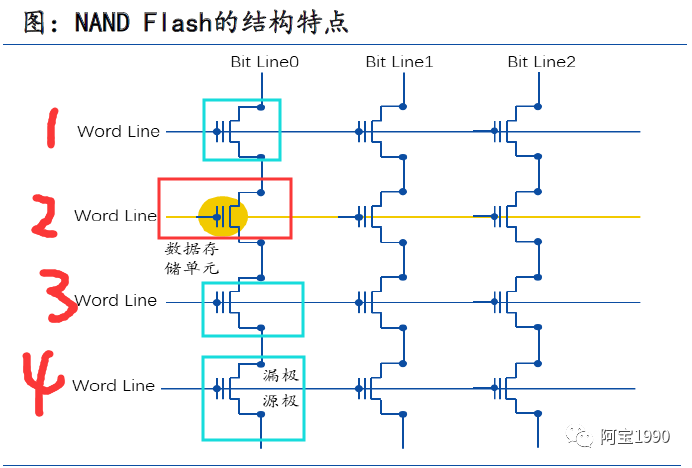

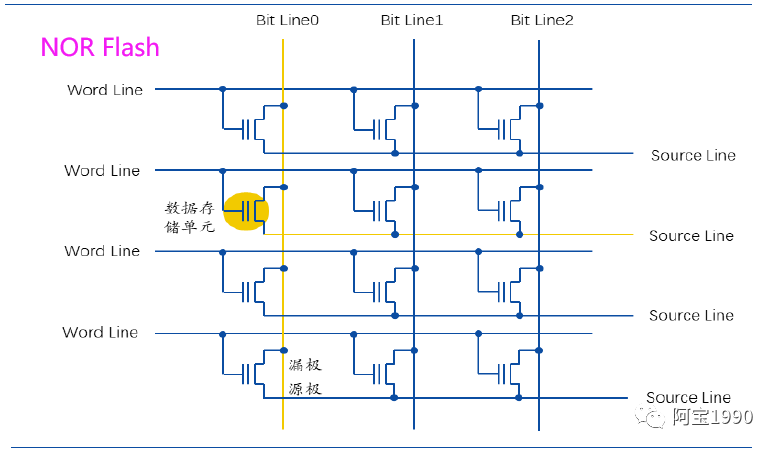

还记得咱们说过一个房间里面有4个书架,每个书架有512本书,若要知道读取第二个书架上的第一本书是什么内容,上图的架构就是NAND Flash的电气连接方式。NAND Flash 的连接方式为串联,若要读取上图黄色 Word Line (字线)的数据,需对其他所有 Word Line 进行增加电压,加压后漏极和源极处于导通状态,也就是要知道上图红色方框中的数据,需要把蓝色方框的数据都导通才行。因此 NAND Flash读取数据的最小单位是页(即Word Line 上的所有数据),无法直接运行程序,所有数据必须先读取到 ARM 上后才可运行。

我们再来看看其他存储设备的读取的特点,N0R Flash 的连接方式为串联,读取数据不需对 Word Line 进行加压,直接测量对应的 Bit Line 和 Source Line 之间的通断即可获取该存储单元的数据。不仅实现了位读取,还大大提高了数据读取的速度。实现位读取,程序便可在 NOR Flash 上运行,即所谓的芯片内执行(XIP)。

为什么NAND FLASH不能XIP片内执行

1、 理论上是可以的,而且也是有人验证过可以的,只不过由于nand flash的物理特性,不能完全保证所读取的数据/代码是正确的,实际上,很少这么用而已。因为,如果真是要用到nand flash做XIP,那么除了读出速度慢之外,还要保证有数据的校验,以保证读出来的,将要执行的代码/数据,是正确的。否则,系统很容易就跑飞了。

2、 NAND FLASH每次读取出来的数据都是以页为单位,你想想,老师要你背诵语文书中的课本,每次你都直接丢给老师一本书,背诵的是目录,这个怎么可以直接算背诵呢。

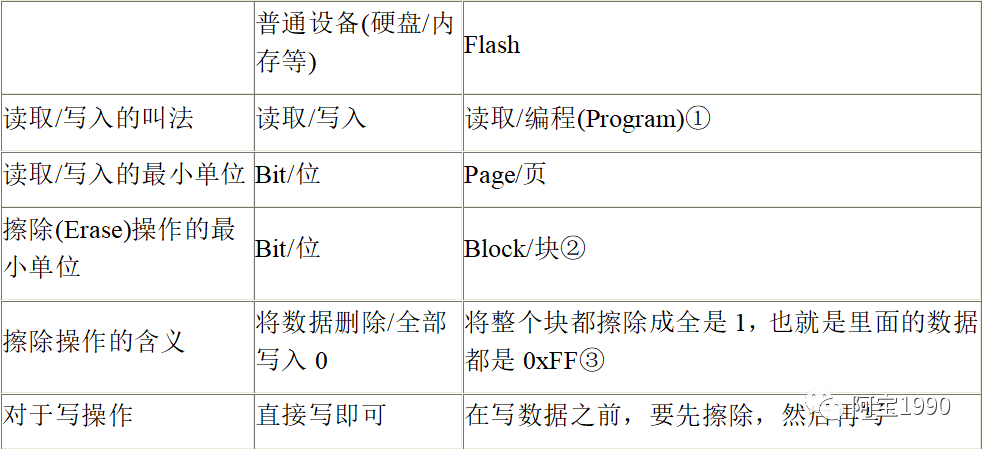

咱们前面说了读数据,有人说写数据就简单了吧,就跟下五子棋一样,下黑棋还是白棋都只要往里填就行,不就是搭积木,往对应的位置写0或者1就行了吧,这个对于NOR Flash或者硬盘等操作,确实是这样的一个操作。NAND FLASH还稍微有一些特殊。

Flash的擦除操作是以block块为单位的,与此相对应的是其他很多存储设备,是以bit位为最小读取/写入的单位,Flash是一次性地擦除整个块:在发送一个擦除命令后,一次性地将一个block,常见的块的大小是128KB/256KB。。,全部擦除为1,也就是里面的内容全部都是0xFF了,由于是一下子就擦除了,相对来说,擦除用的时间很短,可以用一闪而过来形容,所以,叫做Flash Memory。中文有的翻译为(快速)闪存。

这里可以理解为某一天要进行图书馆的第10楼的第二个房间进行编程,也就是装修,此时图书馆馆长就命令人把10楼的书全部更换为西游记(全部擦除为1),然后要编程的时候,就把要从1变为0的地方更换为红楼梦而已,这样速度就非常快。

吃瓜群众:机哥,按照你的意思,那NAND FLASH编程是1变为0咯,那是不是也可以从0变为1呢?

NAND FLASH的编程是1变为0,物理上来说,是可以实现每一位的从0变成1的,但是实际上,对于实际的物理实现,出于效率的考虑,如果对于每一个存储单元都能单独控制,即0变成1,就是对每一个存储单元单独去充电,所需要的硬件实现就很复杂和昂贵,同时所进行对块擦除的操作,也就无法实现之前的,一闪而过的速度了,也就失去了Flash的众多特性了。在写数据之前,要先擦除,内部就都变成0xFF了,然后才能写入数据,也就是将对应位由1变成0。

可以看到NAND Flash和普通存储设备在读写方面操作是有一些比较大的区别,主要是读写的最小单位,擦除的最小单位,最重要的一点就是NAND Flash在写数据之前,一定要先擦除,然后才能写。

7、使用nand scrub命令的工程师要注意了

Nand Flash中,一个块中含有1个或多个位是坏的,就成为其为坏块。坏块的稳定性是无法保证的,也就是说,不能保证你写入的数据是对的,或者写入对了,读出来也不一定对的。而正常的块,肯定是写入读出都是正常的。

其实就相当于图书馆的某个楼层出现了问题,这个楼层就不能进行图书的保存,正常情况下也有两种情况下出现问题,一种是图书馆修好的时候就知道是坏的楼层,此时交付的时候就标记好,这个楼层在后面使用的过程中就不放置图书,还有一种情况下就是使用的过程中年久失修导致损坏,这个时候常见的做法就是把这个楼层的书搬离到还没有使用好的楼层里面去,同时把这个楼层标记为不能使用的楼层。

同理NAND Flash的坏块也有两种:

(1)一种是出厂的时候,也就是,你买到的新的,还没用过的Nand Flash,就可以包含了坏块。此类出厂时就有的坏块,被称作factory (masked)bad block或initial bad/invalid block,在出厂之前,就会做对应的标记,标为坏块。

具体标记的地方是,对于现在常见的页大小为2K的Nand Flash,是块中第一个页的oob起始位置的第1个字节(旧的小页面,pagesize是512B甚至256B的nand flash,坏块标记是第6个字节),如果不是0xFF,就说明是坏块。相对应的是,所有正常的块,好的块,里面所有数据都是0xFF的。

(2)第二类叫做在使用过程中产生的,由于使用过程时间长了,在擦块除的时候,出错了,说明此块坏了,也要在程序运行过程中,发现,并且标记成坏块的。具体标记的位置,和上面一样。这类块叫做worn-out bad block。

对于坏块的管理,在Linux系统中,叫做坏块管理(BBM,Bad Block Managment),对应的会有一个表去记录好块,坏块的信息,以及坏块是出厂就有的,还是后来使用产生的,这个表叫做 坏块表(BBT,Bad Block Table)。在Linux内核MTD架构下的Nand Flash驱动,和Uboot中Nand Flash驱动中,在加载完驱动之后,如果你没有加入参数主动要求跳过坏块扫描的话,那么都会去主动扫描坏块,建立必要的BBT的,以备后面坏块管理所使用。

而关于好块和坏块,Nand Flash在出厂的时候,会做出保证:

1.关于好的,可以使用的块的数目达到一定的数目,比如三星的K9G8G08U0M,整个flash一共有4096个块,出厂的时候,保证好的块至少大于3996个,也就是意思是,你新买到这个型号的nand flash,最坏的可能,有3096-3996=100个坏块。不过,事实上,现在出厂时的坏块,比较少,绝大多数,都是使用时间长了,在使用过程中出现的。

2.保证第一个块是好的,并且一般相对来说比较耐用。做此保证的主要原因是,很多Nand Flash坏块管理方法中,就是将第一个块,用来存储上面提到的BBT,否则,都是出错几率一样的块,那么也就不太好管理了,连放BBT的地方,都不好找了。而且如果只使用了NAND Flash没有配合NOR Flash的系统,uboot都是放到第一个块中,如果这个块损坏了,根本无法保障机器能够开机。像一些amlogic平台为了保险起见,就会把uboot拷贝在前面几个block中,当block 0无法启动的时候,该主芯片还支持从blcok 1启动,这个需要CPU内置程序代码才行。

就好比图书馆,你要去其他楼层,第一楼层得保障是好的吧,否则都没有办法乘坐电梯去其他楼层去了,是一个道理。

一般来说,不同型号的Nand Flash的数据手册中,也会提到,自己的这个nand flash,最多允许多少个坏块。就比如上面提到的,镁光 NAND FLASH MT29F1G08ABAEAH4,最多有100个坏块。

对于坏块的标记,本质上,也只是对应的flash上的某些字节的数据是非0xFF而已,所以,只要是数据,就是可以读取和写入的。也就意味着,可以写入其他值,也就把这个坏块标记信息破坏了。对于出厂时的坏块,一般是不建议将标记好的信息擦除掉的。

uboot中有个命令是“nand scrub”就可以将块中所有的内容都擦除了,包括坏块标记,不论是出厂时的,还是后来使用过程中出现而新标记的。一般来说,不建议用这个。最好用“nand erase”只擦除好的块,对于已经标记坏块的块,不擦除。

8、Nand Flash中的特殊硬件结构

由于nand flash相对其他常见设备来说,比较特殊,所以,特殊的设备,也有特殊的设计,所以,有些特殊的硬件特性,就有必要解释一下:

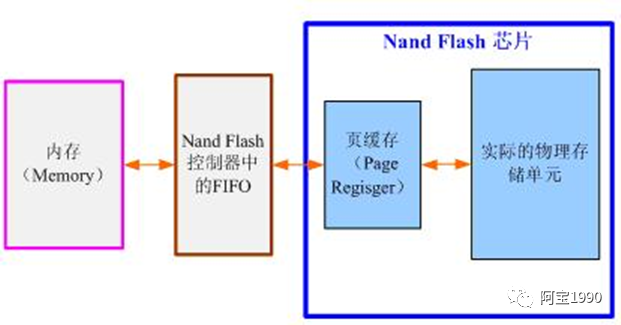

页寄存器(Page Register):由于Nand Flash读取和编程操作来说,最小单位是页,所以nand flash在硬件设计时候,就考虑到这一特性,对于每一片,都有一个对应的区域,专门用于存放,将要写入到物理存储单元中去的或者刚从存储单元中读取出来的,一页的数据,这个数据缓存区,本质上就是一个buffer,但是只是名字叫法不同,datasheet里面叫做Page Register,此处翻译为页寄存器,实际理解为页缓存,更为恰当些。

只有写到了这个页缓存中,只有等你发了对应的编程第二阶段的确认命令0x10之后,实际的编程动作才开始,才开始把页缓存中的数据,一点点写到物理存储单元中去。

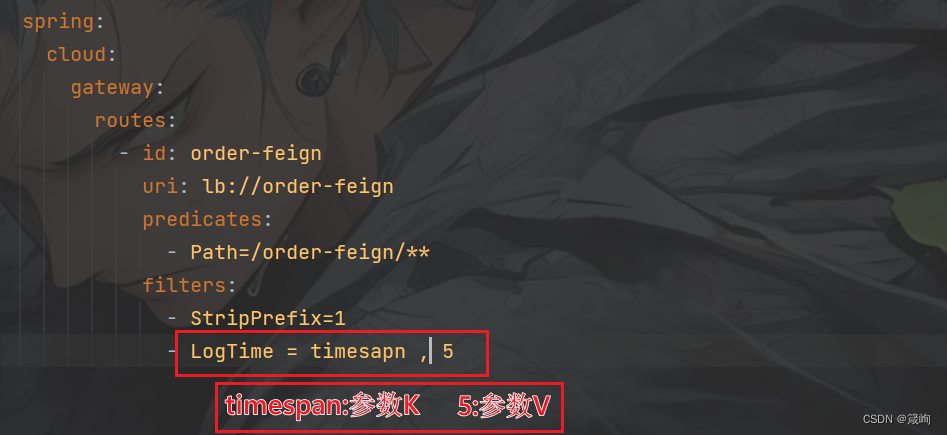

上期内容我们重点说了NAND FLASH本身的一些特殊性,比如写之前要进行擦除,而且存在坏块的可能性性,所以很多车厂在评估NAND FLASH的时候,会评估目前容量的冗余量是多少,要保障有足够多的空间去预防坏块的产生后的数据搬移。

这期内容重点说说NAND FLASH的一些操作特性,怎么进行控制和读取的。这期的内容有点硬核,需要有一些专业知识的人进行阅读,科普类的文章咱们下期继续。

9、NAND FLASH的硬件特性介绍

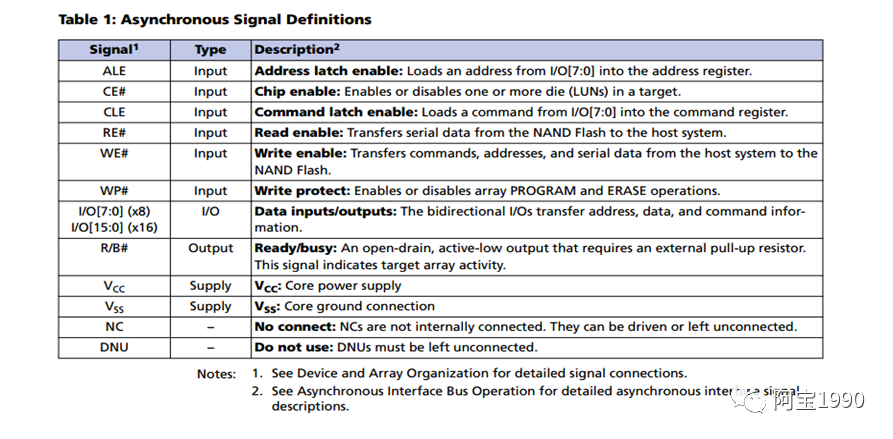

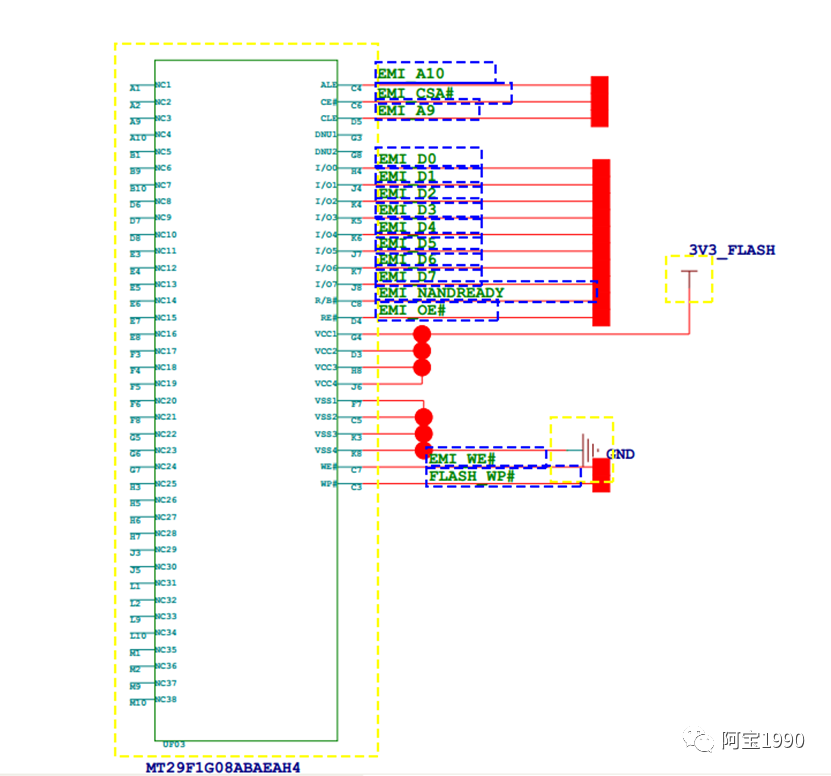

上图是镁光 NAND FLASH MT29F1G08ABAEAH4的引脚(Pin)所对应的功能,简单翻译如下:

1. I/O0 ~ I/O7:用于输入地址/数据/命令,输出数据

2. CLE:Command Latch Enable,命令锁存使能,在输入命令之前,要先在模式寄存器中,设置CLE使能

3. ALE:Address Latch Enable,地址锁存使能,在输入地址之前,要先在模式寄存器中,设置ALE使能

4. CE#:Chip Enable,芯片使能,在操作Nand Flash之前,要先选中此芯片,才能操作

5. RE#:Read Enable,读使能,在读取数据之前,要先使CE#有效。

6. WE#:Write Enable,写使能,在写取数据之前,要先使WE#有效。

7. WP#:Write Protect,写保护

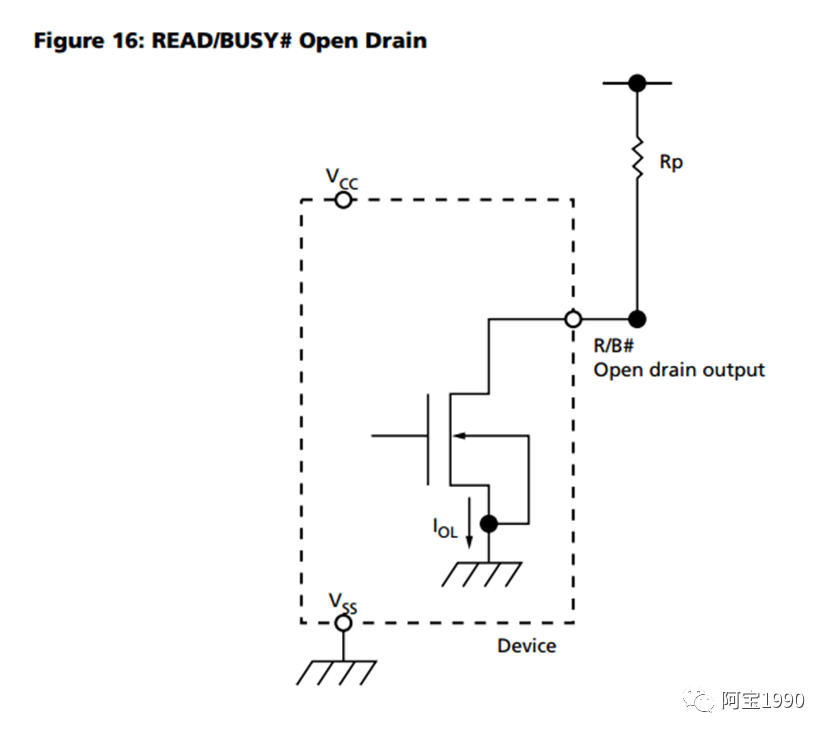

8. R/B#:Ready/Busy Output,就绪/忙,主要用于在发送完编程/擦除命令后,检测这些操作是否完成,忙,表示编程/擦除操作仍在进行中,就绪表示操作完成.

9. Vcc:Power,电源

10. Vss:Ground,接地

11. N.C:Non-Connection,未定义,未连接。

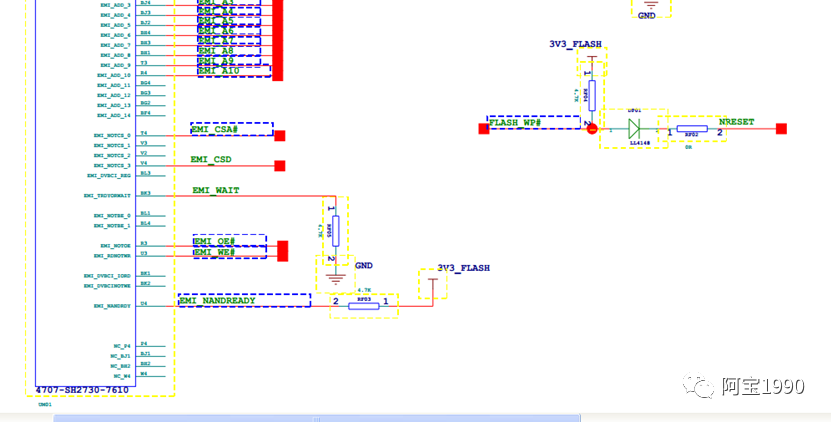

实际项目的NAND FLASH原理图

上图中我们可以发现有两个地方需要上拉电阻R/B#:、WP#,其他都是CPU同nand flash直接相连接。通过查询flash 的datasheet可以发现,这两个引脚是开漏极输出,需要上拉电阻。

而且可以看到电路设计中WP#引脚一端接上拉电阻,一端通过二极管和0欧姆电阻连接到CPU复位引脚,CPU主芯片平台的复位是低电平复位,WP#引脚是低电平的时候写保护有效,这样做的目的就是,在复位期间,即CPU复位引脚为低电平期间此时WP#引脚也为二极管电压(0.7V)为低电平,为写保护状态,在复位期间,CPU引脚状态不定,容易对flash进行误操作。这样做的目的就是硬件实现在CPU复位期间,flash是写保护状态,不允许写入的。

很多时候掉电产生的擦除数据,导致数据丢失无法开机、无法保存掉电记忆等等问题都可以使用这个方案来对策解决问题。

为何需要ALE和CLE

比如命令锁存使能(Command Latch Enable,CLE)和地址锁存使能(Address Latch Enable,ALE),那是因为,Nand Flash就8个I/O,而且是复用的,也就是,可以传数据,也可以传地址,也可以传命令,为了区分你当前传入的到底是啥,所以,先要用发一个CLE(或ALE)命令,告诉nand Flash的控制器一声,我下面要传的是命令(或地址),这样,里面才能根据传入的内容,进行对应的动作。否则,nand flash内部,怎么知道你传入的是数据,还是地址,还是命令啊,也就无法实现正确的操作了。

Nand Flash只有8个I/O引脚的好处

1. 减少外围引脚:相对于并口(Parellel)的Nor Flash的48或52个引脚来说,的确是大大减小了引脚数目,这样封装后的芯片体积,就小很多。现在芯片在向体积更小,功能更强,功耗更低发展,减小芯片体积,就是很大的优势。同时,减少芯片接口,也意味着使用此芯片的相关的外围电路会更简化,避免了繁琐的硬件连线。

2. 提高系统的可扩展性,因为没有像其他设备一样用物理大小对应的完全数目的addr引脚,在芯片内部换了芯片的大小等的改动,对于用全部的地址addr的引脚,那么就会引起这些引脚数目的增加,比如容量扩大一倍,地址空间/寻址空间扩大一倍,所以,地址线数目/addr引脚数目,就要多加一个,而对于统一用8个I/O的引脚的Nand Flash,由于对外提供的都是统一的8个引脚,内部的芯片大小的变化或者其他的变化,对于外部使用者(比如编写nand flash驱动的人)来说,不需要关心,只是保证新的芯片,还是遵循同样的接口,同样的时序,同样的命令,就可以了。这样就提高了系统的扩展性。

片选无关(CE don’t-care)技术

Nand flash支持一个叫做CE don’t-care的技术,字面意思就是,不关心是否片选,那有人会问了,

如果不片选,那还能对其操作吗?答案就是,这个技术,主要用在当时是不需要选中芯片却还可以继续操作的这些情况:在某些应用,比如录音,音频播放等应用中,外部使用的微秒(us)级的时钟周期,此处假设是比较少的2us,在进行读取一页或者对页编程时,是对Nand Flash操作,这样的串行(Serial Access)访问的周期都是20/30/50ns,都是纳秒(ns)级的,此处假设是50ns,当你已经发了对应的读或写的命令之后,接下来只是需要Nand Flash内部去自己操作,将数据读取除了或写入进去到内部的数据寄存器中而已,此处,如果可以把片选取消,CE#是低电平有效,取消片选就是拉高电平,这样会在下一个外部命令发送过来之前,即微秒量级的时间里面,即2us-50ns≈2us,这段时间的取消片选,可以降低很少的系统功耗,但是多次的操作,就可以在很大程度上降低整体的功耗了。

总结起来简单解释就是:由于某些外部应用的频率比较低,而Nand Flash内部操作速度比较快,所以具体读写操作的大部分时间里面,都是在等待外部命令的输入,同时却选中芯片,产生了多余的功耗,此“不关心片选”技术,就是在Nand Flash的内部的相对快速的操作(读或写)完成之后,就取消片选,以节省系统功耗。待下次外部命令/数据/地址输入来的时候,再选中芯片,即可正常继续操作了。这样,整体上,就可以大大降低系统功耗了。

10、NAND FLASH 的读操作详细解读

以最简单的read操作为例,解释如何理解时序图,以及将时序图中的要求,转化为代码。解释时序图之前,让我们先要搞清楚,我们要做的事情:那就是,要从nand flash的某个页里面,读取我们要的数据。要实现此功能,会涉及到几部分的知识,至少很容易想到的就是:需要用到哪些命令,怎么发这些命令,怎么计算所需要的地址,怎么读取我们要的数据等等。

就好比你去图书馆借书,想想是一个什么样的流程,首先得告诉馆长你要要借书还是还书、然后把要借书的位置告诉馆长,最后是把图书卡或者借书证件给馆长,此时就耐心等待要借的书籍了。

下面,就一步步的解释,需要做什么,以及如何去做:

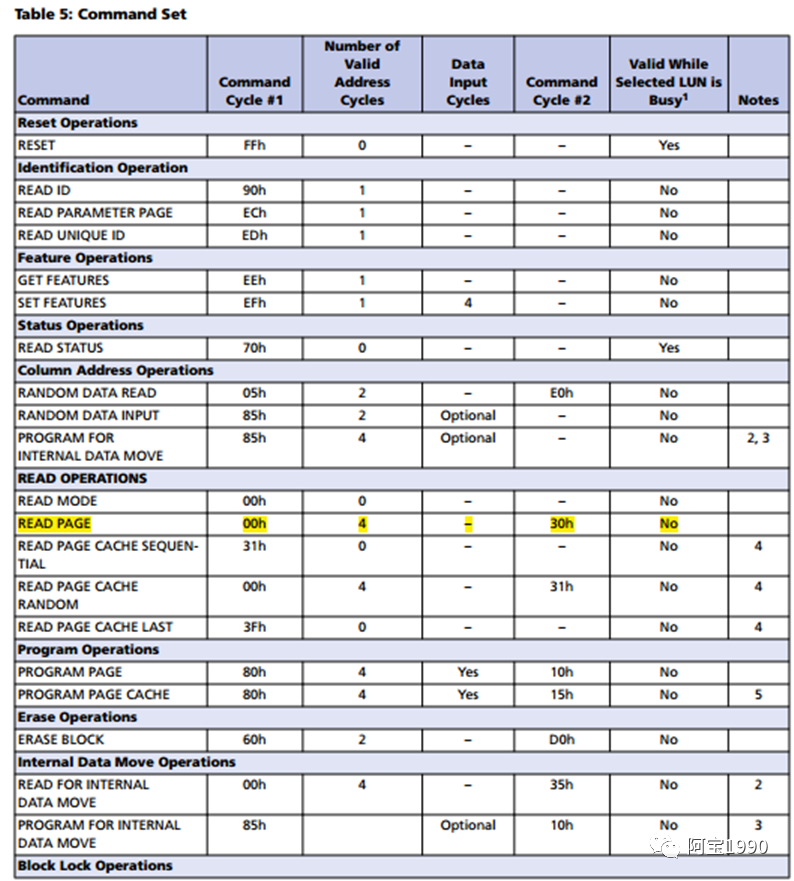

1.需要使用何种命令

首先,是要了解,对于读取数据,要用什么命令。

下面是datasheet中的命令集合:

很容易看出,我们要读取数据,要用到Read命令,该命令需要2个周期,第一个周期发0x00,第二个周期发0x30。

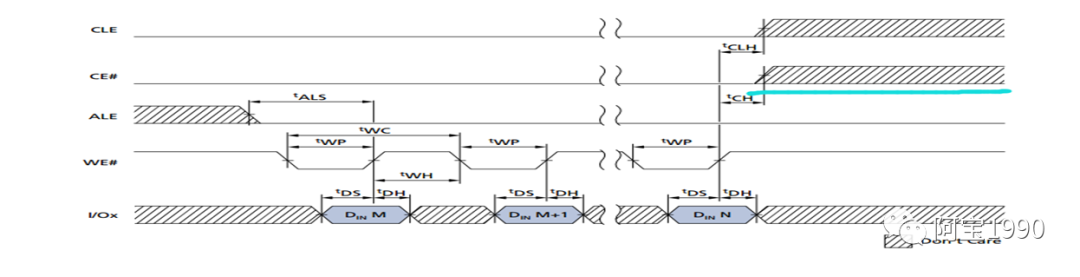

2.发送命令前的准备工作以及时序图各个信号的具体含义

知道了用何命令后,再去了解如何发送这些命令。

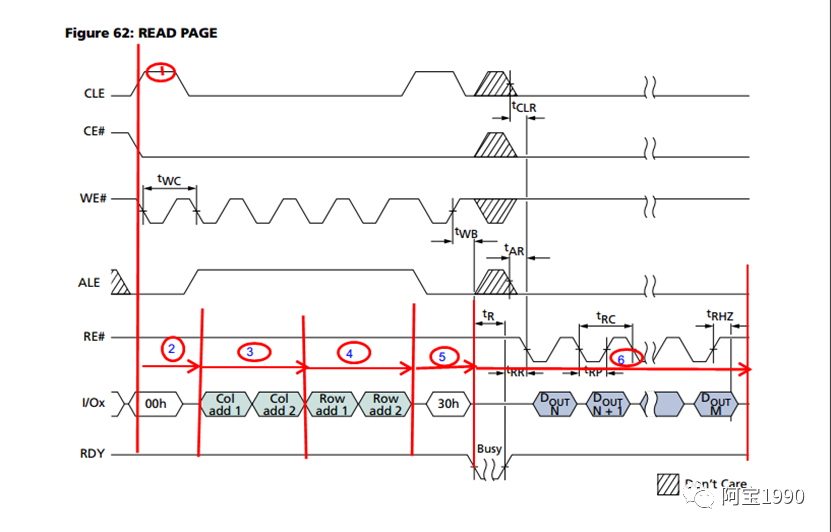

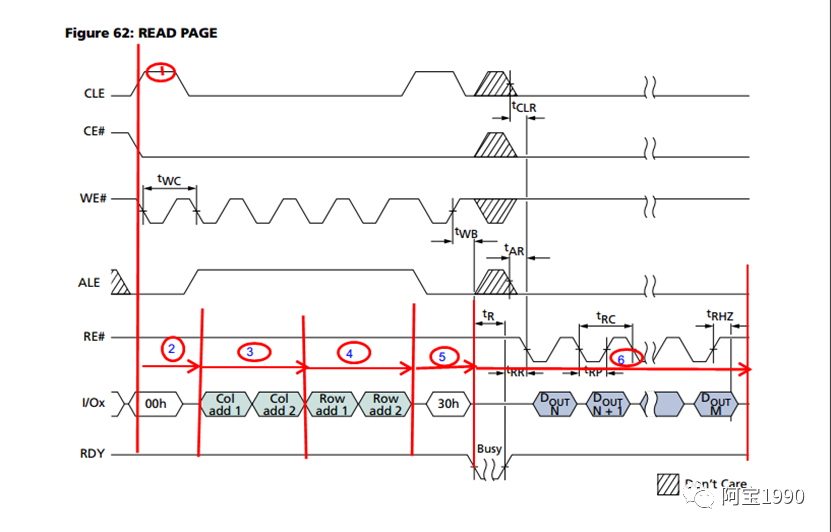

Nand Flash数据读取操作的时序图

注:此图来自镁光的型号MT29F1G08ABAEAH4:E的nand flash的数据手册(datasheet)。

我们来一起看看,我在图中的特意标注的①边上的红色竖线。

红色竖线所处的时刻,是在发送读操作的第一个周期的命令0x00之前的那一刻。让我们看看,在那一刻,其所穿过好几行都对应什么值,以及进一步理解,为何要那个值。

(1)红色竖线穿过的第一行,是CLE。还记得前面介绍命令所存使能(CLE)那个引脚吧?CLE,将CLE置1,就说明你将要通过I/O复用端口发送进入Nand Flash的,是命令,而不是地址或者其他类型的数据。只有这样将CLE置1,使其有效,才能去通知了内部硬件逻辑,你接下来将收到的是命令,内部硬件逻辑,才会将受到的命令,放到命令寄存器中,才能实现后面正确的操作,否则,不去将CLE置1使其有效,硬件会无所适从,不知道你传入的到底是数据还是命令了。

(2)而第二行,是CE#,那一刻的值是0。这个道理很简单,你既然要向Nand Flash发命令,那么先要选中它,所以,要保证CE#为低电平,使其有效,也就是片选有效。

(3)第三行是WE#,意思是写使能。因为接下来是往nand Flash里面写命令,所以,要使得WE#有效,所以设为低电平。

(4)第四行,是ALE是低电平,而ALE是高电平有效,此时意思就是使其无效。而对应地,前面介绍的,使CLE有效,因为将要数据的是命令,而不是地址。如果在其他某些场合,比如接下来的要输入地址的时候,就要使其有效,而使CLE无效了。

(5)第五行,RE#,此时是高电平,无效。可以看到,知道后面低6阶段,才变成低电平,才有效,因为那时候,要发生读取命令,去读取数据。

(6)第六行,就是我们重点要介绍的,复用的输入输出I/O端口了,此刻,还没有输入数据,接下来,在不同的阶段,会输入或输出不同的数据/地址。

(7)第七行,R/B#,高电平,表示R(Ready)/就绪,因为到了后面的第5阶段,硬件内部,在第四阶段,接受了外界的读取命令后,把该页的数据一点点送到页寄存器中,这段时间,属于系统在忙着干活,属于忙的阶段,所以,R/B#才变成低,表示Busy忙的状态的。

介绍了时刻①的各个信号的值,以及为何是这个值之后,相信,后面的各个时刻,对应的不同信号的各个值,大家就会自己慢慢分析了,也就容易理解具体的操作顺序和原理了。

3.如何计算出,我们要传入的地址

在介绍具体读取数据的详细流程之前,还要做一件事,那就是,先要搞懂我们要访问的地址,以及这些地址,如何分解后,一点点传入进去,使得硬件能识别才行。

此处还是以MT29F1G08ABAEAH4:E为例,此nand flash,一共有1024个块,每个块内有64页,每个页是2K+64 Bytes,假设,我们要访问其中的第1000个块中的第25页中的1208字节处的地址,此时,我们就要先把具体的地址算出来:

物理地址=块大小×块号+页大小×页号+页内地址=1000×128K+2K×25+1208=0x7D0CCB8,接下来,我们就看看,怎么才能把这个实际的物理地址,转化为nand Flash所要求的格式。

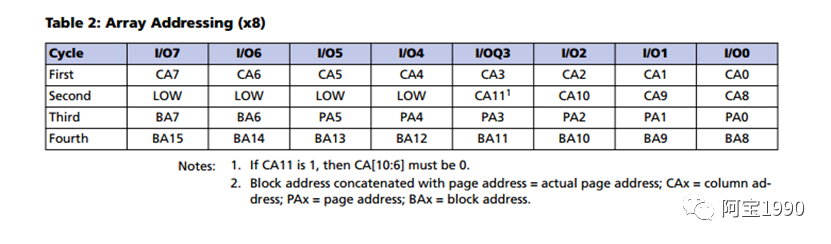

在解释地址组成之前,先要来看看其datasheet中关于地址周期的介绍:

图 Nand Flash的地址周期组成

结合时序图的2,3阶段,我们可以看出,此nand flash地址周期共有4个,2个列(Column)周期,2个行(Row)周期。

而对于对应的,我们可以看出,实际上,列地址CA0~CA10,就是页内地址,11位地址范围是从0到2047,即2K,而多出的A11,理论上可以表示2048~4095,但是实际上,上述规格书中说明当CA11为1时,CA【10:6】都必须为0,所以我们最多也只用到了2048~2112,用于表示页内的oob区域,其大小是64字节。

PA0~PA5,称作页号,页的号码,可以定位到具体是哪一个页。由6个位控制,最多寻址64页,符合规格书中的一块有64页。

而其中,BA6~BA15,表示对应的块号,即属于哪个块,有10个位控制,寻址范围为1024个块。

// 可见:地址的传输顺序是是 页内地址,页号,块号。从小到大。

简单解释完了地址组成,那么就很容易分析上面例子中的地址了:

0x7D0CCB8 = 0111 1101 0000 1100 0000 1100 1011 1000,分别分配到4个地址周期就是:

1st 周期,CA7~CA0 :1011 1000 = 0x B8

2nd周期,CA11~CA8 :0000 1100 = 0x 0C

3rd周期,BA7~PA0 :0000 1100 = 0x 0C

4th周期,A27~A20 :0111 1101 = 0x 7D

注意,上图图中对应的,*L,意思是低电平,由于未用到那些位,datasheet中强制要求设为0,所以,才有上面的2nd周期中的高4位是0000.。因此,接下来要介绍的,我们要访问第1000个块中的第25页中的1208字节处的话,所要传入的地址就是分4个周期,分别传入2个列地址的:0xB8,0x0C,然后再传2个行地址的:0x0C,0x7D,这样硬件才能识别。

4.读操作过程的解释

准备工作终于完了,下面就可以开始解释说明,对于读操作的,上面图中标出来的,1-6个阶段,具体是什么含义。

(1) 操作准备阶段:此处是读(Read)操作,所以,先发一个图5中读命令的第一个阶段的0x00,表示,让硬件先准备一下,接下来的操作是读。

(2) 发送两个周期的列地址。也就是页内地址,表示,我要从一个页的什么位置开始读取数据。

(3) 接下来再传入三个行地址。对应的也就是页号。

(4) 然后再发一个读操作的第二个周期的命令0x30。接下来,就是硬件内部自己的事情了。

(5)Nand Flash内部硬件逻辑,负责去按照你的要求,根据传入的地址,找到哪个块中的哪个页,然后把整个这一页的数据,都一点点搬运到页缓存中去。而在此期间,你所能做的事,也就只需要去读取状态寄存器,看看对应的位的值,也就是R/B#那一位,是1还是0,0的话,就表示,系统是busy,仍在”忙“(着读取数据),如果是1,就说系统活干完了,忙清了,已经把整个页的数据都搬运到页缓存里去了,你可以接下来读取你要的数据了。

对于这里。估计有人会问了,这一个页一共2048+64字节,如果我传入的页内地址,就像上面给的1028一类的值,只是想读取1028到2011这部分数据,而不是页开始的0地址整个页的数据,那么内部硬件却读取整个页的数据出来,岂不是很浪费吗?答案是,的确很浪费,效率看起来不高,但是实际就是这么做的,而且本身读取整个页的数据,相对时间并不长,而且读出来之后,内部数据指针会定位到你刚才所制定的1208的那个位置。

(6) 接下来,就是“窃取“系统忙了半天之后的劳动成果的时候了,呵呵。通过先去Nand Flash的控制器中的数据寄存器中写入你要读取多少个字节(byte)/字(word),然后就可以去Nand Flash的控制器的FIFO中,一点点读取你要的数据了。

至此,整个Nand Flash的读操作就完成了。

对于其他操作,可以根据上面的分析,一点点自己去看datasheet,根据里面的时序图去分析具体的操作过程,然后对照代码,会更加清楚具体是如何实现的。

11、NAND FLASH 搭配NOR FLASH的优缺点

常见的应用组合就是,用小容量的Nor Flash存储启动代码,比如uboot,系统启动后,初始化对应的硬件,包括SDRAM等,然后将Nand Flash上的Linux 内核读取到内存中,做好该做的事情后,就跳转到SDRAM中去执行内核了。

这样的好处是由于NAND 本身有坏块的可能性,所以为了保障启动万无一失,很多要求高级安全的产品,标注必须从NOR Flash启动uboot,而且从NOR启动还有一个好处就是启动速度快,NAND Flash的优点是容量大,但是读取速度不快,比不上NOR Flash,比如一些对于开机速度有要求的产品应用,比如车载液晶仪表,这类产品为了快速启动一般都是NOR FLASH+EMMC的配置,当然像赛普拉斯平台直接上hyperflash那就更快了。

12、NAND Flash的ECC校验简单说明

我们先来说说为什么需要ECC校验这个事情,其实上一篇文章我们说过由于NAND flash的自身的不稳定性,存在位翻转的现象,所以就存在写入到flash中的数据和读出来的数据不一样的情况发生,此时就需要有一个检验的机制,防止读出来的不正确,还可以纠正过来。

其实这个就类似于去银行存钱,你存了1W,过几天去银行去取钱的时候发现只有9000了,这个时候你就会拿出存条找银行理论,上次明明存的就是1W啊,你少的1000必须跟我纠正过来,其实这个就是NAND flash的ECC检验原理,发现有读出来的数据和存进去的数据不正确,此时就需要去纠正回来,当然这里的纠正的数据是有限制的,不是所有数据出错都能纠正过来。

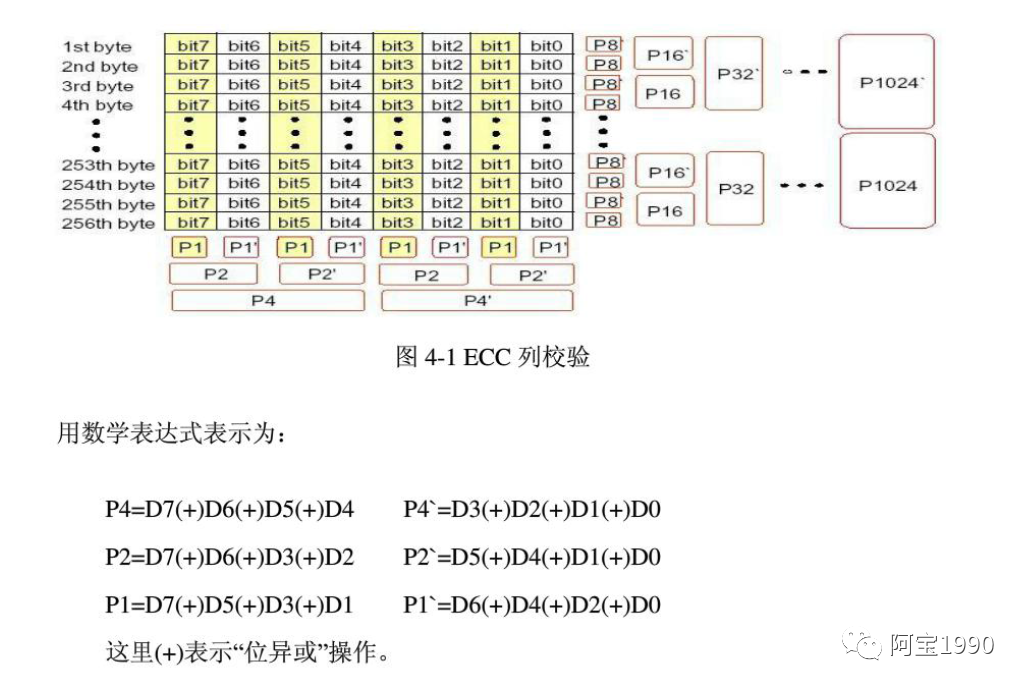

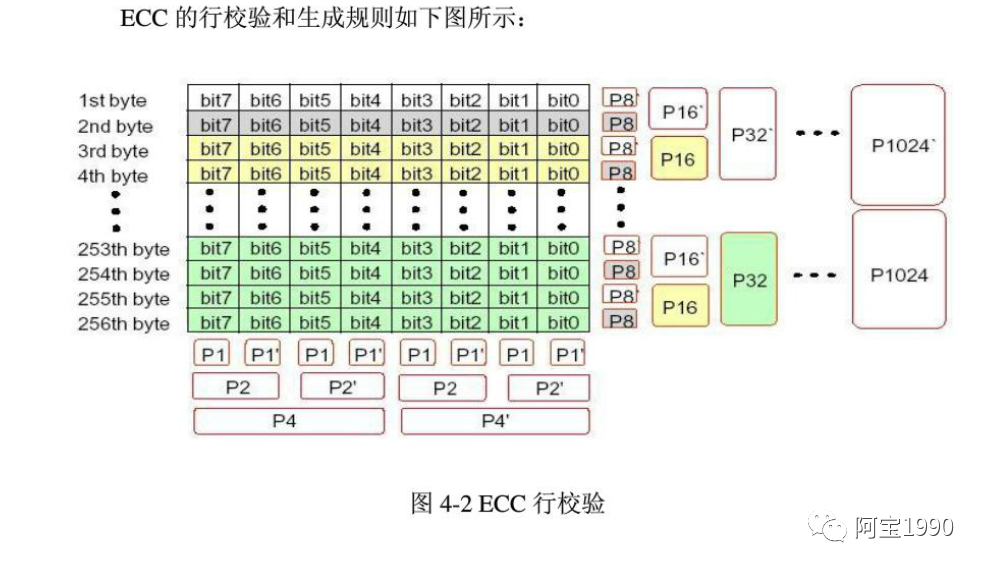

ECC 校验是在奇偶校验的基础上发展而来的,它将数据块看作一个矩阵,利用矩阵的行、列奇偶信息生成 ECC 校验码。它能够检测并纠正单比特错误和检测双比特错误,但对双比特以上的错误不能保证检测。它克服了传统奇偶校验只能检出奇数位出错、校验码冗长、不能纠错的局限性。每 nbit 的 Ecc 数值可满足 2的n次方bit 数据包的校验要求。

当往Nand Flash 的Page 中写入数据的时候,每256字节我们生成一个ECC 校验和,称之为原ECC校验和,保存到 PAGE 的OOB数据区中。当从Nand Flash 中读取数据的时候,每 256 字节我们生成一个ECC校验和,称之为新 ECC 校验和。

校验的时候,根据上述ECC生成原理不难推断:将从 OOB 区中读出的原 ECC校验和新ECC校验和按位异或,若结果为0,则表示不存在错(或是出现了ECC无法检测的错误):若3个字节异或结果中存在11个比特位为1,表示存在一个比特错误,且可纠正;若3个字节异或结果中只存在1个比特位为1,表示OOB区出错:其他情况均表示出现了无法纠正的错误。

![从零开始学RSA: [WUSTCTF2020]情书等5题](https://img-blog.csdnimg.cn/direct/51bd0d35ea2a484c8d4a692c8333ac28.bmp#pic_center)