JTAG Boot(JTAG启动)是一种使用JTAG接口来启动设备的方法。JTAG(Joint Test Action Group)是一种国际标准测试协议,最初用于对芯片进行测试,现在已广泛应用于各种设备的调试和启动过程。在JTAG Boot过程中,设备通过JTAG接口接收启动指令和配置数据。这些数据通常包括设备的配置信息、引导加载程序(Bootloader)等。一旦设备接收到这些数据,它就会根据这些信息来初始化硬件、加载操作系统或执行其他必要的启动步骤。

在Zynq设备中,存在两个JTAG控制器:TAP(测试访问端口)控制器和DAP(调试访问端口)控制器。TAP控制器可以控制PL配置过程以及PL中的其他功能。而DAP控制器位于应用处理单元(APU)中。

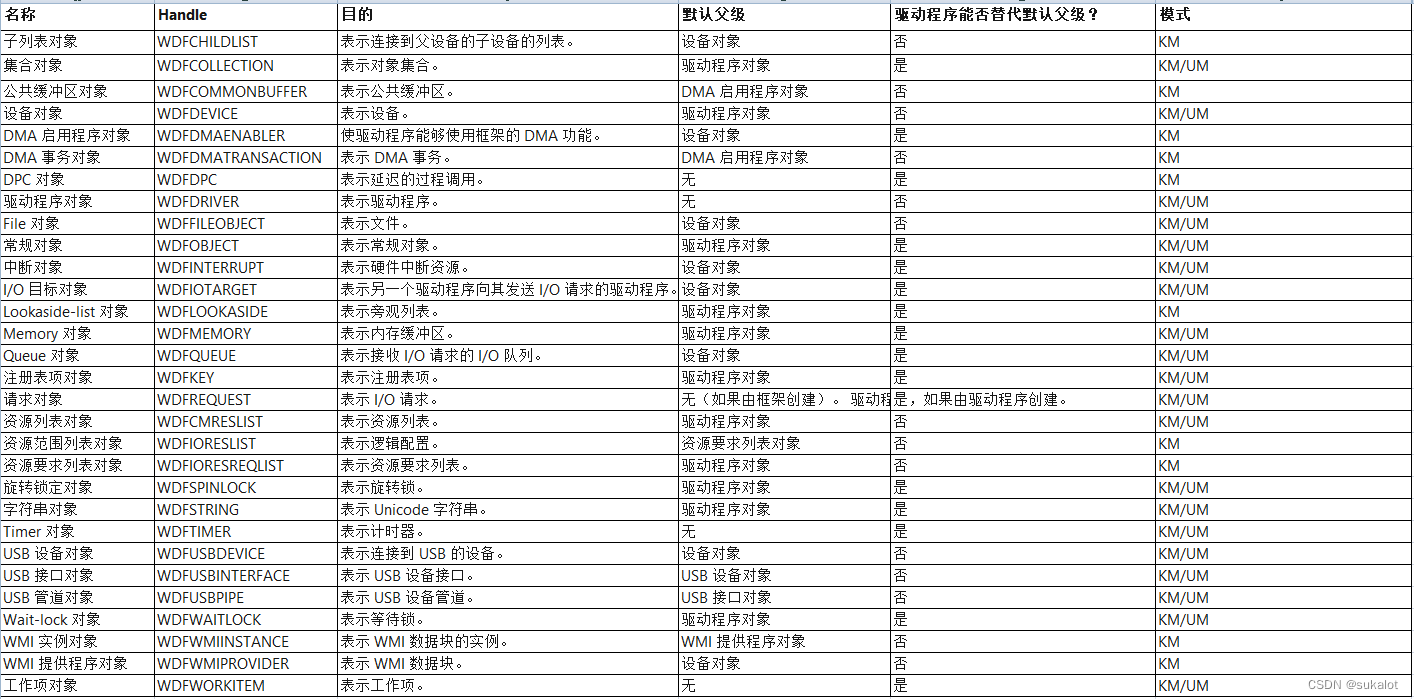

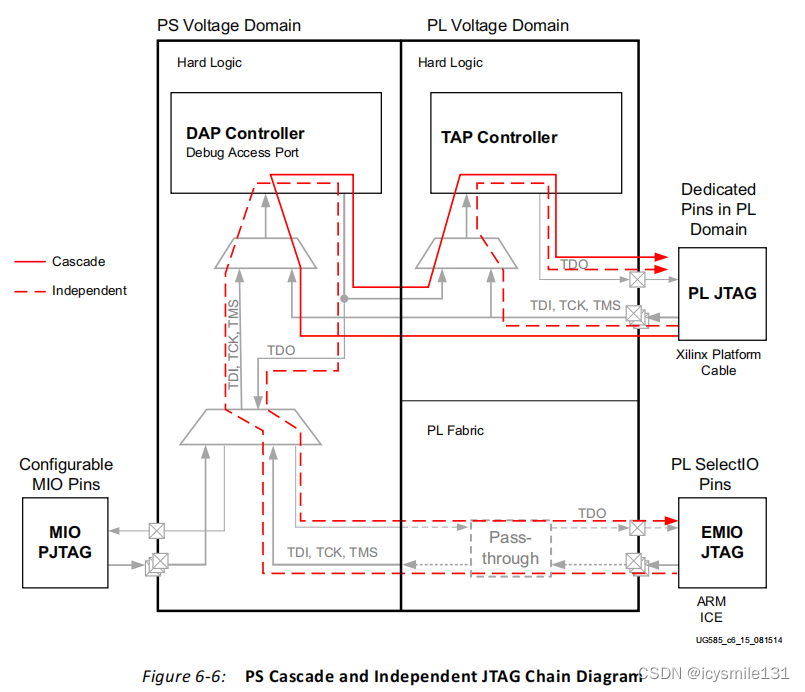

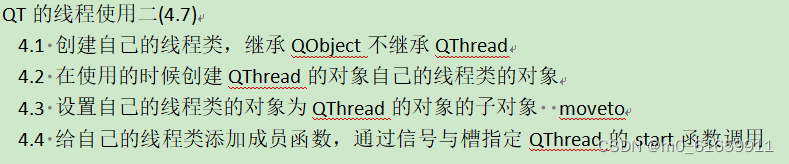

要访问这些JTAG控制器,有两种链接模式:级联模式和独立模式,如图6-6所示。

1 JTAG的启用/禁用控制

JTAG的启用/禁用控制涉及到几个关键的机制,这些机制主要控制DAP和TAP控制器。

级联与独立模式

级联模式允许多个JTAG设备通过JTAG接口串联在一起,形成一个JTAG链,从而可以单独测试各个设备。而独立模式则允许设备独立工作,不与其他JTAG设备形成链。

启用/禁用DAP和TAP控制器

可以根据需要启用或禁用DAP和TAP控制器。禁用这些控制器可以防止通过JTAG接口对设备进行调试或访问。

永久禁用JTAG

某些设备提供了永久禁用JTAG的功能,通常通过烧写特定的电子保险丝(eFuse)位来实现。一旦JTAG被永久禁用,将无法通过JTAG接口进行任何调试或访问操作,这有助于保护设备的安全性。

当JTAG处于默认的级联链模式时,可以通过devcfg.CTRL[JTAG_CHAIN_DIS]位来启用或禁用PL(可编程逻辑)JTAG引脚连接。当JTAG_CHAIN_DIS位被设置为1时,PL JTAG引脚信号将无法到达DAP控制器,因此无法通过级联链通过PL JTAG引脚向DAP和TAP控制器发送有意的JTAG指令。

JTAG_CHAIN_DIS并不会阻止PL JTAG的TCK和TMS引脚信号到达PL TAP控制器。因此,如果TCK和TMS被切换,TAP控制器的状态可能会发生变化。

DAP控制器通过设置devcfg.CTRL[DAP_EN]位为111来启用。任何其他值都会导致DAP控制器被绕过。通过设置devcfg.LOCK[DBG_LOCK]位为1,可以锁定这个位。一旦锁定,只能通过POR(上电复位)来解锁。

DAP和TAP控制器可以通过烧写JTAG链禁用eFuse来永久禁用。一旦eFuse被烧写,这些控制器将永远无法再被访问。软件可以通过devcfg.STATUS[EFUSE_JTAG_DIS]位来读取eFuse的状态。

如果软件试图在没有正确密钥的情况下解锁DevC模块中的APB寄存器空间,那么这将导致DAP控制器被禁用,直到下一次POR(上电复位)发生。这个状态可以通过读取devcfg.STATUS[ILLEGAL_APB_ACCESS]位来检测。

当选择JTAG Boot模式时,BootROM将禁用对所有与安全相关的项的访问,启用JTAG端口,并通过执行WFE指令使CPU进入等待状态。在唤醒CPU并继续启动过程之前,用户有责任通过DAP控制器将启动映像下载到OCM或DDR内存中。

总的来说,JTAG Boot模式提供了一种通过JTAG接口加载启动映像的方式,但在此过程中,BootROM会禁用对安全相关项的访问,并确保CPU在启动映像下载完成之前保持等待状态。用户需要确保在唤醒CPU之前,通过DAP控制器正确地将启动映像加载到内存中。

2 JTAG Boot的示例流程

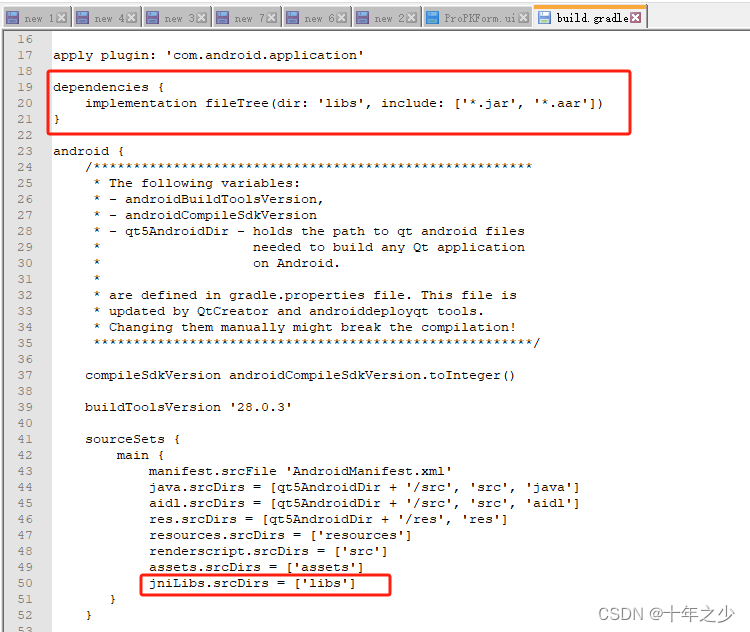

JTAG Boot模式始终是非安全的;AES单元被禁用,并且不支持加密的映像。JTAG启动和PS/PL配置流程如图6-6所示。具体序列如下:

①PS和PL上电;PS_CLK稳定。

②PS_POR_B复位解除。

③BootROM开始执行并确定启动模式。

④如果启用,BootROM执行CRC自检。

⑤BootROM在MIO上编程VMODE。

⑥BootROM禁用所有安全功能并启用DAP控制器。

⑦BootROM启用JTAG路径:

a. Cascade(级联):JTAG链设置为级联模式;可以使用PL JTAG接口访问DAP和TAP控制器。

b. Independent(独立):JTAG链设置为独立模式;TAP控制器可以通过PL JTAG接口访问,而DAP控制器则通过EMIO ⑧JTAG访问。BootROM会等待最多90秒,以便使用TAP控制器为EMIO JTAG连接编程PL。

⑧BootROM关闭并让CPU运行等待事件(WFE)指令:

a. Cascade:BootROM关闭并将系统控制权释放给TAP和DAP控制器的JTAG接口。

b. Independent:BootROM等待PL初始化完成后关闭。DAP控制器的EMIO JTAG接口必须通过PL使用比特流进行路由才能正常工作。

⑨用户可以访问DAP控制器进行PS系统调试:

a. Cascade:PL JTAG接口链上的第一个设备。

b. Independent:EMIO JTAG接口链上的单个设备。

⑩用户可以访问TAP控制器以配置PL:

a. Cascade:PL JTAG接口链上的第二个设备。

b. Independent:PL JTAG接口链上的单个设备。

在使用L2缓存时,为确保系统的高可靠性,应根据AR# 54190的说明将slcr.L2C_RAM寄存器设置为0x0002_0202的值。

3 级联JTAG链模式

在级联模式下,可以使用PL JTAG接口引脚同时访问两个控制器;来自接口的TDI信号会进入DAP控制器。DAP控制器的TDO信号会被连接到TAP控制器的输入端,形成菊花链结构。然后,TAP控制器的TDO信号会输出到JTAG接口。在JTAG链中,DAP寄存器和数据是最后被移入的。

• 首先访问DAP控制器,然后访问TAP控制器。

• 不需要PL配置。

• 两个控制器都必须启用。

• 指令和数据不能对未指定的目标产生不良影响。

使用级联JTAG链模式时,需要确保正确连接JTAG接口引脚,并遵循相关的JTAG协议和规范,以确保正确访问和配置控制器。此外,为了避免潜在的冲突或干扰,还应确保指令和数据不会对非目标设备造成影响。

4 独立JTAG链模式

独立JTAG链模式将TAP控制器连接到PL JTAG接口,并为用户提供时间,以便使用TAP控制器通过位流配置PL,如图6-6所示。BootROM会等待最多90秒,等待PL配置完成,然后启用DAP控制器并继续启动过程。如果PL未能在规定时间内完成配置,则系统会锁定。

TAP控制器通过PL JTAG引脚进行访问,用于配置PL。在PL通过位流配置完成后,DAP控制器变得可访问。

在独立模式下,TAP控制器的行为类似于AMD 7系列FPGA中的TAP控制器。

5 独立模式下的EMIO PJTAG和MIO PJTAG接口

在独立模式下,EMIO PJTAG接口和MIO PJTAG接口为开发者提供了与DAP控制器交互的途径。

对于EMIO PJTAG接口,PL需要通过加载位流来配置,以启用EMIO PJTAG接口与DAP控制器的连接。在启动后,可以断言PROGRAM_B信号,并在DONE信号被断言后将位流加载到PL中。这样做是为了在独立JTAG模式下启用EMIO PJTAG接口来控制DAP控制器。需要注意的是,这一功能仅在生产硅片时受支持,并且系统需要以独立JTAG启动模式启动。BootROM会等待PL完成自我初始化,然后启用PS-PL电平移位器,启用PL JTAG接口,并在CPU上发出WFE指令。

对于MIO PJTAG接口,DAP控制器也可以与之交互,但这需要FSBL/用户代码使用slcr.MIO_PIN_xx寄存器对MIO多路复用器进行编程。MIO PJTAG接口可以路由到四组MIO引脚中的一组。使用MIO PJTAG接口和DAP控制器时,不需要PL电源。

TAP控制器本身无法直接编程MIO多路复用器。因此,必须从包含FSBL/用户代码的闪存设备启动,该代码负责为MIO PJTAG接口配置MIO多路复用器。一旦MIO多路复用器被编程,就可以使用MIO PJTAG接口访问DAP控制器了。

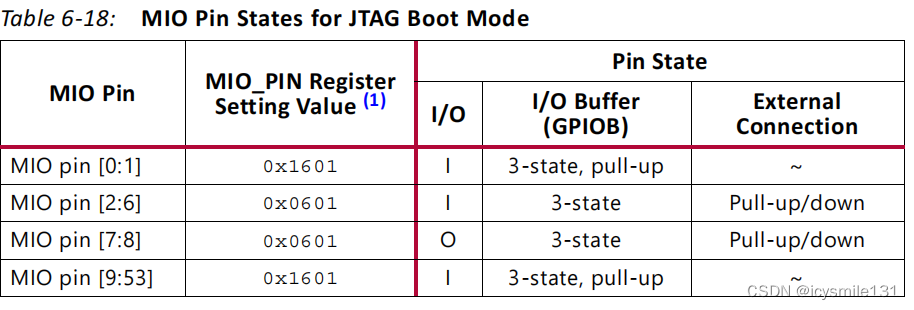

6 JTAG启动模式下,MIO的引脚状态

在JTAG启动模式下,MIO寄存器的值如Table 6-18所示。这些值对级联(Cascade)和独立(Independent)JTAG启动模式都是有效的。

![[数据结构]———交换排序](https://img-blog.csdnimg.cn/direct/7fb0534550834b0681b193b62c6bec0e.png)