数字IC设计、验证、FPGA笔试必会 - Verilog经典习题 (六)多功能数据处理器

🔈声明:

😃博主主页:王_嘻嘻的CSDN博客

🧨未经作者允许,禁止转载

🔑系列专栏:牛客Verilog习题集

🚩推荐一个IC、FPGA新手入门的好网站:👉快 点 击 进 入 学 习 吧

继续整理牛客网经典Verilog习题讲解,牛客网里除了最新的Verilog题库还有其它领域的经典笔试、面试题,大家快和我一起刷起来吧 点 击 跳 转

题目

根据指示信号select的不同,对输入信号a,b实现不同的运算。输入信号a,b为8bit有符号数,当select信号为0,输出a;当select信号为1,输出b;当select信号为2,输出a+b;当select信号为3,输出a-b.

分析:

本题和1、5题类似,无非是在一个多路选择器上扩展了一些功能,唯一需要注意的是,本题的输入是有符号数,是存在符号位的。相信很多新手朋友们可能还没学习过signed和unsigned的一些特性,这部分内容可以参照我之前总结的一篇blog:Verilog的signed和unsigned

题解:

- 对于sel=0和sel=1时,是直接的赋值,在扩位时需要扩展的是符号位a[7]、b[7],而不是1‘b0;

- 对于sel=2和sel=3时,是带有运算的处理,因为a、b、c都声明了signed,所以编译器自动会按有符号处理,不用手动扩位也能实现正确功能。但是如果变量是1-bit有符号数,就需要谨慎考虑了;

- 最后,如果朋友们实在搞不清有符号数该如何处理,使用$signed()函数是一个不错的选择;

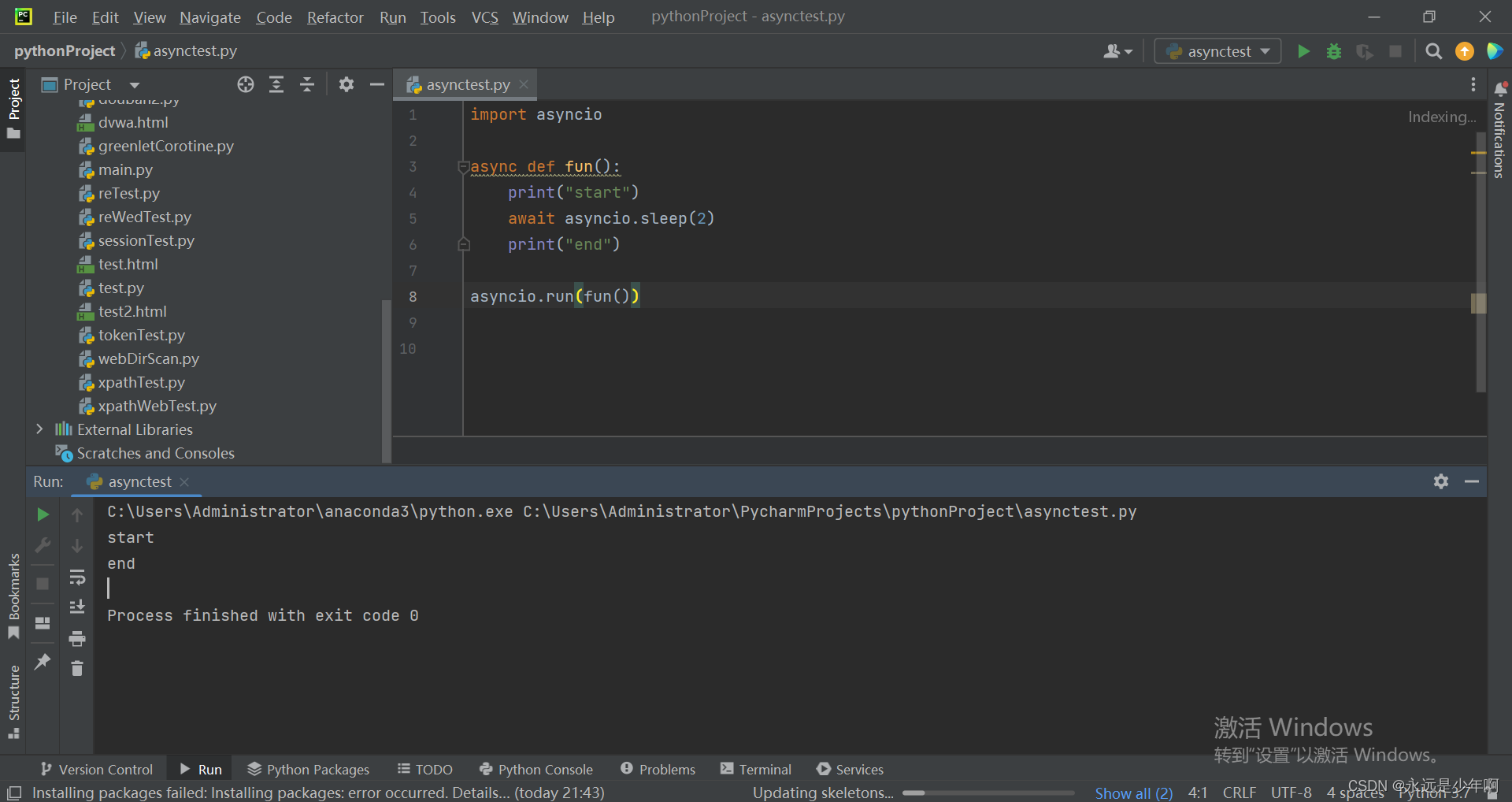

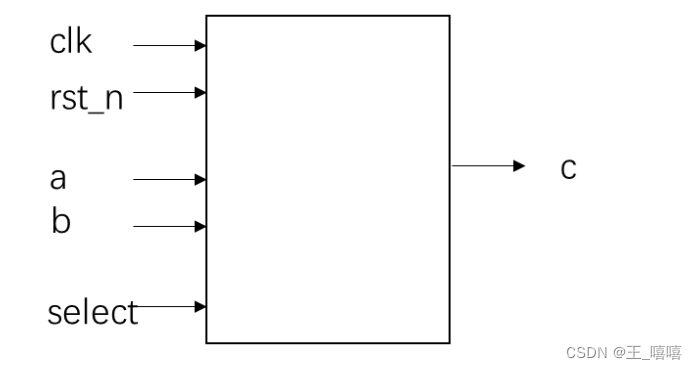

`timescale 1ns/1ns

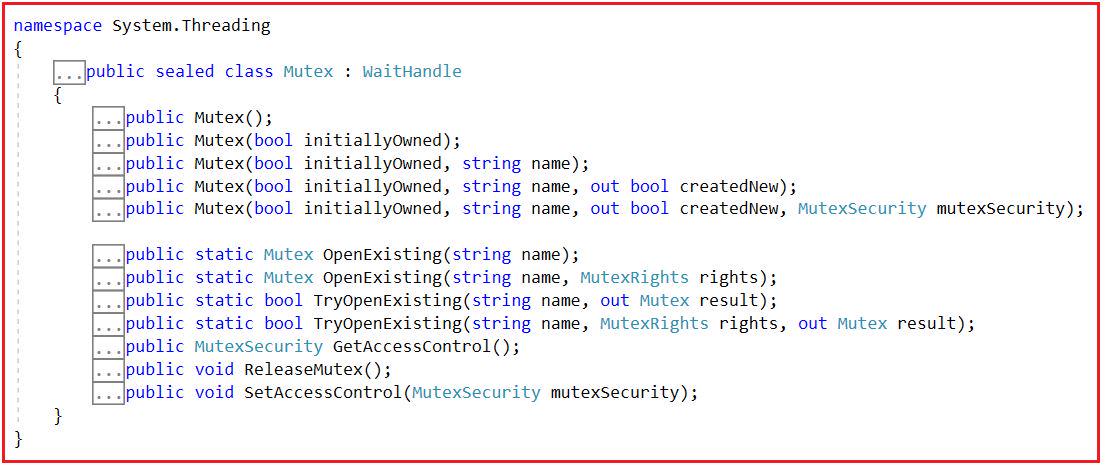

module data_select(

input clk,

input rst_n,

input signed[7:0]a,

input signed[7:0]b,

input [1:0]select,

output reg signed [8:0]c

);

always @(posedge clk or negedge rst_n)begin

if(!rst_n)

c[8:0] <= 9'b0;

else begin

case(select[1:0])

2'b00: c[8:0] <= {a[7],a[7:0]};

2'b01: c[8:0] <= {b[7],b[7:0]};

2'b10: c[8:0] <= a[7:0] + b[7:0];

2'b11: c[8:0] <= a[7:0] - b[7:0];

endcase

end

end

endmodule

![[acwing周赛复盘] 第 86 场周赛20230114](https://img-blog.csdnimg.cn/82cf94fe746b4b4ab41e8c01aaed2f46.png)