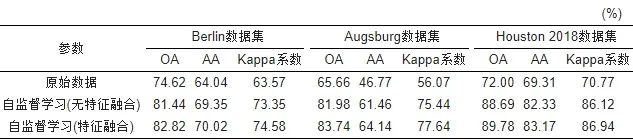

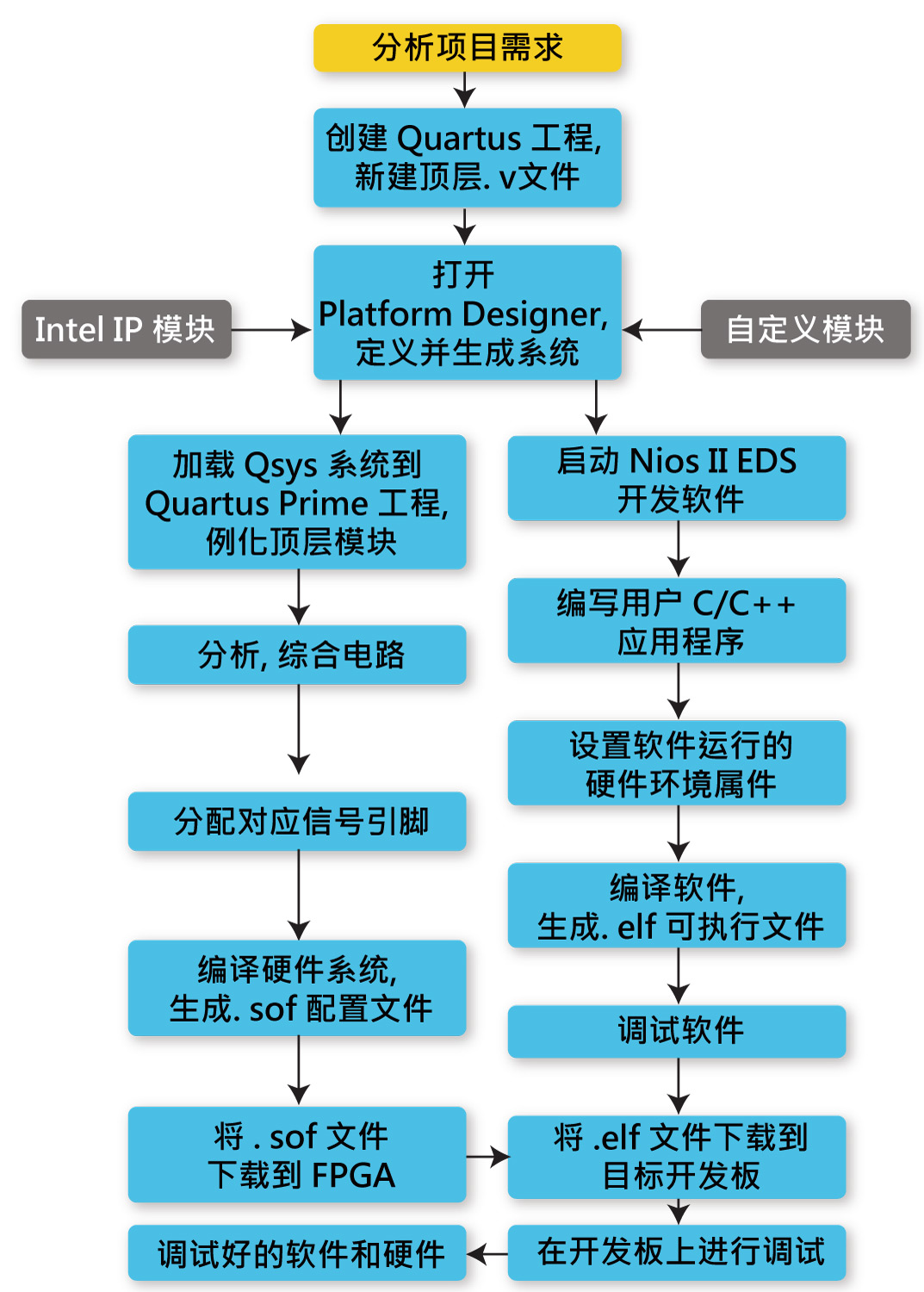

Q:本期我们开始介绍创建Platform Designer系统,并设计基于Nios II Professor的Hello_world工程。

A:设计流程和实验原理:需要用到的IP组件有Clock Source、Nios II Professor、On-Chip Memory、JTAG UART和System ID外设。Nios II Processor是整个系统的核心,其他组件都会通过Avalon总线连接到这个系统核心上,关于Nios II处理器的详细说明和用法可参考Nios II Processor Reference Guide。基于Nios II Professor的设计开发流程:

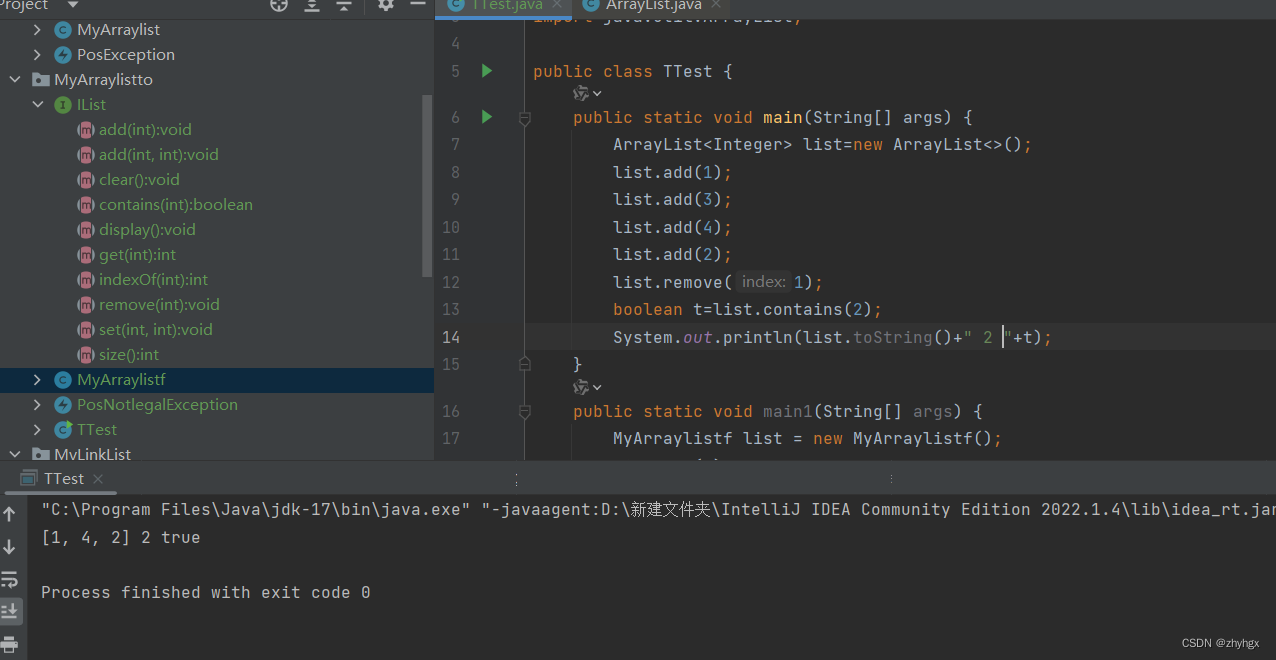

On-Chip Memory用来控制和分配片上存储资源;JTAG UART是PC与FPGA通信的控制台,PC可以将数据通过JTAG传输到FPGA,也能将FPGA产生的数据回传到PC;

然后需要分别用Quartus软件完成系统的硬件设计部分,生成硬件部分的可配置文件(.sof);

在Nios SBT中完成软件设计部分(用printf函数打印出“Hello_World from Nios II!”字符),生成可执行程序(hello_world.elf),最终系统将“ Hello_World from Nios II! ”字符串通过JTAG UART传输到PC并显示在Nios II Console终端。

![[计算机效率] 网站推荐:文字转语音](https://img-blog.csdnimg.cn/direct/552909efef79459b9dfd2dd62cc92280.png)

![[SWPUCTF 2022 新生赛]ez_ez_unserialize](https://img-blog.csdnimg.cn/direct/1ddd06a2f8924002b33be8f1bd004d13.png)