1.概述

配置空间是PCIe设备/桥的标识符,其保存了设备/桥的信息。主机在枚举设备/桥的时候需要先访问配置空间,获取设备厂家、型号、类型、所需资源等信息,然后再分配资源,最后才能访问PCIe设备的存储或IO地址空间。PCIe总线规定了三种类型的配置空间,分别是PCIe Agent设备使用的配置空间、PCIe桥使用的配置空间和Cardbus桥片使用的配置空间,本节只介绍前两种。

2.配置空间布局

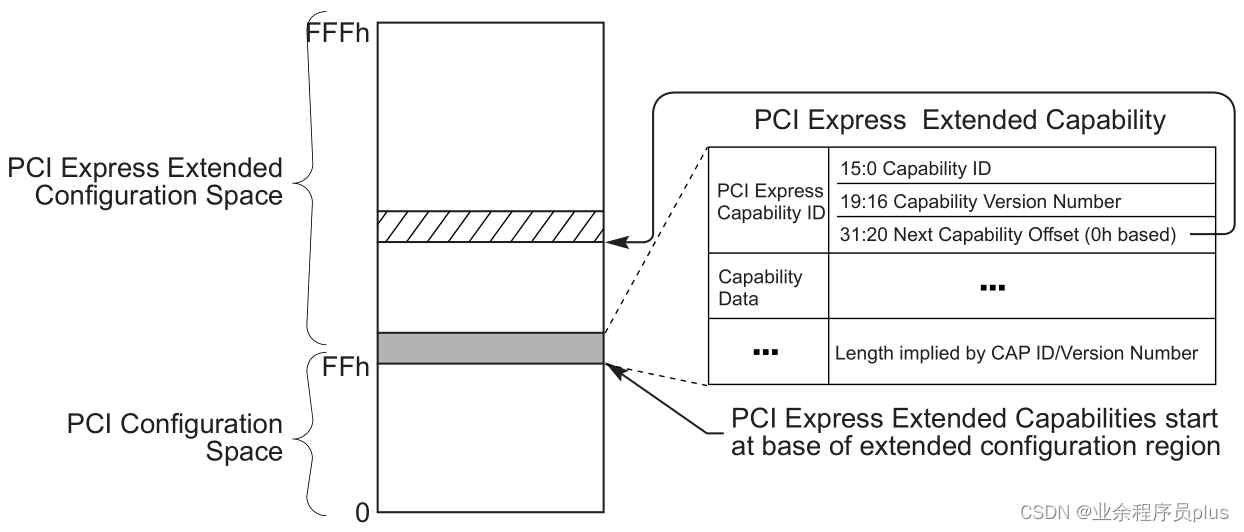

PCIe配置空间的布局如下图所示,总共4KB,PCIe设备的每个Function都对应一个配置空间。0-3Fh(64字节)是PCI兼容配置空间头,按类型可分为Type 0配置空间头和Type 1配置空间头。PCIe设备使用Type 0配置空间头,PCIe桥使用Type 1配置空间头。所有的PCI、PCI-X、PCIe设备(桥)必须支持64字节的配置空间头,即00h-40h。40h-FFh(192字节)是PCI/PCI-X和PCIe扩展的配置空间,主要存放一些与MSI或者MSI-X中断机制和电源管理相关的Capability Structures。支持中断的PCI、PCI-X、PCIe设备(桥)必须支持40h-FFh的配置空间。0-FFh(256字节)是PCI兼容配置空间,可通过传统的PCI方式(基于ID寻址)或PCIe ECAM(Enhanced Configuration Access Mechanism)访问。100h-FFFh(3840字节)是PCIe协议扩展的可选配置空间,主要存放AER、虚拟通道、设备序列号等Capability Structures。100h-FFFh只能通过PCIe ECAM访问。

在一个PCIe总线中,Type 0配置空间头和Type 1配置空间头如下图所示。

3.Type 0 Header

Type 0配置空间头如下图所示。

每个字段的具体意义如下:

| 字段 | 意义 | 偏移地址 | 宽度 |

|---|---|---|---|

| Vendor ID | 厂商ID,由PCI-SIG统一分配,如Intel的厂商ID为0x8086, | 0x00 | 2B |

| Device ID | 设备ID,由PCI-SIG统一分配,如Intel 82571EB网卡的设备ID为0x105E | 0x02 | 2B |

| Command | 命令寄存器,初始化的时候默认值为0,具体见下面的解释 | 0x04 | 2B |

| Status | 保存PCIe状态 | 0x06 | 2B |

| Revision ID | 保存PCIe版本号 | 0x08 | 1B |

| Class Code | 保存PCIe设备的分类,由Base Class Code、Sub Class Code和Interface组成。Base Class Code是设备的基本分类,如显卡、网卡、PCIe桥等设备。Sub Class Code则会将设备进一步细分。Interface定义编程接口。 | 0x09 | 3B |

| Cache Line Size | 保存主机处理器的Cache行长度,该寄存器由主机的系统软件设置。若PCIe设备不支持与Cache相关的总线事务,系统软件可不设置该寄存器。 | 0x0C | 1B |

| Latency Timer | 控制PCI设备占用总线的时间,对PCIe总线无意义。 | 0x0D | 1B |

| Header Type | 记录设备的类型。bit[7]=0表示单功能设备,bit[7]=1表示多功能设备,bit[6:0]=0表示PCIe Agent设备,bit[6:0]=1表示PCIe桥设备,bit[6:0]=2表示PCIe CardBus桥。 | 0x0E | 1B |

| BIST | 可选,用于内部自检 | 0x0F | 1B |

| Base Address 0 | BAR寄存器,保存主机分配给该PCIe设备的PCIe域地址,64位地址使用2个BAR | 0x10 | 4B |

| Base Address 1 | BAR寄存器,保存主机分配给该PCIe设备的PCIe域地址,64位地址使用2个BAR | 0x14 | 4B |

| Base Address 2 | BAR寄存器,保存主机分配给该PCIe设备的PCIe域地址,64位地址使用2个BAR | 0x18 | 4B |

| Base Address 3 | BAR寄存器,保存主机分配给该PCIe设备的PCIe域地址,64位地址使用2个BAR | 0x1C | 4B |

| Base Address 4 | BAR寄存器,保存主机分配给该PCIe设备的PCIe域地址,64位地址使用2个BAR | 0x20 | 4B |

| Base Address 5 | BAR寄存器,保存主机分配给该PCIe设备的PCIe域地址,64位地址使用2个BAR | 0x24 | 4B |

| Cardbus CIS Pointer | 不介绍 | 0x28 | 4B |

| Subsystem Vendor ID | 记录PCIe设备生产厂商 | 0x2C | 2B |

| Subsystem ID | 记录PCIe设备生产厂商 | 0x2E | 2B |

| Expansion ROM Base Address | 固件程序地址,用于初始化PCIe设备 | 0x30 | 4B |

| Capabilities Pointer | Capabilities寄存器相对于配置空间的偏移地址,PCI-X和PCIe必须支持该功能 | 0x34 | 1B |

| Reserved | 保留 | 0x35 | 3B |

| Reserved | 保留 | 0x38 | 4B |

| Interrupt Line | 保存当前PCIe设备使用的中断向量号,由主机系统软件分配,通常不使用 | 0x3C | 1B |

| Interrupt Pin | 保存PCIe设备使用的中断引脚,由主机系统软件分配,1表示INTA#,2表示INTB#,3表示INTC#,4表示INTD#,PCIe设备可使用INTx模拟INTA~D#中断 | 0x3D | 1B |

| Min_Gnt | PCIe设备能忍受的最大延时,只读寄存器 | 0x3E | 1B |

| Max_Lat | PCIe设备期望的最小延时,只读寄存器 | 0x3F | 1B |

3.1.Command

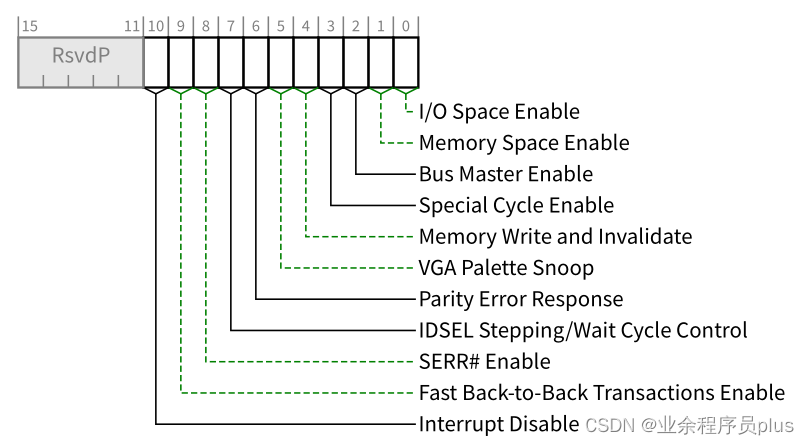

Command寄存器为PCIe设备的命令寄存器,默认值为0,此时PCIe设备除了能够接收配置请求总线事之外,不能接收任何存储器或者I/O请求。

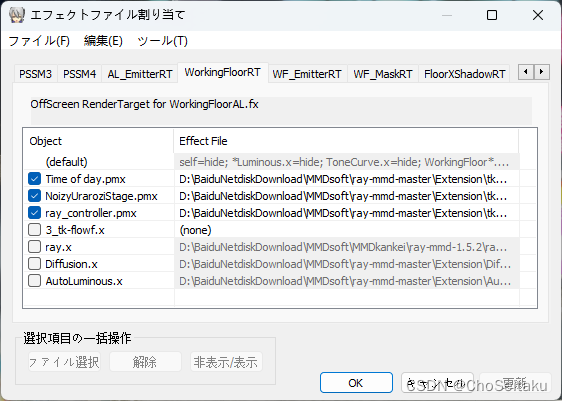

Command寄存器位域如下图所示:

Command寄存器位域定义如下表所示:

| 位域 | 意义 | 属性 |

|---|---|---|

| 0 | I/O Space位,默认值为0。表示是否响应I/O请求。为1时响应,为0时不响应。如果支持I/O空间,系统软件会将该位置1。 | RW |

| 1 | Memory Space位,默认值为0。表示是否响应Memory请求。为1时响应,为0时不响应。如果支持Memory地址空间,系统软件会将该位置1。 | RW |

| 2 | Bus Master位,默认值为0。对于EP表示是否可以发送I/O或者Memory请求,包括MSI/MSI-X中断,对于Root和Switch端口表示是否会将I/O或者Memory请求转发到上行端口。为1时可以发送或者可以转发,为0时不发送或者不转发。 | RW |

| 3 | Special Cycle位,默认值为0。表示是否响应Special总线事务。为1时响应,为0时不响应。Special总线事务可以将一些信息广播到多个目标设备 | RO |

| 4 | Memory Write and Invalidate位,默认值为0。对于PCIe总线没有意义 | RO |

| 5 | VGA Palette Snoop位,默认值为0。对于PCIe总线没有意义 | RO |

| 6 | Parity Error Response位,默认值为0。此位控制TLP出现奇偶校验错误时是否在Status寄存器中记录。为1时记录,为0时不记录 | RW |

| 7 | IDSEL Stepping/Wait Cycle Control位,默认值为0。对于PCIe总线没有意义 | RO |

| 8 | SERR# Enable位,默认值为0。对于PCIe总线没有意义 | RO |

| 9 | Fast Back-to-Back Transactions Enable位,默认值为0。对于PCIe总线没有意义 | RO |

| 10 | Interrupt Disable位,默认值为0。表示EP是否可以发送INTx中断。为1时不可以,为0时可以。 | RW |

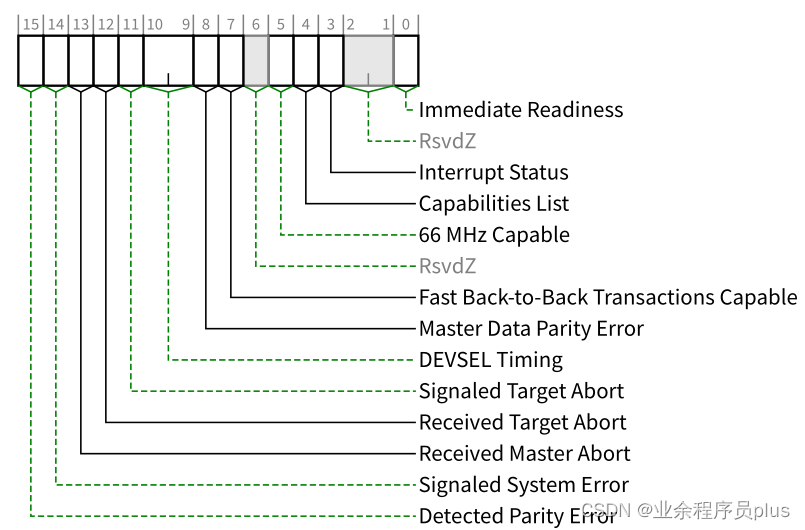

3.2.Status

Status寄存器保存PCIe设备的状态。

Status寄存器的位域如下图所示:

Status寄存器的位域定义如下表所示:

| 位域 | 意义 | 属性 |

|---|---|---|

| 0-2 | 保留 | RO |

| 3 | 中断状态位。该位为1时且Command bit[10]=0,表示PCIe设备使用INTx信号提交中断。大多数的PCIe设备有自己的中断状态寄存器,可同通过BAR访问,很少使用该寄存器。 | RO |

| 4 | Capabilities List有效位。为1时Capabilities Pointer有效,否则无效 | RO |

| 5 | 66MHz Capability位,默认值为0。为1时表示PCIe设备支持66MHz的PCI总线。对PCIe总线无意义 | RO |

| 6 | 保留 | RO |

| 7 | Fast Back-to-Back Transactions Capable位,默认值为0。对于PCIe总线没有意义 | RO |

| 8 | Master Data Parity Error位,默认值为0。当该位设置且Command寄存器bit[6]=1,对于EP Function来说,表示其收到了错误的完成报文或者其发送了错误的请求,对于Root Port、Switch上行口或者Switch下行口,表示其接收到了下行口的错误完成报文或者向上行口发送了错误的请求。Command寄存器bit[6]=0,该位保持为0 | RW1C |

| 9-10 | DEVSEL Timing,默认值为0。对于PCIe总线没有意义 | RO |

| 11 | Signaled Target Abort位,默认值为0。This bit is Set when a Function completes a Posted or Non-Posted Request as a Completer Abort error. This applies to a Function with a Type 1 Configuration header when the Completer Abort was generated by its Primary Side. | RW1C |

| 12 | Received Target Abort位,默认值为0。This bit is Set when a Requester receives a Completion with Completer Abort Completion Status. On a Function with a Type 1 Configuration header, the bit is Set when the Completer Abort is received by its Primary Side. | RW1C |

| 13 | Received Master Abort位,默认值为0。This bit is Set when a Requester receives a Completion with Unsupported Request Completion Status. On a Function with a Type 1 Configuration header, the bit is Set when the Unsupported Request is received by its Primary Side.。 | RW1C |

| 14 | Signaled System Error位,默认值为0。This bit is Set when a Function sends an ERR_FATAL or ERR_NONFATAL Message, and the SERR# Enable bit in the Command register is 1. | RW1C |

| 15 | Detected Parity Error,This bit is Set by a Function whenever it receives a Poisoned TLP, regardless of the state the Parity Error Response bit in the Command register. On a Function with a Type 1 Configuration header, the bit is Set when the Poisoned TLP is received by its Primary Side. | RW1C |

3.3.Base Address

Base Address寄存器简称为BAR,保存了PCIe设备/桥的Function使用的PCIe总线域地址的基地址。Type 0设备每个Function最多可以有6个BAR,Type 1设备每个Function最多可以有2个BAR。若使用64位PCIe总线域地址,则2个BAR表示一个64位地址,BARn表示低32位,BARn+1表示高32位。

BAR保存的PCIe总线域基地址有两种类型,分别是IO地址空间和存储地址空间,存储地址空间有4中属性,分别是预取(prefetchable)、非预取(non-prefetchable)、32位和64位。主机在枚举的时候先读取BAR,然后判断所需的总线域基地址类型,若是存储地址空间,则进一步获取存储地址空间的属性,接着向BAR写如0xFFFFFFFF,最后再读取BAR,根据可以写入的最低有效位,获取Function请求IO地址空间和存储地址空间的长度。

当BAR表示的是存储地址空间时,位域如下图所示:

当BAR表示的是IO地址空间时,位域如下图所示:

- 32位存储地址空间

32位存储地址空间分为预取(prefetchable)和非预取(non-prefetchable)。下面以32位非预取存储地址空间的初始化流程为例进行分析:- 当PCIe Function初始化完成后,BAR的基地址类型和属性也初始化完毕。图中bit[3-0]都是0,表示这是一个32位非预取存储地址空间。

- 主机先读取BAR,获取BAR的类型和属性。图中未画出。

- 主机向BAR的所有bit写1,此时BAR中可以写入的bit变为1,不可写入bit的保持原来的值。图中bit[31-12]=1,表示该BAR请求的存储地址空间大小为2^12=4KB。

- 主机获取这些信息后,向BAR中配置存储地址空间的基地址。图中配置的是0xF9000000,bit[11-0]保持为0,即该BAR表示的32位非预取存储地址空间范围为0xF9000000-0xF9000FFF,大小为4KB。

实质上,当该BAR表示的PCIe总线域地址向存储域地址转换时,bit[31-12]被转换为存储域基地址,bit[11-0]被视为存储域基地址的偏移,直接映射到存储域空间,不做转换。

- 64位存储地址空间

64位存储地址空间分为预取(prefetchable)和非预取(non-prefetchable)。下面以64位预取存储地址空间的初始化流程为例进行分析:- 当PCIe Function初始化完成后,BAR的基地址类型和属性也初始化完毕。图中bit[3-0]=0xC,表示这是一个64位预取存储地址空间,需要两个BAR表示。

- 主机先读取BAR,获取BAR的类型和属性。图中未画出。

- 主机向BARn和BARn+1的所有bit写1,此时BAR中可以写入的bit变为1,不可写入bit的保持原来的值。图中bit[63-26]=1,表示该BAR请求的存储地址空间大小为2^26=64MB。

- 主机获取这些信息后,向BAR中配置存储地址空间的基地址。图中配置的是0x240000000,bit[25-0]保持为0,即该BAR表示的64位预取存储地址空间范围为0x240000000-0x243FFFFFF,大小为64MB。

实质上,当该BAR表示的PCIe总线域地址向存储域地址转换时,bit[63-26]被转换为存储域基地址,bit[25-0]被视为存储域基地址的偏移,直接映射到存储域空间,不做转换。

- IO地址空间

IO地址空间的初始化流程如下图所示:- 当PCIe Function初始化完成后,BAR的基地址类型也初始化完毕。图中bit[0]=0x0,表示这是一个IO地址空间。

- 主机先读取BAR,获取BAR的类型。图中未画出。

- 主机向BAR的所有bit写1,此时BAR中可以写入的bit变为1,不可写入bit的保持原来的值。图中bit[31-8]=1,表示该BAR请求的存储地址空间大小为2^8=256B。

- 主机获取这些信息后,向BAR中配置IO地址空间的基地址。图中配置的是0x4000,bit[7-0]保持为0,即该BAR表示的IO地址空间范围为0x4000-0x40FF,大小为256B。

早期的IO设备内部寄存器只能通过IO地址空间进行访问,但是这种方式局限性很大,而且效率低。后来为了提高灵活性和效率,将IO设备内部寄存器统一映射到存储地址空间,使用MMIO方式访问IO设备内部寄。PCIe为了兼容PCI,保留了IO地址空间,但现在很少使用。

4.Type 1 Header

Type 1配置空间用来描述PCIe桥,PCIe桥除了作为PCIe设备之外,还需要管理其下面连接的PCIe子总线使用的各类资源。Type 1配置空间头如下图所示。

每个字段的具体意义如下:

| 字段 | 意义 | 偏移地址 | 宽度 |

|---|---|---|---|

| Vendor ID | 厂商ID,由PCI-SIG统一分配,如Intel的厂商ID为0x8086, | 0x00 | 2B |

| Device ID | 设备ID,由PCI-SIG统一分配,如Intel 82571EB网卡的设备ID为0x105E | 0x02 | 2B |

| Command | 命令寄存器,初始化的时候默认值为0,具体见下面的解释 | 0x04 | 2B |

| Status | 保存PCIe状态 | 0x06 | 2B |

| Revision ID | 保存PCIe的版本号 | 0x08 | 1B |

| Class Code | 保存PCIe设备的分类,由Base Class Code、Sub Class Code和Interface组成。Base Class Code是设备的基本分类,如显卡、网卡、PCIe桥等设备。Sub Class Code则会将设备进一步细分。Interface定义编程接口。 | 0x09 | 3B |

| Cache Line Size | 保存主机处理器的Cache行长度,该寄存器由主机的系统软件设置。若PCIe设备不支持与Cache相关的总线事务,系统软件可不设置该寄存器。 | 0x0C | 1B |

| Primary Latency Timer | 上游总线的延迟时间,对PCIe总线无意义。 | 0x0D | 1B |

| Header Type | 记录设备的类型。bit[7]=0表示单功能设备,bit[7]=1表示多功能设备,bit[6:0]=0表示PCIe Agent设备,bit[6:0]=1表示PCIe桥设备,bit[6:0]=2表示PCIe CardBus桥。 | 0x0E | 1B |

| BIST | 可选,用于内部自检 | 0x0F | 1B |

| Base Address 0 | BAR寄存器,保存主机分配给桥的PCIe域地址,64位地址使用2个BAR | 0x10 | 4B |

| Base Address 1 | BAR寄存器,保存主机分配给桥的PCIe域地址,64位地址使用2个BAR | 0x14 | 4B |

| Primary Bus Number | 保存该PCIe桥的上游PCIe总线号 | 0x18 | 1B |

| Secondary Bus Number | 保存桥的下游总线中总线编号最小的PCIe总线号 | 0x19 | 1B |

| Subordinate Bus Number | 保存桥的下游总线中总线编号最大的PCIe总线号 | 0x1A | 1B |

| Secondary Latency Timer | Secondary总线的延迟时间,对PCIe总线无意义。 | 0x1B | 1B |

| I/O Base | 保存桥的下游总线连接的所有PCIe设备IO地址空间的基地址。若桥没有实现I/O地址空间,则应该只读并且返回0,反之高4位可以修改 | 0x1C | 1B |

| I/O Limit | 保存桥的下游总线连接的所有PCIe设备IO地址空间的大小。若桥没有实现I/O地址空间,则应该只读并且返回0,反之高4位可以修改 | 0x1D | 1B |

| Secondary Status | 记录Secondary总线的状态 | 0x1E | 2B |

| Memory Base | 保存桥的下游总线连接的所有PCIe设备非预取存储地址空间的基地址 | 0x20 | 2B |

| Memory Limit | 保存桥的下游总线连接的所有PCIe设备非预取存储地址空间的大小 | 0x22 | 2B |

| Prefetchable Memory Base | 保存桥的下游总线连接的所有PCIe设备预取存储地址空间的基地址 | 0x24 | 2B |

| Prefetchable Memory Limit | 保存桥的下游总线连接的所有PCIe设备预取存储地址空间的大小 | 0x26 | 2B |

| Prefetchable Base Upper 32 Bits | 保存桥的下游总线连接的所有PCIe设备预取存储地址空间基地址的高32位 | 0x28 | 4B |

| Prefetchable Limit Upper 32 Bits | 保存桥的下游总线连接的所有PCIe设备预取存储地址空间大小的高32位 | 0x2C | 4B |

| I/O Base Upper 16 Bits | 保存桥的下游总线连接的所有PCIe设备IO地址空间基地址的高16位。若桥没有实现I/O地址空间,则应该只读并且返回0 | 0x30 | 2B |

| I/O Limit Upper 16 Bits | 保存桥的下游总线连接的所有PCIe设备IO地址空间大小的高16位。若桥没有实现I/O地址空间,则应该只读并且返回0 | 0x32 | 2B |

| Capability Pointer | Capabilities寄存器相对于配置空间的偏移地址,PCI-X和PCIe必须支持该功能 | 0x34 | 1B |

| Reserved | 保留 | 0x35 | 3B |

| Expansion ROM Base Address | 固件程序地址,用于初始化PCIe桥 | 0x38 | 4B |

| Interrupt Line | 保存当前PCIe设备使用的中断向量号,由主机系统软件分配,通常不使用 | 0x3C | 1B |

| Interrupt Pin | 保存PCIe设备使用的中断引脚,由主机系统软件分配,1表示INTA#,2表示INTB#,3表示INTC#,4表示INTD#,PCIe设备可使用INTx模拟INTA~D#中断 | 0x3D | 1B |

| Bridge Control | 控制桥的寄存器,最终要的是bit[6](Secondary Bus Reset), 当bit[6]=1时,PCIe桥将对该port下面连接的所有PCIe设备/桥发起hot reset。 | 0x3E | 2B |

4.1.Base Address

Type 1设备中只含有两个BAR,其意义和Type 0中的BAR寄存器相同。但在Type 1表示的PCIe桥中,这两个BAR寄存器是可选的,如果桥设备不存在私有寄存器,可以不使用这两个BAR寄存器。不存在私有寄存器,且没有专门驱动的PCIe桥,被称为透明桥。

4.2.I/O地址空间

I/O Base、I/O Limit、I/O Base Upper 16 Bits和I/O Limit Upper 16 Bits共同决定了桥的下游总线IO地址空间范围。计算方法如下图所示:

- I/O Base和I/O Limit的低2位决定了IO地址是16位还是32位,若是32位则需要使用I/O Base Upper 16 Bits和I/O Limit Upper 16 Bits。

- I/O Base表示I/O地址空间基地址,按4KB对齐,低12位都是0,因此图中的I/O基地址为0x4000。

- I/O Limit表示I/O地址空间最大地址,低12位都是1,即为0xFFF。因此图中的I/O地址空间最大地址为0x4FFF。

- 图中I/O地址空间为16位,因此I/O地址空间范围为0x4000-0x4FFF。

4.3.非预取地址空间

Memory Base和Memory Limit共同决定了非预取地址空间的范围。计算方法如下图所示:

- Memory Base和Memory Limit低4位只读,默认为0,非预取地址空间默认为32位。

- Memory Base表示非预取地址空间基地址,按1MB对齐,即低20位为0。

- Memory Limit表示非预取地址空间最大地址,低20位都为1,即为0xFFFFF。

- 因此非预取地址空间范围为0xF9000000-0xF90FFFFF。

4.4.预取地址空间

Prefetchable Memory Base、Prefetchable Memory Limit、Prefetchable Base Upper 32 Bits和Prefetchable Limit Upper 32 Bits共同决定了预取地址空间的范围。计算方法如下图所示:

- Prefetchable Memory Base和Prefetchable Memory Limit低4位只读,而且决定了预取地址空间是32位还是64位,0x0表示32位,0x1表示64位。若是64位地址,则需要使用Prefetchable Base Upper 32 Bits和Prefetchable Limit Upper 32 Bits。

- Prefetchable Memory Base表示预取地址空间基地址,按1MB对齐,即低20位为0。

- Prefetchable Memory Limit表示预取地址空间最大地址,低20位都为1,即为0xFFFFF。

- 图中预取地址空间为64位,因此I/O地址空间范围为0x240000000-0x243FFFFFF。

5.Capabilities Structures

Capabilities Structures主要有MSI、MSI-X、PCI Express、电源、AER、PCI Express Extended等Capabilities Structures。第一个Capabilities Structures的地址由配置空间Header的Capabilities Pointer寄存器保存,系统可以根据此遍历所有的Capabilities Structures。Capabilities Structures的链表如下图所示。

每一个Capabilities Structures都有一个独一无二的Capability ID,该ID保存在Capabilities Structures的开始地址,系统软件根据此判断Capabilities Structures的类型。

PCI标准Capabilities ID如下图所示。

PCIe扩展Capabilities ID参考PCI Express® Base Specification Revision 5.0的9.3.7节。

5.1.MSI Capability Structures

MSI使用报文的形式向主机发送中断。具体是使用存储器写请求,向MSI Capability Structures中的Message Address写入Message Data,写入后会在主机侧触发中断。

MSI最多支持32个中断,且要求主机分配的中断号连续。MSI Capability Structures共有4种形式,分别是32位和64位不带中断Mask和Pending Structure,32位和64位带中断Mask和Pending Structures,具体如下图所示。

MSI Capability Structures各个寄存器的定义如下表所示:

| 定义 | 描述 | 属性 |

|---|---|---|

| Capability ID | 记录MSI Capability的ID号,值为0x05 | RO |

| Next Capability Pointer | 存放下一个Capability Structure的偏移地址,0x00表示该Capability是最后一个 | RO |

| Message Control | 存放Function使用MSI机制进行中断请求的状态与控制信息 | - |

| Message Address | 存放MSI存储器写事务目的地址的低32位,bit[1:0]为0,4字节对齐,该地址由系统软件分配并设置 | RW |

| Message Upper Address | 存放MSI存储器写事务目的地址的高32位,该地址由系统软件分配并设置 | RW |

| Message Data | 存放MSI存储器写事务携带的数据。总共4字节,Message占低2字节,若扩展Message数据使能,则高2字节为扩展Message数据,否则为0。当只有一个MSI中断(Multiple Message Enable=0)时,Message表示一个真实的数据,Function不会改变Message。当有多个MSI中断(Multiple Message Enable>0)时,Message表示Function可以改变Message低位的bit数,以产生不同的中断,比如当Multiple Message Enable=2时,表示Function需要4个中断,则Function可以修改Message的bit[1]和bit[0],以区分4个中断 | RW |

| Extended Message Data | 存放MSI存储器写事务携带的数据。总共4字节,Message占低2字节,若扩展Message数据使能,则高2字节为扩展Message数据,否则为0 | RW/undefined/RsvdP |

| Mask Bits | 存放MSI中断屏蔽位。系统软件可以向某个bit写1,此时会将对应的中断禁止,清零时会使能对应的中断 | RW |

| Pending Bits | 存放MSI中断Pending位。当Function中断发生时,根据中断号会将对应的bit设置为1 | RO |

Message Control寄存器位域如下图所示:

Message Control寄存器位域的定义如下表所示:

| 位域 | 定义 | 描述 | 属性 |

|---|---|---|---|

| 15:11 | RsvdP | 保留 | - |

| 10 | Extended Message Data Enable | 扩展Message数据使能位,系统软件需要先读取Extended Message Data Capable判断Function是否支持扩展Message数据,若支持再判断是否使能该位 | RW/RO |

| 9 | Extended Message Data Capable | Function是否支持扩展Message数据 | RO |

| 8 | Per-Vector Masking Capable | Function是否支持MSI中断Mask和Pending。0表示不支持,1表示支持 | RO |

| 7 | 64-bit Address Capable | Function是否支持64位地址Structure。0表示只支持32位地址Structure,1表示支持64位地址Structure | RO |

| 6:4 | Multiple Message Enable | 该位域保存系统软件给Function实际分配的MSI中断数量。系统软件先读取Multiple Message Capable位确定Function请求的中断数量,然后再分配。通常情况下两者相等,若系统中断数量不足,则Multiple Message Enab可能会小于Multiple Message Capable | RW |

| 3:1 | Multiple Message Capable | Function需要的中断向量数量,按2的n次方对齐,如0表示需要1个中断向量,1表示需要2个中断向量,…,5表示需要32个中断向量,6和7保留。若设备实际上需要3个中断,则需要设置为2。系统软件根据此位域给Function分配MSI中断数量 | RO |

| 0 | MSI Enable | MSI中断机制使能位,当MSI或MSI-X使能时,INTx中断将被自动禁止 | RW |

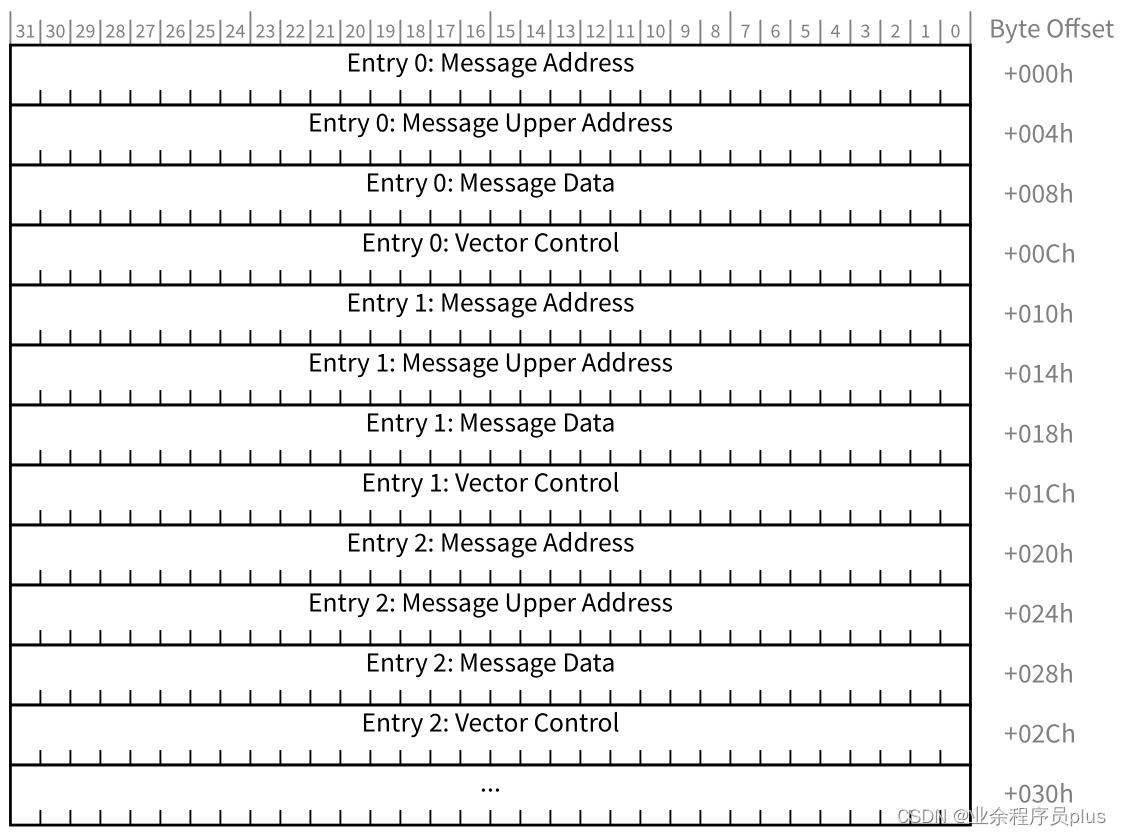

5.2. MSI-X

MSI-X的中断机制和MSI类似,都是向主机的某个地址写Message数据以产生中断。但MSI-X每一个中断都有独立的Message Address和Message Data,Message Address和Message Data组成一个中断向量表,同时MSI-X使用了独立的中断Pending表。中断向量表和中断Pending表存放在BAR空间中。因此MSI-X支持的中断数量更多,且不需要中断号连续。

5.2.1.MSI-X Capability Structures

MSI-X Capability Structures主要的作用是记录中断向量表和Pending表保存的位置。MSI-X Capability Structure如下图所示。

MSI Capability Structures各个寄存器的定义如下表所示:

| 定义 | 描述 | 属性 |

|---|---|---|

| Capability ID | 记录MSI-X Capability的ID号,值为0x11 | RO |

| Next Capability Pointer | 存放下一个Capability Structure的偏移地址,0x00表示该Capability是最后一个 | RO |

| Message Control | 存放Function使用MSI-X机制进行中断请求的状态与控制信息 | - |

| Table BIR | 表示MSI-X中断向量表存放在那个BAR空间中,0-5与BAR0-5对应,若是64位的BAR,则表示低32位BAR的编号 | RO |

| Table Offset | 表示该MSI-X中断向量表在对应BAR空间中的偏移地址,偏移地址为32位,低3位为0,按8字节对齐 | RO |

| PBA BIR | 表示MSI-X中断Pending表存放在那个BAR空间中,0-5与BAR0-5对应,若是64位的BAR,则表示低32位BAR的编号。通常情况下中断向量表和中断Pending表存放在同一个BAR空间中 | RO |

| PBA Offset | 表示该MSI-X中断Pending表在对应BAR空间中的偏移地址,偏移地址为32位,低3位为0,按8字节对齐 | RO |

Message Control寄存器位域如下图所示:

Message Control寄存器位域的定义如下表所示:

| 位域 | 定义 | 描述 | 属性 |

|---|---|---|---|

| 15 | MSI-X Enable | MSI-X中断机制使能位,当MSI、MSI-X和INTx中断只能使用其中一个 | RW |

| 14 | Function Mask | MSI-X中断全局Mask位,当此位为1时,无论Pending表如何设置,所有中断都会被屏蔽 | RO |

| 13:11 | Reserved | 保留 | RsvdP |

| 10:0 | Table Size | MSI-X中断向量表的大小,存放Message Address和Message Data。若系统软件读取的值为0x3,则中断向量表的大小为4字节。 | RO |

5.2.2.MSI-X Table

MSI-X Table如下图所示。每一个Entry表示一个MSI-X中断向量,占用16字节。一个Entry由4部分组成,分别是Message Address、Message Upper Address、Message Data、Vector Control。

MSI-X Table每个Entry的寄存器定义如下表所示:

| 定义 | 描述 | 属性 |

|---|---|---|

| Message Address | 存放MSI存储器写事务目的地址的低32位,bit[1:0]为0,4字节对齐,该地址由系统软件分配并设置 | RW |

| Message Upper Address | 存放MSI存储器写事务目的地址的高32位,如果为0,则使用32地址,否则使用64位地址,该地址由系统软件分配并设置。 | RW |

| Message Data | 存放MSI存储器写事务携带的数据,总共4字节 | RW |

| Vector Control | 控制该中断entry的行为 | - |

Vector Control寄存器位域如下图所示:

Vector Control寄存器位域定义如下表所示:

| 位域 | 定义 | 描述 | 属性 |

|---|---|---|---|

| 31:24 | ST Upper | 如果Function实现了TPH Requester Extended Capability而且ST表位域值为10b,同时Extended TPH Requester Supported位为1,则ST Upper保存了高8位的Steering Tag,可以读写,否则保留 | RW or Rsvd |

| 23:16 | ST Lower | 如果Function实现了TPH Requester Extended Capability而且ST表位域值为10b,则ST Lower保存了低8位的Steering Tag,可以读写,否则保留 | RW or Rsvd |

| 15:1 | Reserved | 保留 | RW or RsvdP |

| 0 | Mask Bit | 中断屏蔽位,为1屏蔽该MSI-X中断,为0时可以正常发送MSI-X中断,默认值为1 | RW |

5.2.3.MSI-X PBA

MSI-X中断Pending Table如下图所示。每一个Entry由64位组成,其中每一位与MSI-X中断表中的一个Entry对应,则一个Entry和MSI-X中断表的64个Entry对应。当Pending Table中的某一个bit置1时,表明与之对应的MSI-X中断发生了。

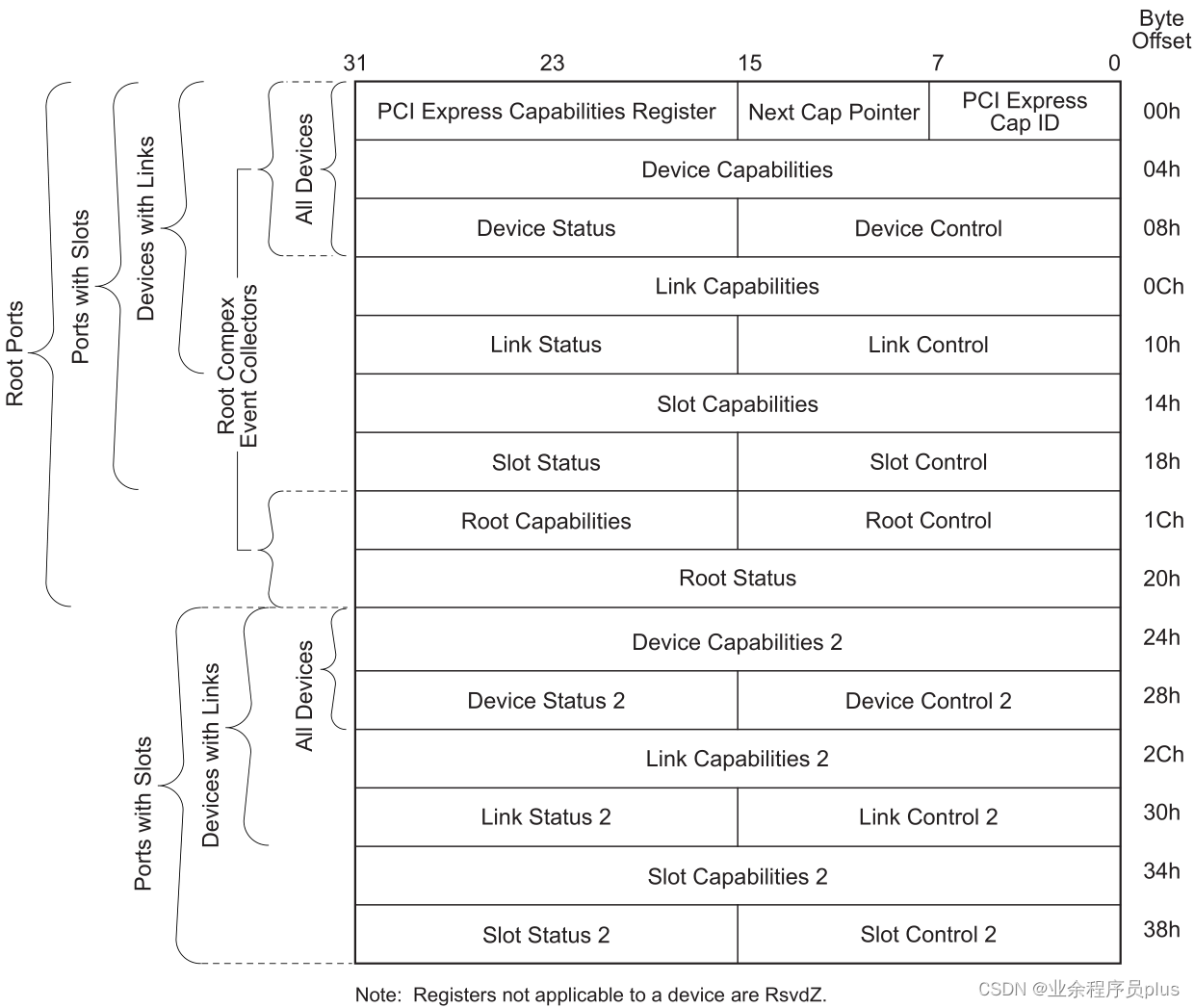

5.3.PCI Express Capability Structure

PCI Express Capability Structure存放和PCIe总线相关的信息,包括PCIe链路、插槽、设备状态、是否支持PCIe新特性等信息。PCI Express Capability Structure整体的Structure如下图所示。

所有PCIe设备Functions必须实现PCI Express Capabilities、Device Capabilities、Device Status和Device Control寄存器。PCIe设备Functions选择实现Device Capabilities 2、Device Status 2和Device Control 2寄存器,若没有实现,则保持为0。

Root Ports、Switch Ports、Bridges和Endpoints(非RCiEPs)必须实现Link Capabilities、Link Status、Link Control、Link Capabilities 2, Link Status 2和Link Control 2寄存器,Functions无需实现上述寄存器,保持为0即可。

Switch Downstream和Root Ports选择实现Slot Capabilities、Slot Status和Slot Control寄存器。如果port连接了插槽,则必须实现Slot Capabilities寄存器,如果port连接了插槽或者Data Link Layer Link Active Reporting Capable位设置,则必须实现Slot Status和Slot Control寄存器。Functions无需实现上述寄存器,保持为0即可。Switch Downstream和Root Ports选择实现Slot Capabilities 2、Slot Status 2和Slot Control 2寄存器,Functions无需实现上述寄存器,保持为0即可。

Root Ports and Root Complex Event Collectors必须实现Root Capabilities, Root Status, and Root Control寄存器,Functions无需实现上述寄存器,保持为0即可。

下面只介绍比较重要的寄存器。

5.3.1.PCI Express Capabilities Register

PCI Express Capabilities寄存器记录了PCIe设备Function类型及相关的capabilities,位域如下图所示。

PCI Express Capabilities位域的定义如下表所示:

| 位域 | 定义 | 描述 | 属性 |

|---|---|---|---|

| 14 | Undefined | PCIe5.0之前的版本表示是否支持TCS Routing,PCIe5.0未定义 | RO |

| 13:9 | Interrupt Message Number | 使用MSI或MSI-X中断的编号。当Slot Status或Root Status寄存器的状态发生变化时,该PCIe设备可以通过MSI或MSI-X中断通知主机。 | RO |

| 8 | Slot Implemented | 该位为1时表示当前port连接了PCIe插槽。对下行port有效,对上行port无效 | HwInit |

| 7:4 | Device/Port Type | 保存PCIe Function类型,对于多Function的设备,Function类型可能不相同。Type 0配置空间头:0x0表示PCI Express Endpoint,0x1表示Legacy PCI Express Endpoint,0x9表示RCiEP,0xA表示Root Complex Event Collector。Type 1配置空间头:0x4表示Root Port of PCI Express Root Complex,0x5表示Upstream Port of PCI Express Switch,0x6表示Downstream Port of PCI Express Switch,0x7表示PCI Express to PCI/PCI-X Bridge,0x8表示PCI/PCI-X to PCI Express Bridge | RO |

| 3:0 | Capability Version | 保存PCI-SIG定义的PCI Express Capability structure版本编号 | RO |

5.3.2.Device Capabilities Register

Device Capabilities寄存器记录了PCIe设备Function特有的capabilities,位域如下图所示。

Device Capabilities寄存器位域的定义如下表所示:

| 位域 | 定义 | 描述 | 属性 |

|---|---|---|---|

| 28 | Function Level Reset Capability | 是否支持FLR | RO |

| 27:26 | Captured Slot Power Limit Scale | 上行port最大功耗系数,0x0表示1.0,0x1表示0.1,0x2表示0.01,0x3表示0.001 | RO |

| 25:18 | Captured Slot Power Limit Value | 上行port最大功耗,和Captured Slot Power Limit Scale一起使用 | RO |

| 16 | ERR_COR Subclass Capable | 是否支持ERR_COR Subclass | RO |

| 15 | Role-Based Error Reporting | 是否支持错误上报 | RO |

| 14:12 | Undefined | 未定义 | RO |

| 11:9 | Endpoint L1 Acceptable Latency | 退出L1状态所能接收的延时。0x0表示最大1us,0x1表示最大2us,0x2表示最大4us,0x3表示最大8us,0x4表示最大16us,0x5表示最大32us,0x6表示最大64us | RO |

| 8:6 | Endpoint L0s Acceptable Latency | 退出L0s状态所能接收的延时。0x0表示最大64ns,0x1表示最大128ns,0x2表示最大256ns,0x3表示最大512ns,0x4表示最大1us,0x5表示最大2us,0x6表示最大4us | RO |

| 5 | Extended Tag Field Supported | 表示最大支持的Tag长度,0x0表示支持5bit,0x1表示支持8bit | RO |

| 4:3 | Phantom Functions Supported | 是否支持Phantom Functions | RO |

| 2:0 | Max_Payload_Size Supported | 保存了TLP包中数据包的最大长度。0x0表示128字节,0x1表示256字节,0x2表示512字节,0x3表示1024字节,0x4表示2028字节,0x5表示4096字节。 | RO |

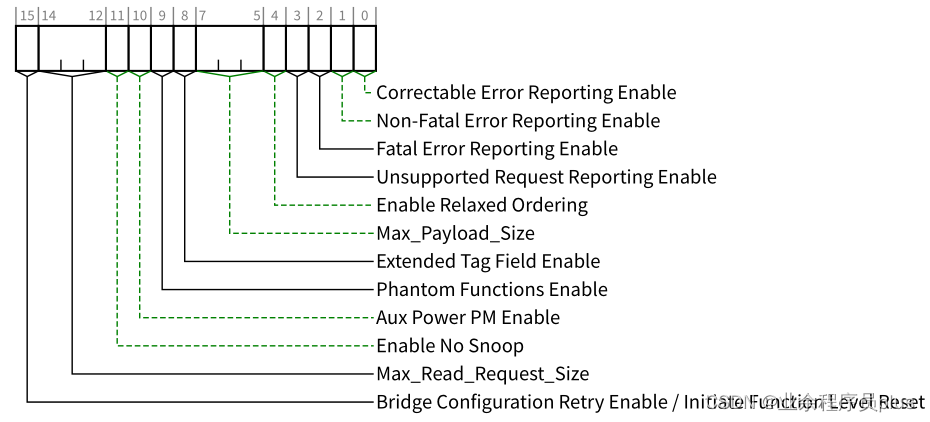

5.3.3.Device Control Register

Device Control寄存器的位域如下图所示,主要用于设置MPS(Max_Payload_Size)、MRRS(Max_Read_Request_Size)。

5.4.PCI Express Extended Capabilities

PCI Express Extended Capabilities保存在配置空间的100h-FFFh中。PCI Express Extended Capabilities只能通过EACM访问。PCI Express Extended Capabilities布局如下图所示,详细信息可以参考PCIe Space文档。

Linux中访问PCI Express Extended Capabilities的代码如下所示。

[include/uapi/linux/pci_regs.h]

#define PCI_CFG_SPACE_SIZE 256

#define PCI_CFG_SPACE_EXP_SIZE 4096

[drivers/pci/pci.c]

int pci_find_next_ext_capability(struct pci_dev *dev, int start, int cap)

{

u32 header;

int ttl;

int pos = PCI_CFG_SPACE_SIZE;

/* minimum 8 bytes per capability */

ttl = (PCI_CFG_SPACE_EXP_SIZE - PCI_CFG_SPACE_SIZE) / 8;

if (dev->cfg_size <= PCI_CFG_SPACE_SIZE)

return 0;

if (start)

pos = start;

if (pci_read_config_dword(dev, pos, &header) != PCIBIOS_SUCCESSFUL)

return 0;

/*

* If we have no capabilities, this is indicated by cap ID,

* cap version and next pointer all being 0.

*/

if (header == 0)

return 0;

while (ttl-- > 0) {

if (PCI_EXT_CAP_ID(header) == cap && pos != start)

return pos;

pos = PCI_EXT_CAP_NEXT(header);

if (pos < PCI_CFG_SPACE_SIZE)

break;

if (pci_read_config_dword(dev, pos, &header) != PCIBIOS_SUCCESSFUL)

break;

}

return 0;

}

PCIe的配置空间内容很多,且版本升级后又会增加。上述只介绍了配置空间中比较常见的内容,详细内容需要参考最新的PICe Spec文档。

参考资料

- PCIEXPRESS体系结构导读

- PCI Express technology 3.0

- PCI_Express_Base_r3.0_10Nov10

- PCI-to-PCI Bridge Architecture Specification Revision 1.1

- https://blog.csdn.net/qq_42208449/article/details/132475653

- PCI Express® Base Specification Revision 5.0 Version 1.0

![[Collection与数据结构] 二叉树(三):二叉树精选OJ例题(下)](https://img-blog.csdnimg.cn/direct/4f296d76b5234dd18709cd687cfdb8d3.png)

![Redis集合[持续更新]](https://img-blog.csdnimg.cn/img_convert/3e662e81235cf3e798d531d15fe67c77.png)