Zynq 7000系列SoC器件通过标准JTAG调试接口提供调试访问。在内部,SoC设备器件在处理系统(PS)内部实现了一个Arm调试访问端口(DAP),同时在可编程逻辑(PL)内部实现了一个标准的JTAG测试访问端口(TAP)控制器。作为Arm CoreSight调试架构的一部分,Arm DAP允许用户利用行业标准的第三方调试工具。

除了标准JTAG功能外,AMD TAP控制器还支持一系列PL功能,包括PL调试、eFuse/BBRAM编程、片上XADC访问等。最重要的是,它还允许通过TAP同时使用跟踪缓冲区和PS与PL之间的交叉触发接口,对Arm软件和PL硬件进行调试。

Zynq 7000 SoC包含的另一个重要的调试特性是调试跟踪支持。这一特性允许用户将PS和PL的跟踪捕获到一个公共跟踪缓冲区中,该缓冲区要么通过下文描述的JTAG读出,要么通过跟踪端口接口单元(TPIU)发送出去。

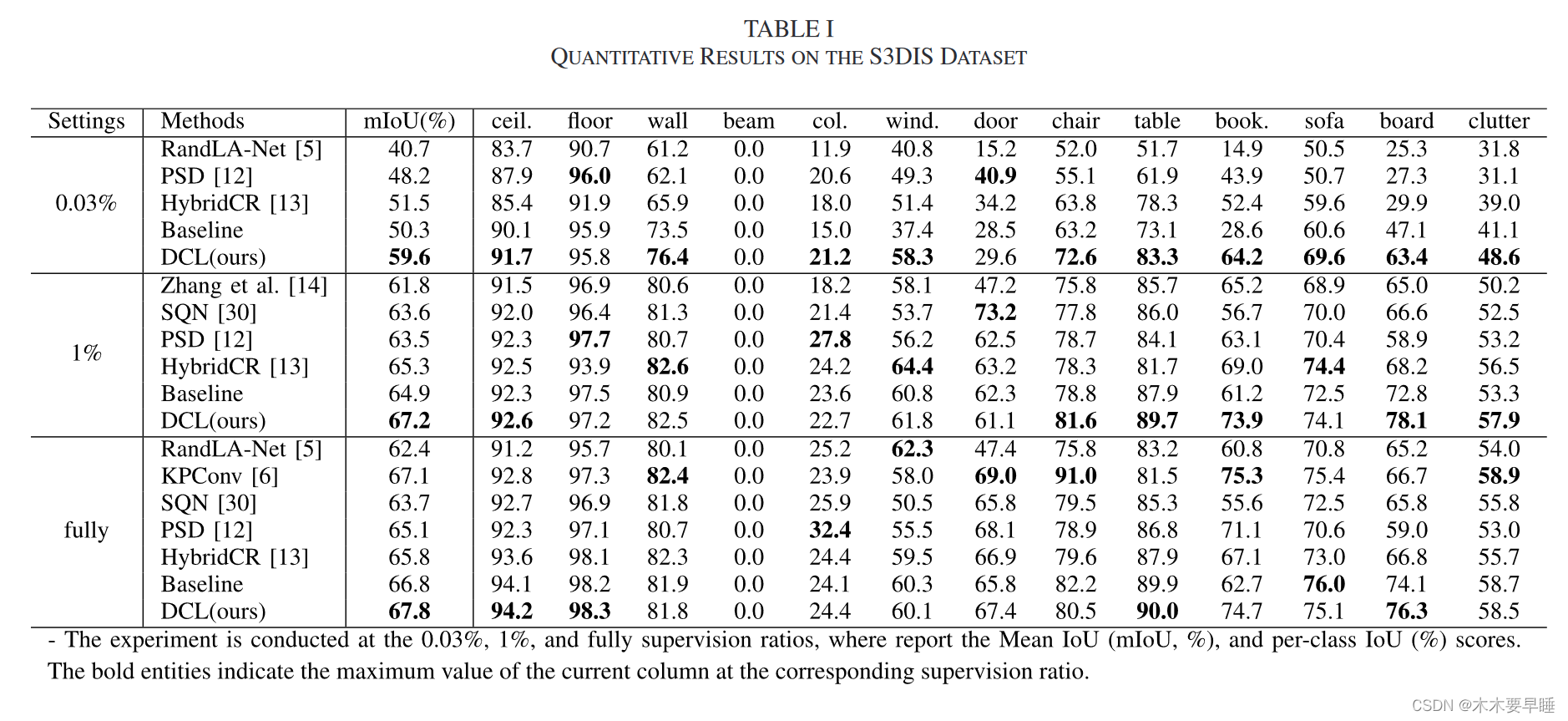

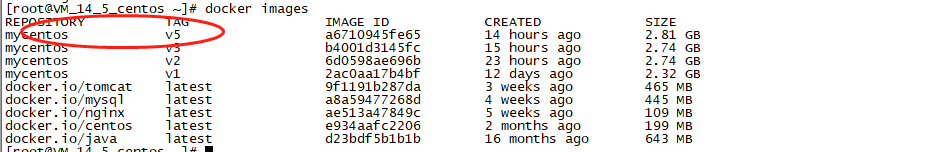

一、框图

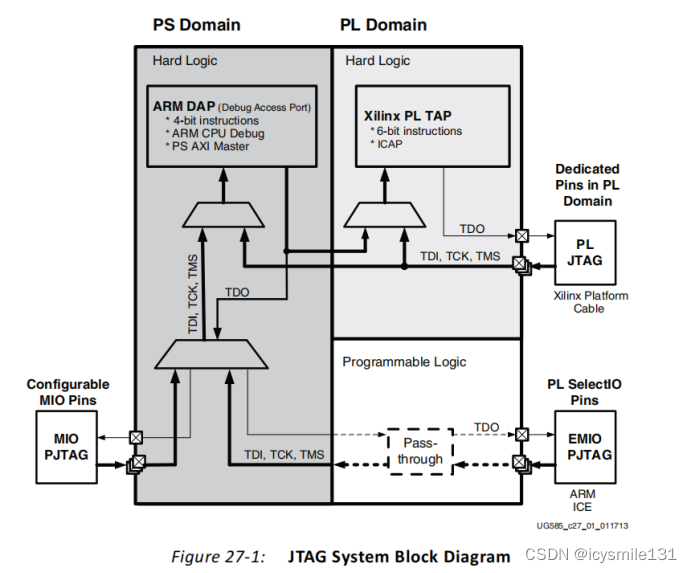

上图展示了顶层DAP/TAP架构。一旦BootROM将控制权传递给用户软件,假设是非安全启动过程,JTAG链将自动启用。这允许从用户软件入口点进行调试。

JTAG支持两种不同模式:级联JTAG模式(也称为单链模式)和独立JTAG模式(也称为分链模式)。模式是在系统复位解除时通过模式输入确定的。

在级联JTAG链模式下,TAP和DAP都可以从外部JTAG调试工具或JTAG测试仪访问。尽管PL侧有专用的PL_TDO/TMS/TCK/TDI I/O,但只能连接一根JTAG电缆,并且可以同时访问PS和PL功能。为了使用单独的电缆同时调试Arm软件和PL设计,用户必须切换到独立JTAG模式。在这种模式下,JTAG电缆只能从专用的PL_TDO/TMS/TCK/TDI引脚看到AMD TAP控制器。为了调试Arm软件,用户可以将Arm DAP信号(PJTAG)通过MIO或EMIO路由到PL SelectIO引脚。

要使用JTAG调试,PS和PL都必须上电。出于安全原因,JTAG链受到三重冗余门控逻辑的保护,以防止由于单一事件扰动(SEU)而在安全环境下意外启用调试。Zynq 7000 SoC设备还提供JTAG禁用锁定功能,以防止由于软件错误而启用调试。

Zynq 7000 SoC提供了使用一个eFuse位记录来永久禁用JTAG的功能。在选择此选项时应谨慎,因为eFuse JTAG禁用是不可逆的。

二、跟踪端口接口单元(TPIU)

是用于将实时跟踪信息转储到外部跟踪捕获模块的跟踪接收器模块之一。为了监控更长时间的跟踪信息,必须启用TPIU通过MIO或EMIO进行转储,以便跟踪信息被外部跟踪捕获设备捕获,例如HP逻辑分析仪、Lauterbach Trace32、Arm DStream等。

三、特征

• 支持JTAG 1149.1边界扫描

• 两个符合1149.1标准的TAP控制器:一个JTAG TAP控制器和一个Arm DAP

• Zynq 7000系列器件的AMD TAP提供单一独特的IDCODE

• 支持IEEE 1532在系统可编程(ISC)设备编程

eFuse编程

BBRAM编程

XADC访问

板上闪存编程

• 支持AMD ChipScope调试

• 使用Arm DAP进行Arm CoreSight调试中心控制

• 通过DAP-AP端口间接访问PS地址空间

• 使用PS中的MIO或PL中的EMIO进行外部跟踪捕获

这些功能使得JTAG调试接口在开发、测试和调试过程中能够提供强大的支持和灵活性。通过JTAG接口,开发人员可以访问和控制设备的内部状态,捕获和分析系统的行为,从而更有效地进行调试和优化工作。此外,它还支持多种在系统可编程设备的编程,为设备配置和定制化提供了便利。

四、功能

Arm DAP和JTAG TAP控制器以菊花链方式连接,其中Arm DAP位于链的前端。这两个JTAG控制器属于两个不同的电源域。Arm DAP位于PS(处理系统)电源域中,而TAP则位于PL(可编程逻辑)电源域中。JTAG I/O焊盘位于PL电源域中,以便利用PL中现有的JTAG I/O焊盘。尽管PS支持PL掉电模式,但为了支持所有与JTAG相关的功能,这两个电源域都必须上电。

在独立模式下,用户可以同时访问TAP和Arm DAP控制器。出于安全原因,当PS复位解除时,Arm DAP控制器将被旁路。位于PL中的AMD TAP控制器可以通过eFuse或PL配置逻辑中的控制寄存器进行禁用。

PS内的所有调试组件都直接受调试工具的控制,如Arm RVDS或AMD XDK,通过Arm DAP进行。PS内的所有调试组件(包括DAP)均按照Arm CoreSight架构设计和集成。尽管PL内没有CoreSight组件,但PS内的FTM组件允许将PL跟踪转储到ETB中。CTI/CTM支持PS和PL之间的交叉触发。

所有PS(处理系统)调试组件都与调试APB(高级外设总线)相连,而DAP(调试访问端口)作为唯一的总线主设备。通过JTAG连接到Arm DAP的外部调试工具使用调试APB总线来配置所有调试组件,包括CPU、CTI/CTM、PTM、ITM和FTM。

PL中的AMD TAP控制器具有四个主要目的:

• 边界扫描测试

• eFuse编程

• BBRAM编程

• PL调试ChipScope。

TPIU提供了长时间捕获跟踪的机制。没有内部时间限制来确定跟踪可以转储多长时间,因此唯一的实际限制是Zynq 7000的带宽。如果使用通过MIO的PS I/O进行跟踪转储,则最大跟踪带宽取决于可以分配多少个MIO跟踪I/O。另一种选择是通过EMIO进行跟踪转储。PL软逻辑将EMIO跟踪信号连接到PL SelectIO。处理EMIO跟踪还有其他潜在的创新方法。

例如,用户可以将EMIO跟踪数据回环到PS,并将其存储在DDR内存中,或者通过千兆以太网导出跟踪以启用远程调试或监控。在典型的调试流程中,用户启用最小的跟踪源转储功能,以适应分配给TPIU的吞吐量中的跟踪数据。在通过跟踪监控确定发生调试的小时间窗口后,如果需要,用户可以启用完全跟踪转储功能,并将短时间的数据存储到ETB中,以便进行下一级的调试。除了调试之外,跟踪端口还为软件分析带来了显著的价值。软件分析有助于用户识别消耗最多CPU功率的软件例程。基于此,用户可以决定是执行软件优化还是将进程卸载到PL。

五、I/O信号

在级联JTAG模式下,对于用户来说,只有PL侧的PL_TDO/TMS/TCK/TDI信号是有意义的。通过这些信号,用户可以访问Arm DAP和AMD TAP。

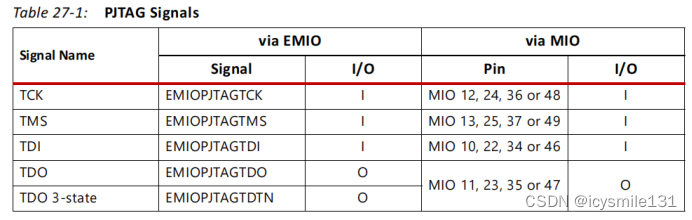

在独立JTAG模式下,用户只能通过PL_TDO/TMS/TCK/TDI信号访问AMD TAP。要访问Arm DAP,用户必须使用PJTAG信号,如表27-1所示。将PJTAG信号路由到芯片引脚输出有两种选择:通过EMIO到PL SelectIO,或者通过MIO。