CACHE 概念

CPU 读写指令或者数据,可能直接从寄存器查取,也可能经过 TLB ,经过 MMU,经过高速缓存,经过内存,经过外部存储器。这里面有一个 Cache 的概念,想多了解下了,于是有这这一篇笔记。

1 生活的例子

例如,我在商场购物时,把要买的东西先把它放到小推车中,最后统一结账。此时,把 自己想象成芯片中的 CPU,购物车是芯片中 Cache,柜台是芯片的输出口。再例如,我在图书馆看书,随手将喜欢看的书放到柜子里,这里某一些书我会反复看,不想看时把书放回书架上。此时,我是 CPU,书柜是 Cache,书架是下一级存储器。

2 Cache 基本概念

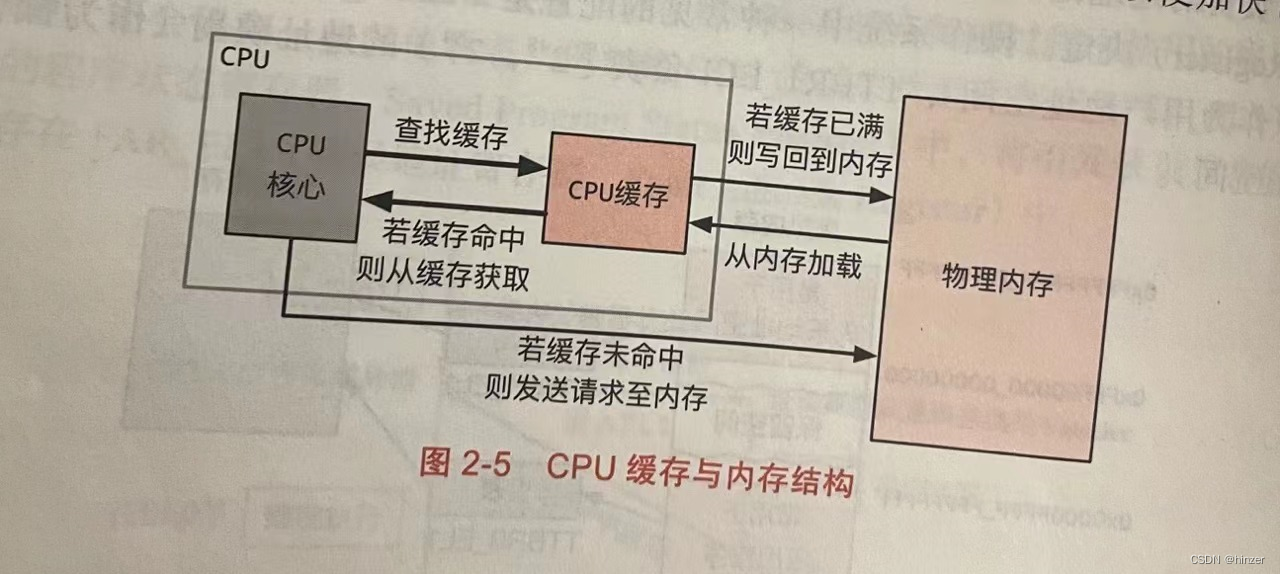

Cache 特指计算机存储子系统中的高速缓存,使用 Cache 能加速 CPU 与主存之间的交互。另外一个说法,在提交结构中为了解决慢速设备加入的一个相对快速的设备就可以是一个 Cache,此时 Cache 泛指 TLB 、MMU、高速缓存。

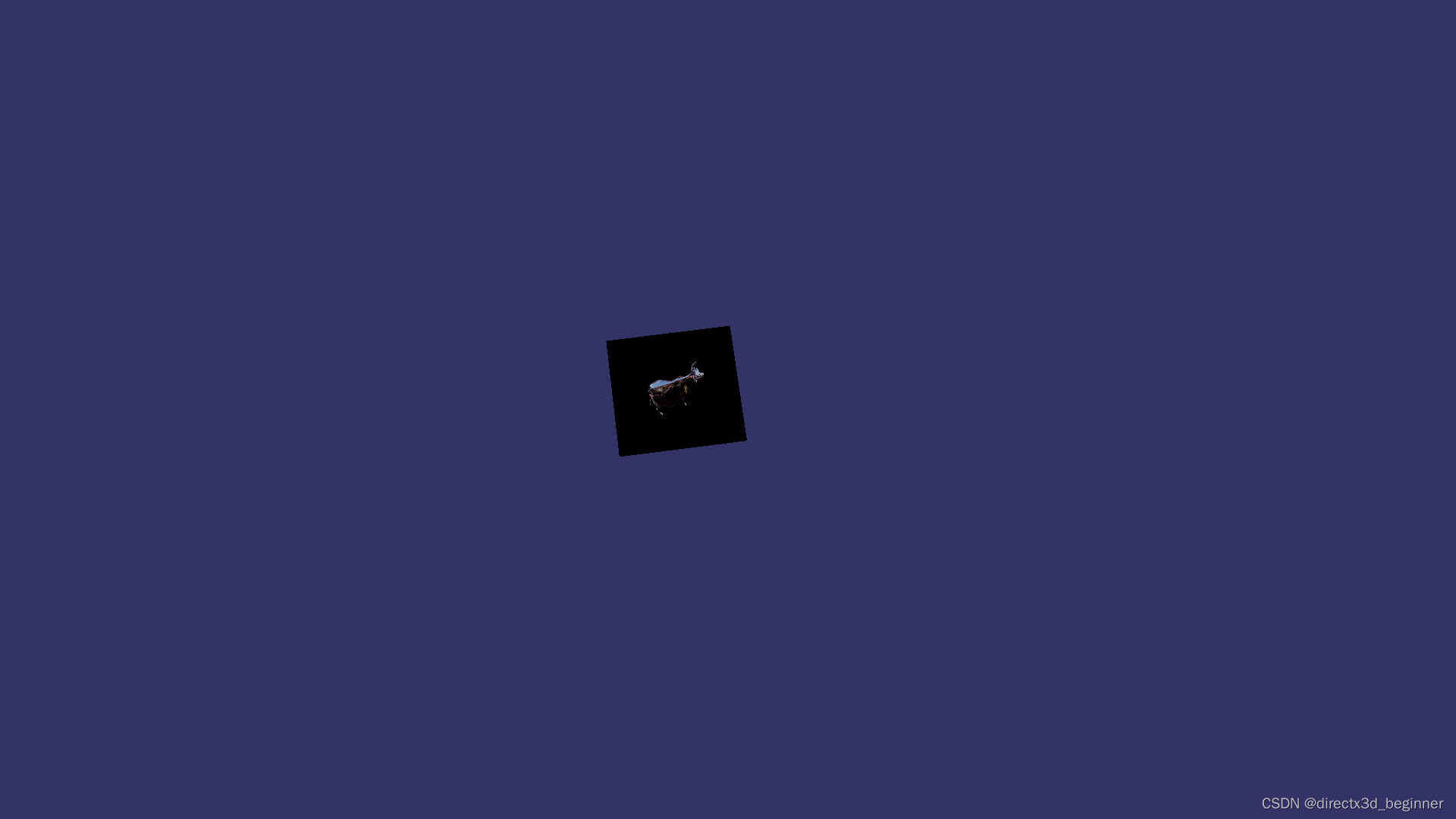

图参考源《现代操作系统:原理与实现》

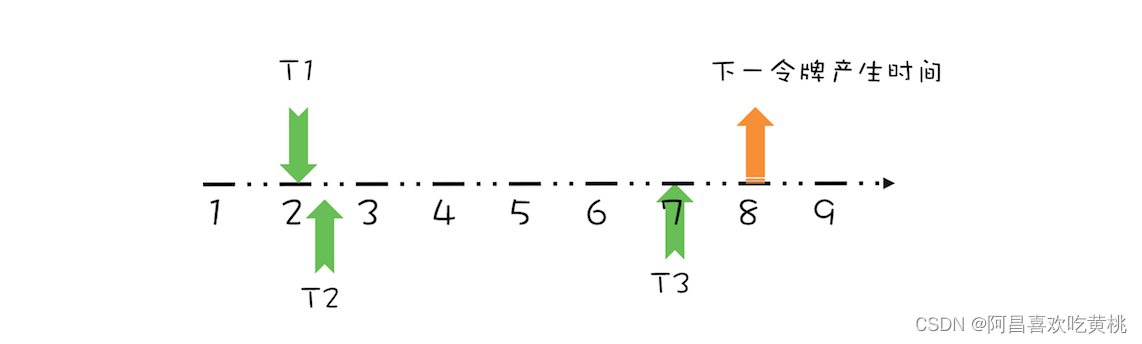

为什么说 Cache 能提高 CPU 的读写速率? 其中一个原因是 Cache 读写本来就快,另一个原因是利用局部性原理(使得 CPU 访问 cache 命中率高)。例如, CPU 要加载(内存上的)数据时,一般会优先查找 Cache

- 如果存在(命中),返回结果值

- 如果不存在(缺失),选择从主存中加载

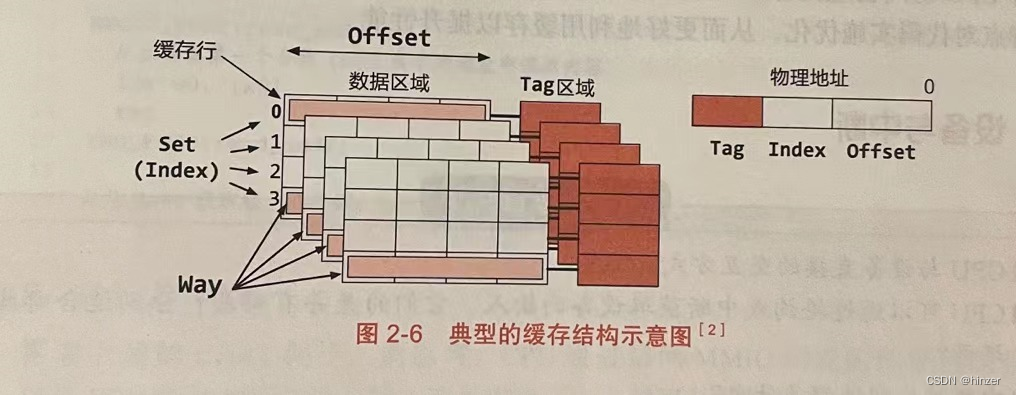

3 Cache 基本结构(内部)

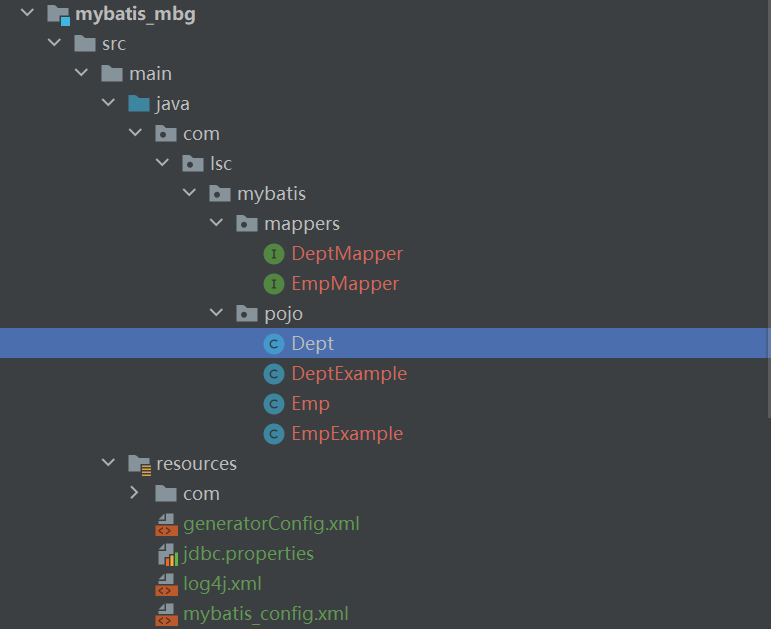

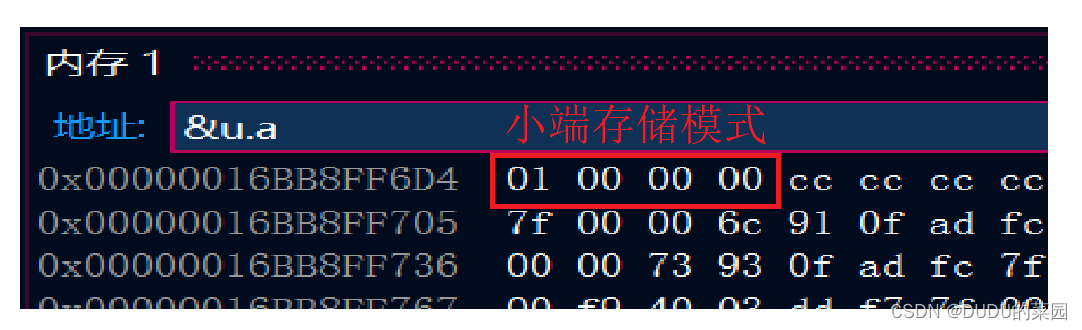

将 cache 看作一张散列表,当前 index 宽度为 3,可以索引 2^3=8 个 Set,当前 offset 宽度为 3 ,表示一个 Cahe Line 有 2^3=8 Byte

图参考源《现代操作系统:原理与实现》

- cache size: cache 的大小

- cache line:cache 分割出的存储单元,cache line 是 cache 和主存之间数据传输的最小单位

- offset: 用于寻址 cache line 中的某一个字节

- index: 用于查找 cache 中的某一个 Set(然后)

- tag: 整个地址位宽去除 index 和 offset 的部分,通过 tag 在 Set 中匹配 cache line

举一个例子

如图,此时 CPU 需要从 0x0654(11001010100) 地址读取一个字节,先通过 index 找到第2组 Cache 区域,然后对比 tag 命中是否命中某一个 Cache Line,如果命中并且该 Cache Line 有效,那么在根据 offset 读取对应的地址。如果没有命中任何 Cache Line 或者命中的 Cache Line 无效,那么缺失的数据将在从下一级的内存中寻找。

| tag | index | offset |

|---|---|---|

| 11001 | 010 | 100 |

Cache 设计模型

- 直接映射缓存(Direct-mapped cache),也叫单路组相连缓存,Set 只有一个 Cache Line

- 多路组相连缓存(N-way Set Associative),Set 有多个 Cache Line

- 全相连缓存(Full associative cache),Set 包含所有 Cache Line

4 参考链接

- Cache的基本原理

- 《现代操作系统:原理与实现》