本文主要介绍以下几点:

- 什么是触发器和锁存器

- 门电路和触发器的区别

- 什么是电平钟控触发器

- 电平钟控触发器触发器和锁存器的区别

- 触发器的分类方式:逻辑功能、触发方式、电路结构、存储数据原理、构成触发器的基本器件

- 寄存器

- 利用移位寄存器实现串并转换或并串转换

目录

- 一、触发器的基本概念

- 二、触发器的分类及原理

- 1.RS触发器

- (1)与非门RS触发器

- (2)或非门RS触发器

- 2.电平触发钟控触发器

- (1)钟控RS触发器

- (2)D触发器

- (3)钟控JK触发器

- (4)钟控T触发器

- 3.边沿触发器

- (1)基本概念

- (2)触发器的应用

- 三、寄存器

- 1.基本结构

- (1)电平触发数据寄存器

- (2)边沿触发数据寄存器

- 2.移位寄存器

- (1)基本结构

- (2)可预置移位寄存器

- (3)四位通用移位寄存器74LS194

- (4)利用移位寄存器实现串/并转换

- (5)利用移位寄存器实现并/串转换

一、触发器的基本概念

触发器(Flip-Flop)是一种具有记忆功能、可以存储二进制信息的双稳态电路,它是组成时序逻辑电路的基本单元,也是最基本的时序电路。

同时也看一下锁存器的概念:

锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值。简单而言,锁存器的输入有数据信号和使能信号,当处于使能状态时,输出随着输入变化而变化,当不处于使能状态时,输入信号怎么变化都不会影响输出。

双稳态电路的特点是:在没有外来触发信号的作用下,电路始终处于原来的稳定状态。在外加输入触发信号作用下,双稳态电路从一个稳定状态翻转到另一个稳定状态。由于它具有两个稳定状态,故称为双稳态电路。

组合逻辑电路的基本单元是门电路。时序逻辑电路的基本单元是触发器。门电路某一时刻的输出信号完全取决于该时刻的输入信号,无记忆功能。触发器具有记忆功能,能够在无信号的情况下,保持上一次的信号。

二、触发器的分类及原理

触发器可以按照逻辑功能、触发方式、电路结构、存储数据原理、构成触发器的基本器件进行分类,详细如下:

| 分类标准 | 触发器类型 |

|---|---|

| 逻辑功能 | RS触发器、D触发器、JK触发器、T/ T’触发器 |

| 触发方式 | 电平触发器、边沿触发器和主从(脉冲)触发器 |

| 电路结构 | 基本RS触发器(锁存器)和钟控触发器 |

| 存储数据原理 | 静态触发器和动态触发器 |

| 构成触发器的基本器件 | 双极型触发器和MOS型触发器 |

1.RS触发器

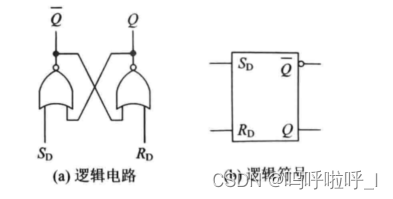

(1)与非门RS触发器

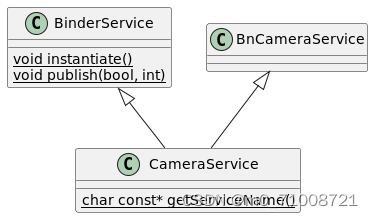

下图是用两个与非门构成的基本RS触发器,它具有两个互补的输出端Q和Q,一般用Q端的逻辑值来表示触发器的状态。

RS触发器的特征方程:

{ Q n + 1 = S ˉ + R Q R + S = 1 \left\{\begin{array}{l}Q^{n+1}=\bar{S}+RQ \\ R+S=1\end{array}\right. {Qn+1=Sˉ+RQR+S=1

各种输入情况下的输出:

| R | S | 输出 |

|---|---|---|

| 0 | 1 | 复位 |

| 1 | 0 | 置位 |

| 1 | 1 | 保持 |

| 0 | 0 | 禁止此输入 |

(2)或非门RS触发器

各种输入情况下的输出:

| R | S | 输出 |

|---|---|---|

| 0 | 1 | 置位 |

| 1 | 0 | 复位位 |

| 0 | 0 | 保持 |

| 1 | 1 | 禁止此输入 |

2.电平触发钟控触发器

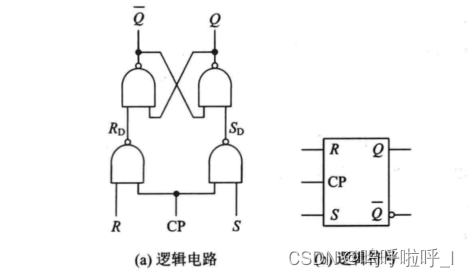

(1)钟控RS触发器

希望触发器在只有在时钟来临的时候才改变其输出状态,其他时候,触发器维持。钟控RS触发器如图所示,通过增加两个与非门构成了高电平触发的钟控触发器。当CP=0时,Rp=Sp=1,触发器处于保持状态﹔只有在CP=1时,触发器的状态才可能发生变化。钟控RS触发器的电路图如下:

特征方程:

{ Q n + 1 = R + S ˉ Q R S = 0 \left\{\begin{array}{l}Q^{n+1}=R+\bar{S}Q \\ RS=0\end{array}\right. {Qn+1=R+SˉQRS=0

各种输入情况下的输出:

| R | S | 输出 |

|---|---|---|

| 0 | 1 | 置位 |

| 1 | 0 | 复位 |

| 0 | 0 | 保持 |

| 1 | 1 | 禁止此输入 |

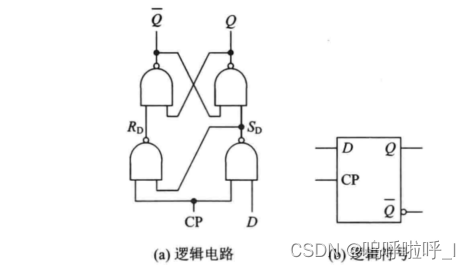

(2)D触发器

钟控D触发器的逻辑电路和逻辑符号分别如图所示。

当CP 为1时,R和S,互补,Sp=D,Rp=D。该触发器特征方程为

Q n + 1 = S ˉ D + R D Q = D + D Q = D Q^{n+1}=\bar{S}_D+R_DQ=D+DQ=D Qn+1=SˉD+RDQ=D+DQ=D

该触发器完成输人信号的保存,也称为数据锁存器,输入端D称为数据输入端。

各种输入情况下的输出:

| CP | D | 输出 |

|---|---|---|

| 0 | × | Q |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

注意,这里的D触发器是电平触发器。在时钟为高时,输出等于输入。

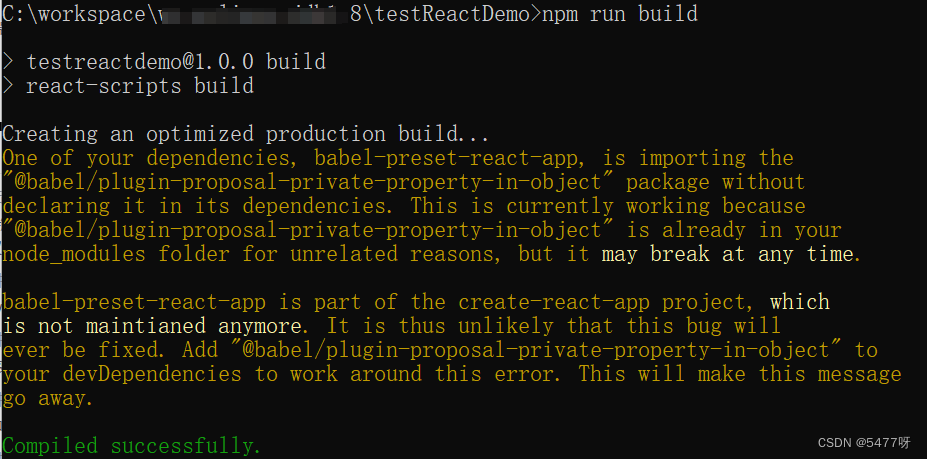

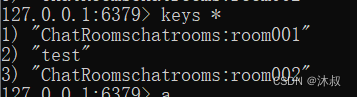

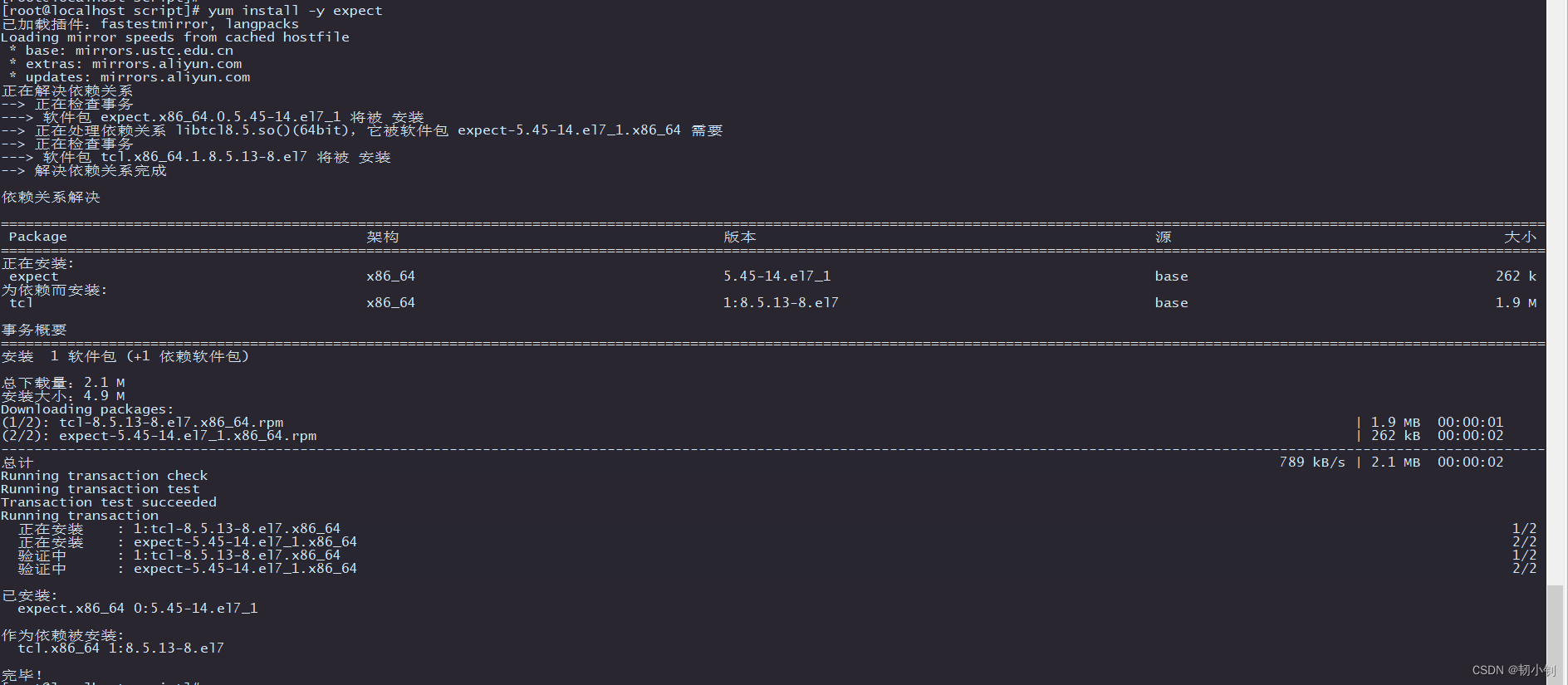

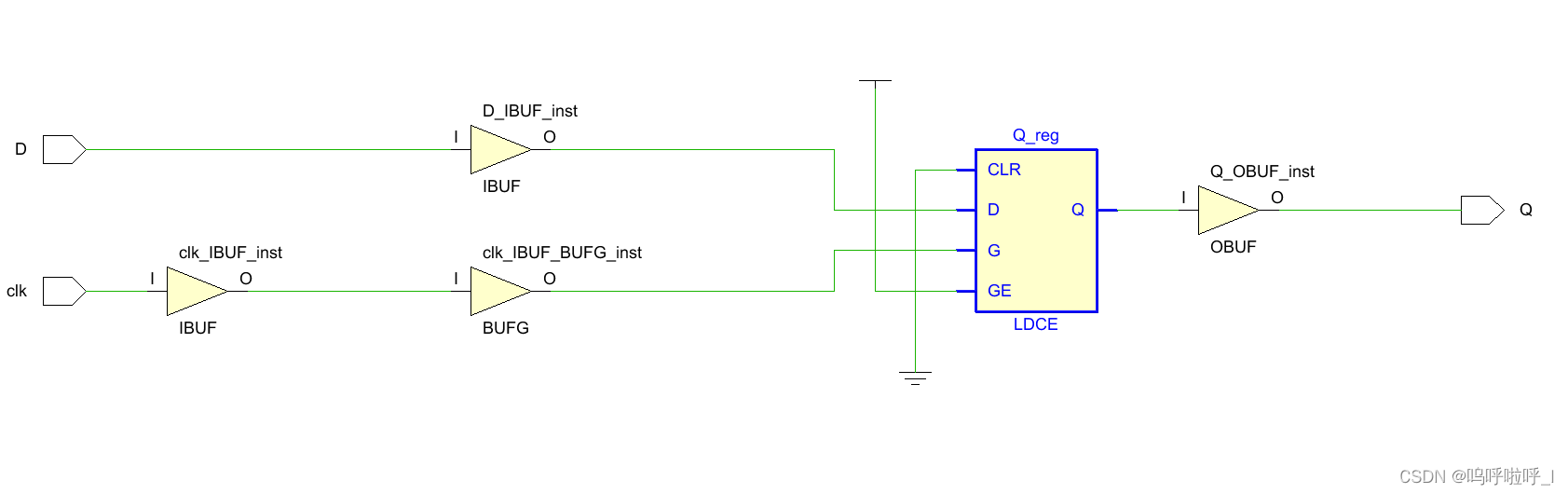

下面是钟控D触发器的Verilog及Vivado综合后的结果:

module D_FF(

input clk,

input D,

output reg Q

);

always@(clk)

begin

Q<=D;

end

endmodule

观察电路图我们其实可以发现,电平D触发器实际上就是D锁存器(实际上可以推广到所有的电平钟控触发器)。Vivado电路将其当作LATCH,边沿D触发器才是真正意义上的D触发器。因为从钟控D触发器的逻辑结构图我们可以发现,在时钟CP为1时,输出一样可以随着输入变化,这和锁存器是一样的。

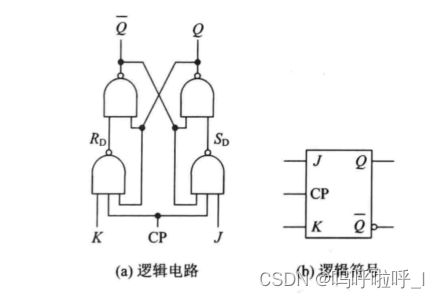

(3)钟控JK触发器

钟控JK触发器的逻辑电路和逻辑符号分别如图所示。

该触发器特征方程为

Q n + 1 = J Q ˉ + K ˉ Q Q^{n+1}=J\bar{Q}+\bar{K}Q Qn+1=JQˉ+KˉQ

该触发器完成输人信号的保存,也称为数据锁存器,输入端D称为数据输入端。

各种输入情况下的输出:

| CP | J | K | 输出 |

|---|---|---|---|

| 0 | × | × | Q |

| 1 | 0 | 0 | Q |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | ~Q |

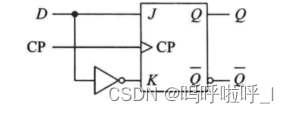

钟控JK触发器可以构建钟控D触发器,如图所示。

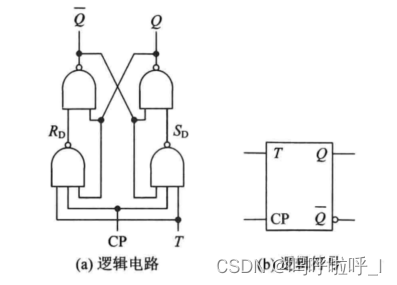

(4)钟控T触发器

将钟控JK触发器的J和K两个输入连接在一起构成钟控T触发器,它的逻辑电路和逻辑符号分别如图所示。

该触发器特征方程为

Q n + 1 = T 异或 Q Q^{n+1}=T异或Q Qn+1=T异或Q

各种输入情况下的输出:

| CP | T | 输出 |

|---|---|---|

| 0 | × | Q |

| 1 | 0 | Q |

| 1 | 1 | ~Q |

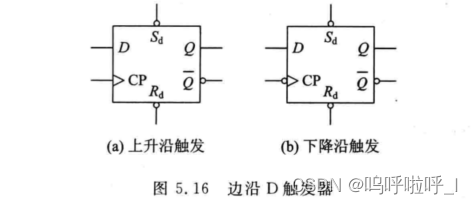

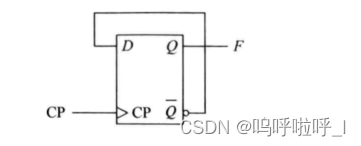

3.边沿触发器

(1)基本概念

在电平触发方式中,当触发电平有效时,当前输出状态作为现态参与触发器的次态计算。当次态出现后,如果触发电平仍有效,那么次态输出作为新一轮的现态再产生下一个新的次态(如T触发器若T在CP为1时一直为1)。电平触发方式可能使状态在约定电平期间发生多次翻转,也称为空翻。为了防止出现空翻现象,采用边沿触发器。边沿触发器仅在约定的电平边沿(上升沿或下降沿)到达时才可能发生状态变化﹔并且次态仅由该边沿变化瞬间的输入和状态决定;在非约定的边沿和电平期间,输人信号的变化不会引起状态的变化。

钟控触发器通常需要外部对其进行复位(输出变为0)或置位(输出变为1),所以实际的触发器通常有复位R和置位Sa,假定复位和置位信号均为低电平有效。图5.16为常用的边沿D触发器的逻辑符号。

(2)触发器的应用

可以用于设计二分频电路:

Verilog代码如下:

module FENPIN_2(

input clk,

input rst_n,

output reg Q

);

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

Q<=0;

else

Q<=~Q;

end

endmodule

波形图如下:

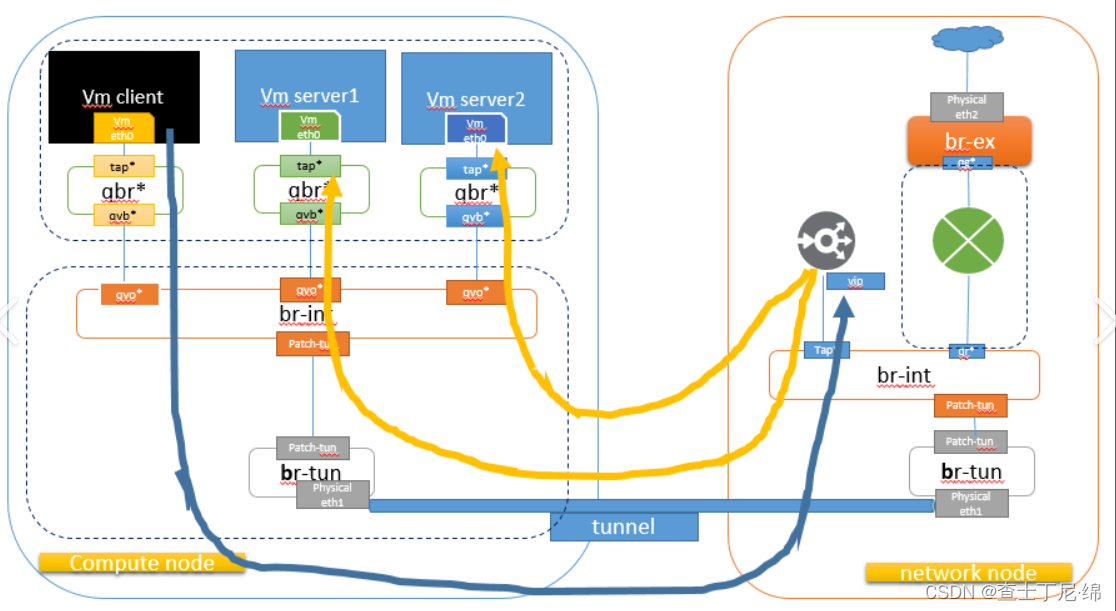

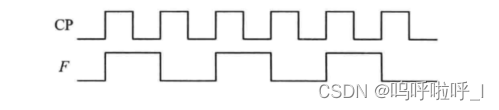

三、寄存器

1.基本结构

采用多个D触发器来构成一组保存二进制信息的电路称为寄存器。例如要保存n个数据可以采用n个触发条件相同的D触发器,有两种实现方式,一种是通过电平触发还有一种是通过边沿****触发**,其具体结构如下:

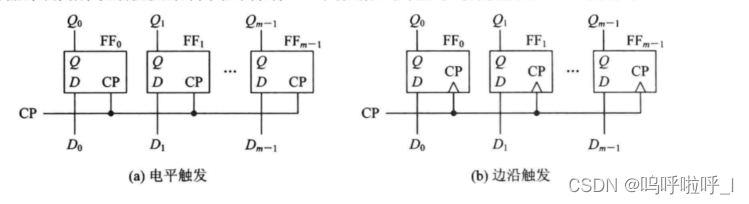

(1)电平触发数据寄存器

以74LS573(八D数据锁存器)举例,下图是其逻辑符号和内部结构:

其中,G为锁存信号;OE为输出使能﹔D0-D7为数据输入;Q0~Q7为三态数据输出。其只有在使能信号有效(低电平有效)并且锁存信号也同时有效(高电平有效)时才能够将输入数据映射到输出。之后当使能信号无效并且锁存信号为低时,将数据所存下来保持不变。详见下表:

| ~OE | G | D0…D7 | Q0~Q7(次态) |

|---|---|---|---|

| 1 | × | × | z…z |

| 0 | 1 | d0~d7 | d0~d7 |

| 0 | 0 | × | Q0~Q7 |

需要注意的是,当使能信号无效时,三态输出为高阻态。

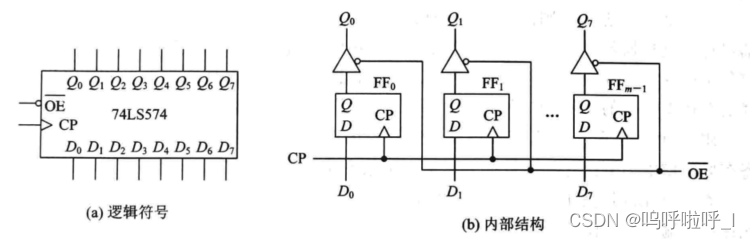

(2)边沿触发数据寄存器

以74LS574(八D触发器)举例,下图是其逻辑符号和内部结构。

只有当时钟上升沿到达并且使能信号有效时才会对数据进行更新,否则在使能信号有效的其他时刻对维持原有输出。详见下表:

| ~OE | G | D0…D7 | Q0~Q7(次态) |

|---|---|---|---|

| 1 | × | × | z…z |

| 0 | ↑ | d0~d7 | d0~d7 |

| 0 | 非↑ | × | Q0~Q7 |

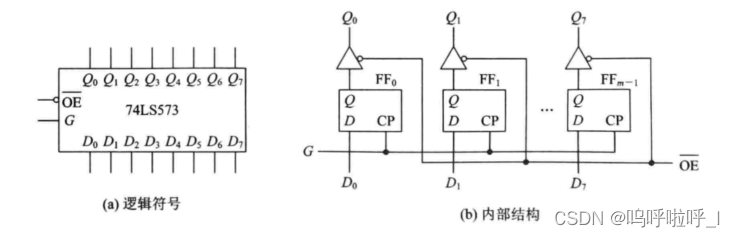

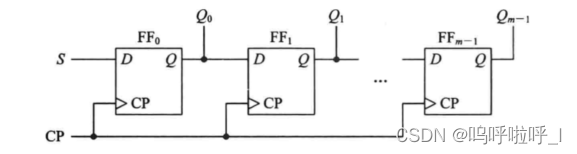

2.移位寄存器

(1)基本结构

若干个D触发器级联构成的触发器组成为移位寄存器,能够寄存串行的二进制信息。其结构如下图:

数据从S输入,每过一个时钟周期接收一位数据保存在D触发器内。

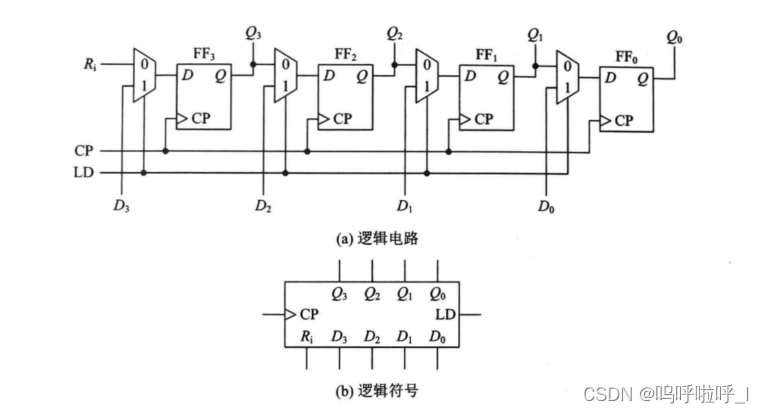

(2)可预置移位寄存器

将D触发器的数据输入端连接一个2选1数据选择器,两路数据为前级寄存器的输出和并行输入的一位数据,在原有功能的基础上还实现了对寄存器输出的置位。下图是其逻辑符号和内部结构:

当LD=0时,与基本移位寄存器的功能一致;

当LD=1时,寄存器的输出Q(次态)=D;

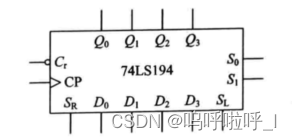

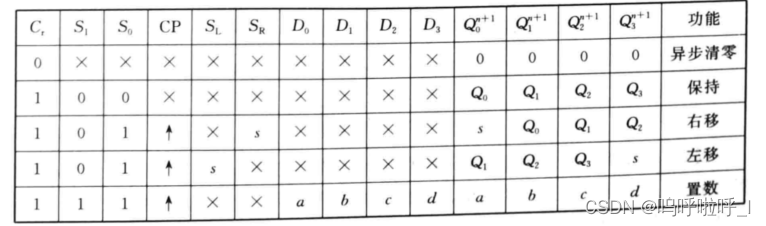

(3)四位通用移位寄存器74LS194

74LS194是四位通用移存器,具有左移、右移、并行置数、保持、清除等多种功能。其逻辑符号如图所示,其中,D0~D3是并行数据输入端;Cr是低电平有效的异步清零端;SR和SL分别是右移和左移的串行数码输入端;S1和S0是工作方式控制端,其组合00 为保持、01为右移、10为左移、11为置数。

其功能表如下:

注:图中左移时的S1S0标注错误,应为10

主要分为以下几点:

- Cr为0时,对输出进行复位

- Cr=1,S1S0=00时保持输出不变;

- Cr=1,S1S0=11时将输出置数为D0~D3;

- Cr=1,S1S0=01并且在时钟上升沿到来时进行右移

- Cr=1,S1S0=10并且在时钟上升沿到来时进行右移

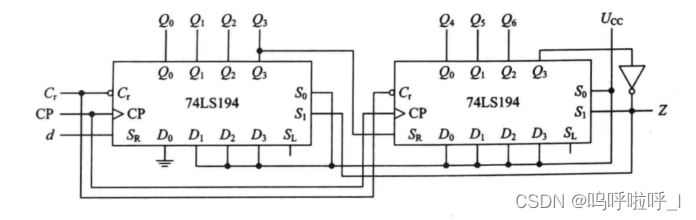

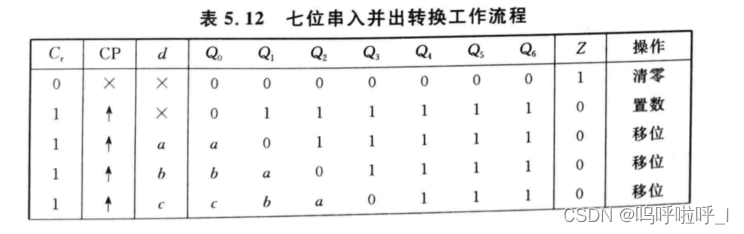

(4)利用移位寄存器实现串/并转换

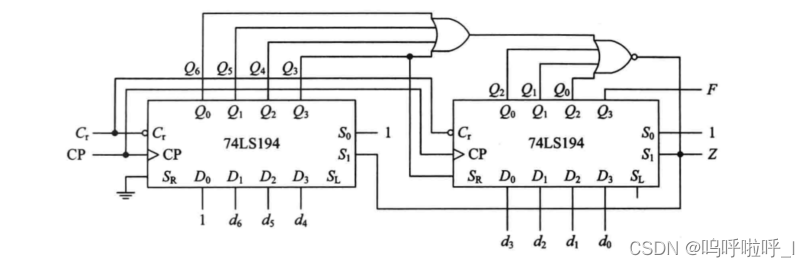

七位串并转换电路图如下:

Cr为初始清零信号;CP为移位时钟;d为串行数据输入;Q0~Q6为并行输出;Z为转换结束标志输出。

数据d6d0从数据输入端SR输入(假设d0先输入),并行数据从Q0Q6输出。D0接0作为标志,D1~D7接1。

工作流程如下图:

步骤如下:

- 复位:所有输出为0,Z为1

- 置数,数据输出为(0111_1111),其中Q7接非门到Z,Z变为0

- 上升沿到来输入数据开始右移,Q0输出d

- 一直右移直到之前置数的Q0的0右移到Q7(第8个时钟上升沿),此时Z变为1表示移位结束,而第一个输入数据“a”此时在Q6输出。

- 置数跳回到第二步

置数一定要有特殊位(只有一个1或一个0),才能有标志表示转换完成。

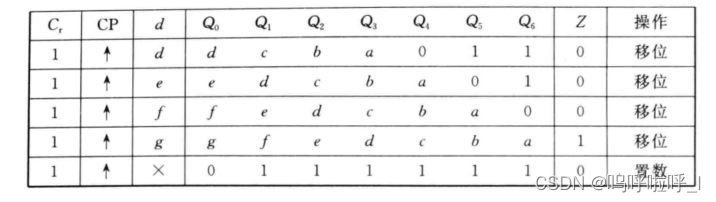

(5)利用移位寄存器实现并/串转换

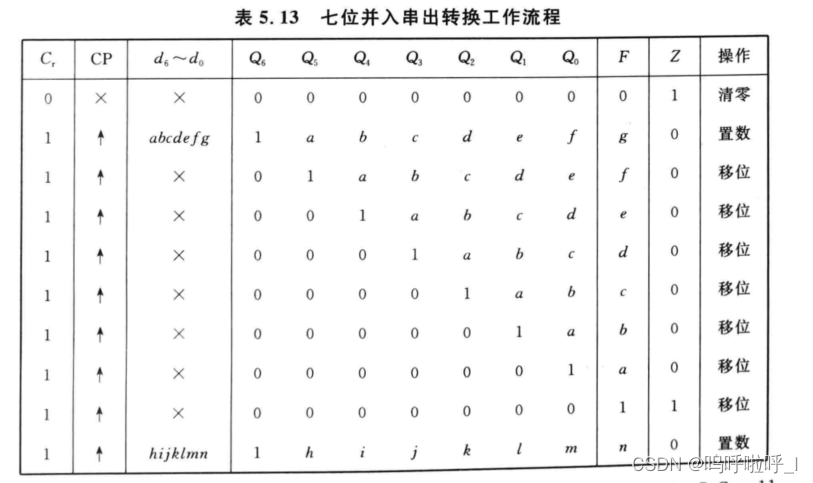

七位并转串电路如图所示:

并行数据d6~d0,从预置端输人,串行数据由F端输出,标志码1在74LS194的D0端。表5.13为七位并入串出的操作过程。

由于标志码在D0,之后的几拍会从Q0一拍一拍传递到Q2,在这个过程中因为或非门的存在Z一直会为0,知道标志位传递到Q7(第八拍)表示并串转换结束。

工作流程如下:

步骤如下:

- 复位:所有输出为0,Z为1

- 置数,数据输出为1abcdefg(对应结构图中从左到右的顺序),其中前7个数据的或非输入到Z,Z变为0

- 上升沿到来输入数据开始右移,F输出第八个数据口的数据(从左到右)

- 一直右移直到之前置数的Q0的1右移到第八个数据口(第8个时钟上升沿),此时前期个输出全部变为0,或非后结果为1,Z变为1表示移位结束。

- 置数跳回到第二步